回路設計

はじめに

今回は回路設計に関して簡単に書いていこうと思います。まだ全体の話を読んでいない方はこちらを先に読んでいただければと思います。

分野わけ

まずは簡単に分野を大きく2つに分けます。両方を跨ぐ設計もありますがそこはご了承ください。そこは本当の専門家がどこかで話してくれるかと思います。

Digital設計

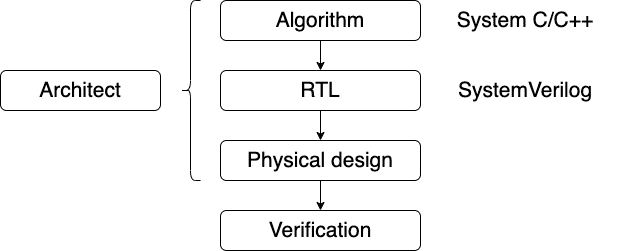

アルゴリズム設計、RTL記述、物理設計を含みます。昔の言い方で言うとLogic屋さんです。現在ではSystem C/C++等でアルゴリズ設計するとツールからRTLが生成されて、そのRTLから直で物理設計が完成するという流れができています。かなり抽象化されたアルゴリズムからも職人が作ったような物理設計ができるようになっており、かなり面白い分野です。

一昔前だと、アルゴリズム部分とRTL部分が分離されておりRTLはVHDLやVerilog/System Verilog等を使用して記述するのが一般的でした。

Digital設計はLayoutツール等で自分でトランジスタを書くという作業はほぼなく、プログラミング作業が大半になるかと思います。

Analog設計

SPICEと言われるSimulatorを使用してトランジスタレベルで回路を設計します。回路設計が終了するとLayout editorを使用して実際のLayout作業も含まれます。トランジスタレベルでSimulationおよび物理設計をするため、電子回路の知識(OPアンプ等)が必須です。例えばAnalog-Digital変換器や、アンプ回路設計等はこの分野になります。

基礎的なトランジスタの知識があると回路の設計最適化や特性向上に役たつと思います。よく言われるのがLayout作業はかなり美的センスが問われます。美しく描くと美しく動くとまで言われます。実際にそうなるのが怖いですが・・・。

Digital設計

最近話題となっているAI開発に必要不可欠なGPUは、このDigital設計の分野に入ります。もう少し詳しく掘り下げてみたいと思います。専門家では無いのであくまで自分が知っている範囲の情報です。

Architect

Digital設計におけるTop Level設計の分野になります。仕様をどのようにするかを明確にします。またData幅や大まかなDataの流れや処理方法に関して仕様を明確にしてSystem全体を定義します。そのため全体的な整合性を調整したりする能力が必要になります。これがGPUやCPUの様な大規模なものになると、パイプラインやキャッシュをどうするなどの話も入ってくるので天才エンジニアがこの仕事を請け負うことになります。

Algorithm/RTL

Architectが全体に関する仕様を決めるので、その仕様にあるように個々のブロックのAlgorithmを決めます。最近だとSystem C/C++でアルゴリズムを記述しRTL生成する方法が主流かと思います。少し前だとAlgorithmを作成し検証が終わるとそのアルゴリズムを参照しながらSystem VerilogでRTLで記述するのが一般的でした。その場合、アルゴリズムでは明示されていない部分も解釈しRTLを記述するという職人技が必要でした。

Physical design/Verification

RTLが記述できると、それをコンパイルしてFPGAに書き込むことができます。FPGA上で実際に意図したような動作をしているかをVerificationします。このVerificationもかなり大変で実装した機能が意図したように動くかは必須で、それに加えて想定外の入力や指示が来た場合にそれがFailとして弾かれたり、通常動作に影響を与えず動作し続けるかなどの検証もします。かなり大変と聞いています。

検証が終わると、実際の物理レイアウトにする必要があります。最近は優秀なToolがあるので、RTLを入力すると自動で配置配線をしてくれます。ただ完璧では無いので、優先されるパラメータや規約などのパラメータを最適化しながら設計を詰めていきます。最悪の場合はManualで配置してLayout作業する場合もあります。

Analog設計

Analog信号を扱う部分の設計となります。Analog信号といってもかなり範囲が広くDC的な信号やRFのようはGHz領域を扱うAnalogもあります。さらに言うと昇圧や降圧を行うインバーター回路、Charge Pump回路、さらに言うとDigitalの要素も入ってくPLL回路もあります。ただ実際に行う作業は共通点が多く、全体の流れとしてはこのようになります。

SPICE

デバイス設計者が実際のデバイスからAnalog Simualtion用のSPICEパラメータを抽出します。そのSPICEモデルを使用してAnalog回路を設計します。SPICE Simulatorは各社から色々出ています。ただ共通しているのはSPICEモデルです。これはBSIM4等が有名です。SPICEモデルはトランジスタの電気特性を数式を用いて抽象化したもので、SPICE Simulatorは回路図をもとにNodeの電圧や電流を計算します。その計算結果を確認しながらトランジスタの配置やサイズ等を調整したり抵抗や容量を追加したり値を変えたりして仕様を満たすように回路を設計します。

Layout

SPICE simulatorを用いて回路設計が終了すると、次はこの回路情報をもとにLayoutをします。この時にToolによってはS-Cellが読み出されてたりしてLayoutがある程度自動化できます。ただ要求によってはLayoutをStandardなものよりもカスタマイズしたものがよかったりするので、それは回路設計者の技量が試されるとこにもなります。

Analog回路設計でよく言われるのは美しくLayoutすれば、美しく動くということです。何が言いたいかと言うと左右対称で、かつSimpleで見た目も美しいと寄生容量や抵抗値が最小化したり、それらがバランスよく分布したりするので特性自体も良くなるという格言です。

DRC/LVS/RCX

Simulationで確定させた回路図とLayout作業で実装した回路図が一致してるかを検証するのがLVSです。さらにそのLayoutがDRを違反していないのかを検証するのがDRCです。特にExcuseや特別な理由がない限りはこの2つは必ずPassしないといけません。その後、RCXで寄生容量、抵抗、またはインダクタンス成分を抽出してそれを回路図に反映させ、最後の検証をSPICE Simulatorで実施します。ここで特性未達だったり、マージンがない場合は回路図の修正やLayoutの修正を行い、同様な作業を繰り返して最適化していきます。

まとめ

かなりざっくりとまとめました。あくまで新入社員やこれから半導体を扱う人向けなので大まかな流れや内容がわかればと思っています。

アメリカSilicon Valley在住のエンジニアです。日本企業から突然アメリカ企業に転職して気が付いた事や知って役に立った事を書いています。