【第3回】M-KUBOSを動かしてみます

皆様こんにちは

さぁ、本日は準備したBlock DesignをM-KUBOSの設定に変更していきましょう!

![]()

前回土台になるBlock Designには『Zynq UltraScale+ MPSoC』を選択しました。

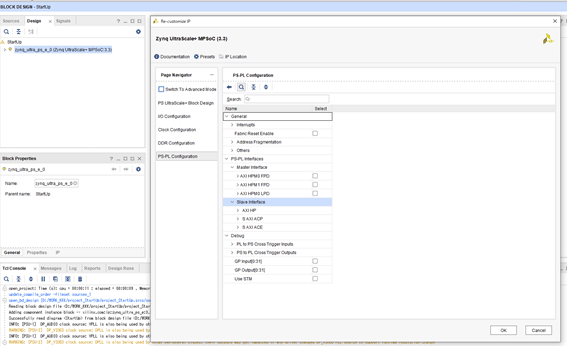

ここから『Re-customize IP』を開き各種Configurationを変更します。

今回、変更するのは

1.I/O Configuration

2.Clock Configuration 3.DDR Configuration

になります。

M-KUBOSのマル秘設計情報をもとに設定していきます。

となりにいる先輩からご指導いただきながら行いました~

I/O Configurationの変更です。

MIO Voltage Standard、各種peripheralの設定を、回路図を参考にして入力していきます。

面倒な作業ですね~~~

一度変更するたびに勝手にページスクロールしてしまうので

えっ!!どこを変えていたんだっけ???

と何度見失った事か。。。(汗)

と愚痴をこぼしていたのですが。。。

![]()

『M-KUBOS基本セット』がありました!

これら初期設定の済んだデザインが用意されています!! これがあれば、すぐに開発に取り掛かれるという製品です☆

別の機会にご紹介いたします~。

![]()

次にClock Configurationで クロックを設定します。

Input Clocks、Output Clocksを設定します

DDR Configurationの設定にはM-KUBOSに実装されているメモリのデータシートが必要になります。 メーカーの公開情報から取得します。今回は先輩が用意してくれました。

スピードグレードから該当箇所を見つけ出すのは大変ですね~。

こんな労力も『M-KUBOS基本セット』があれば。。。。

今回PL側には接続しないので

PS-PL Configurationでは全てチェックを外しました。

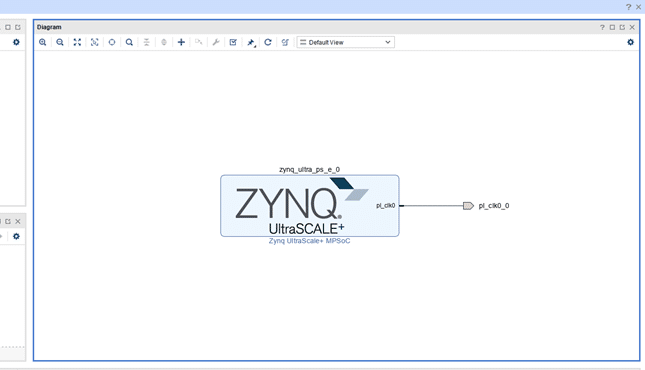

これで各Configuration設定はおしまい、

PLへクロックの信号を『Make External』で引き出しておきます。

以上で

M-KUBOSのBrock Designが出来上がりました!

最後に『Create HDL Wrapper』で上位層のコードを生成しておきます。

![]()

設定情報は回路図とメーカー公表のモノを使っていくので、自分で計算したりすることはありませんでした。FPGAの開発経験がなくてもわりとすんなり進めました。

次回は

ネットリスト、bitファイルの作成にチャレンジ!

M-KUBOSの詳細なご紹介は弊社Webページ(↓の画像をクリック) もしくはyuji_kakiki@paltek.co.jp にお問い合わせください。

#MPSOC #FPGA #やってみた #実験 #MKUBOS #xilinx #開発 #VIVADO #設定 #起動 #Config #IO

この記事が参加している募集

この記事が気に入ったらサポートをしてみませんか?