【第4回】M-KUBOSを動かしてみます

皆様こんにちは

今回はデザインソースを合成してネットリストを作成し、PL部に書き込むbitファイルを作成に挑戦します!

![]()

と、その前に

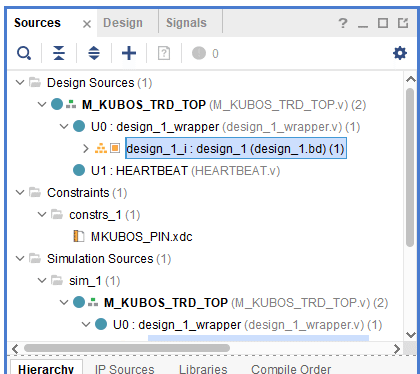

先輩に3つの追加ファイルを用意していただきました。

• TOPファイル:プロジェクトのTOP用

• Heart Beatファイル:LEDチカチカ

• M-KUBOSのConstrainファイル(制約ファイル):ピン情報等

です。

まずは、これらを前回作ったプロジェクトに入れていきます!!

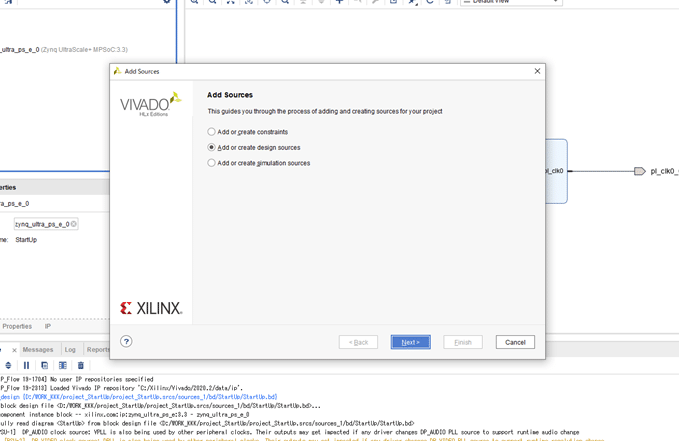

前回に引き続き、Vivadoを使って『Add Sources』でファイルを追加します。

HEARTBEAT.vとM_KUBOS_TRD_TOP.vファイルをソースに追加します。

さらに『Add Sources』でConstrainファイルのMKUBOS_PIN.xdcファイルを追加します。

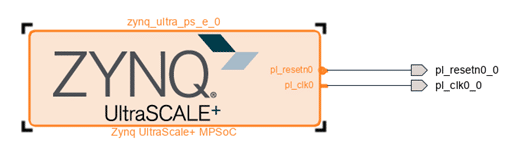

PLへのresetピンをTOPファイルで追加したので

『PS-PL Configuration』を変更してMake Externalで出力を追加します。

これで全てのソースがプロジェクトに揃いました。

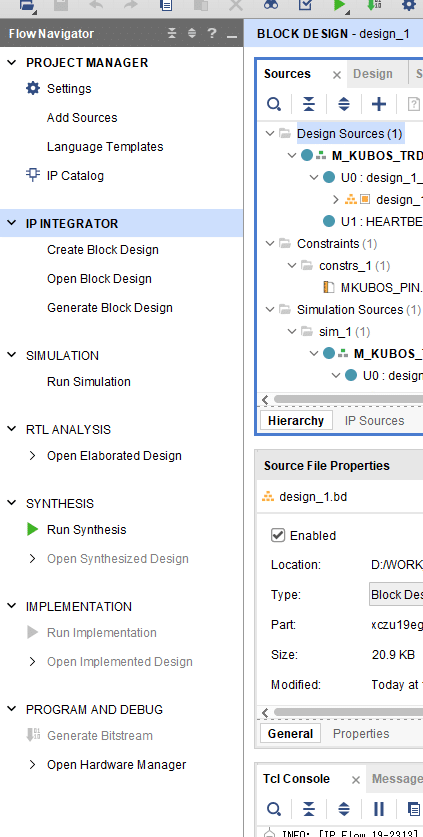

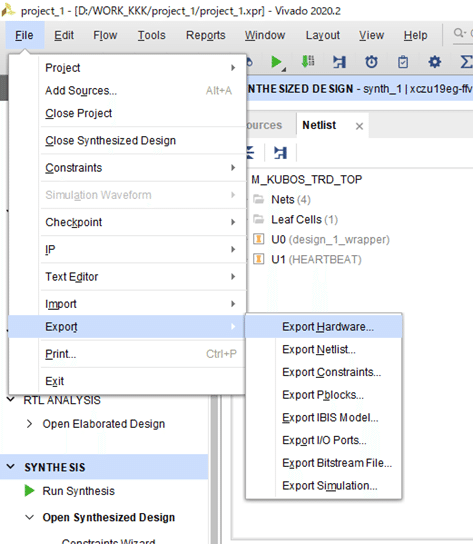

では次に、『Run synthesis』で論理合成します。

すると

ネットリストが生成されるんですね~。

そして、『Generate Bitstream』を実行すると

。

。。

。。。

出来ました!

M-KUBOSのハードウェア部分のbitファイルが生成されました☆

これで終わりと思っていたら

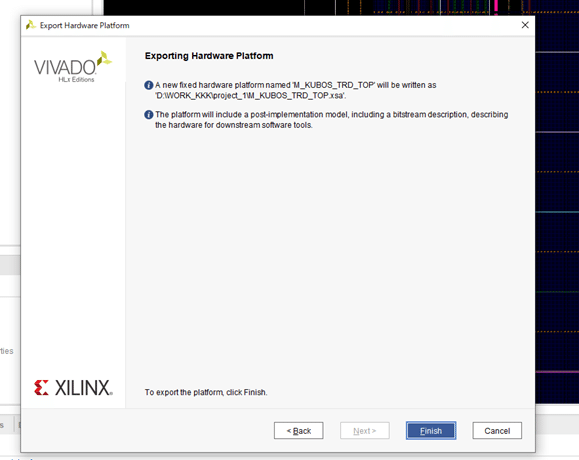

MPSoCではVIVADOで作成したハードウェアデザインをVITIS(またはSDK)にPS側プラットフォームとしてExportしなければならないとの事。。。

というわけで、本日、最後の一仕事!

従来のSDKの代わりとなる『VITIS』に作業を引き継ぐためにファイルを変換して出力します。

VIVADO 2020.2では出力先は『VITIS』に設定されているので『Export Hardware Platform』を『Include Bitstream』にチェックを入れて実行するだけで

じゃ~ん!!

M-KUBOSの『Hardware Platform』がXSAファイル形式で生成されました!! これをVITISに読み込ませます。

本日はここまで。

次回はVITISを使ってデモデザイン設計を仕上げて参ります。

![]()

M-KUBOSの詳細なご紹介は弊社Webページ(下記画像をクリック)もしくはyuji_kakiki@paltek.co.jpにお問い合わせください。

#MPSOC #FPGA #やってみた #実験 #MKUBOS #xilinx #開発 #VIVADO #設定 #起動 #ネットリスト #Synthesis #bitstream #Export