Device設計とは

はじめに

シリーズとして続けている記事の第三弾としてDevice設計の仕事内容を簡単に書いていきたいと思います。半導体エンジニアの簡単な役割や全体像に関して知りたい方はまずこちらの記事をご参照ください。

Device設計者の仕事全体像

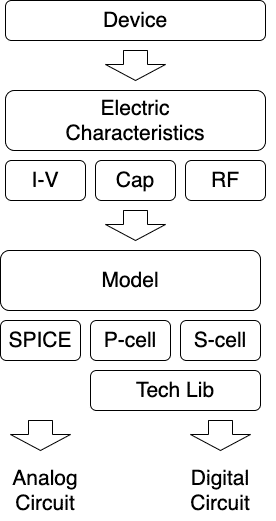

まずは全体像の把握からです。この分野の仕事は表にあまり出ないのでわからない部分が多くあるかと思います。自分もあまり詳しいくは把握しておりません。文献等で調べた範囲ですので間違いがあるかもしれませんが、大体はあっているかと思います。

流れとしては、プロセスインテグレーションで得られたデバイス特性を基に上位設計(回路設計)に繋げる架け橋を作る感じです。まだプロセスインテグレーションの部分を読んでいない方はこちらをご参照ください。

Electric characteristics

大抵の場合、新規技術開発時にDevice特性を抽出するために様々なテストパターンが入っています、TEGとかTestKey、またはWATと言われるものです。時には簡単な回路が入っていたりします。これらの電気的特性を取得してライブラリーを作成することが最初のStepとなります。

例えば、I-V特性取得や容量測定、適応分野によってはNoiseやRFの特性取得も行います。この時Fabが保証するであろうDeviceサイズを網羅することが重要です。

回路マージンを検証するために、コーナー特性の取得をする場合があります。この場合はプロセスインテグレーションエンジニアと協力してコーナー条件のデバイス試作をして特性取得を行います。

Model抽出

次に取得した特性を基に様々な回路設計用ライブラリーを作成します。モデルと言っても様々な種類があるので今回は代表的なものだけです。

SPICE :主にアナログ回路の設計に使用するものです

P-Cell :Primitive cellの略称。基本的な回路をひとまとまりとしています。インバーターなどですね

S-cell : Standard cellの略称。スタセルともいいます。Digital回路設計で使用する基本的なものを定義します。例えばANDやNANDやFFなどです。RTLからDigital回路を生成するときはこれらを呼び出して回路が作成されます

特にP-cellやS-cellはDesign KitやTechnology LibとしてまとめられてFabから提供されるものとなります。自前で作成するのはかなり稀です。

検証用Toolの開発

Device設計者が扱う仕事で、もう一つ重要な仕事はDRC等の検証用Toolのライブラリー開発です。プロセスインテグレーションエンジニアと協力して生産時に高歩留で安定して生産できるDesignをDocument化しそれを、検証ツールで使えるようにすることです。非常に重要な仕事ですが検証Toolを熟知してそれに対応するプログラム能力も必要となります。

Toolで使用するプログラムがかなりマイナーな言語だったり、記述にかなりの癖があったりするので勉強が大変です。

まとめ

今回はデバイス設計者に関してまとめました。自分もあまり専門では無いため詳しくは書けませんでした。

アメリカSilicon Valley在住のエンジニアです。日本企業から突然アメリカ企業に転職して気が付いた事や知って役に立った事を書いています。