Taiwan Semiconductor Manufacturing Company (TSM)24’2Q決算内容,Press Release,カンファレンスコール

昨日トランプさんの台湾防衛費負担発言から急落した半導体セクターですが、AHでは既に+2.4%と買い戻す動きが顕著です。

世界最大の半導体ファウンドリー企業として名実共に世界一に君臨する同社、否が応でも決算には世界中が注目します。

TSMCは事前に月次売上高を発表している為、売上高については予想をBeatする事がほぼ確実視されておりますがEPSや部門別売上、国別売上など細かい部分を見て行きたいと思います。

またTSMCは事前にCoWoSの値上げについて言及する記事が出ていたり、HPC(High Performance Computing)についても10%前後の値上げを示唆しております。

こういった点が来期以降のガイダンスにどう影響してくるのか、また2025年後半から量産化が噂されている2nmのウェハーについて何か記事があれば取り上げたいと思います。

今回の決算前に確認しておくポイントを別の記事にまとめて先に公開しておりますので、合わせてお読みいただければ理解も深まるかと思います。

※個別銘柄に言及する内容が含まれますが筆者の経験と知識を基に見解を述べているもので売買を推奨するものではありません。この先に進まれる方はこの件に同意されたものとみなさせていただきます。

24’2Q決算内容

Revenue 20.82B$(208億2000万$)Consensus 20.09B(200億9000万$)

Beat 0.73B(7億3000万$)Y/Y+34.9%

EPS nonGAAP 1.48$ Consensus 1.42$ Beat 0.06$

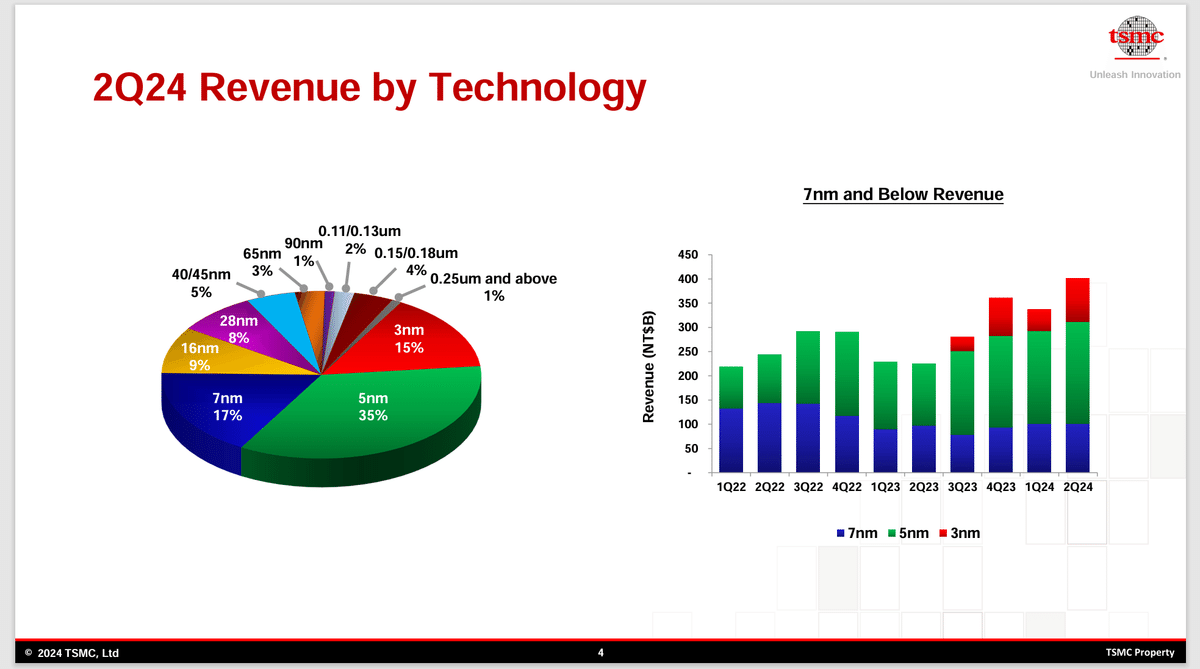

3nmウェハー比率 15%(1Qは9% +6%)

5nmウェハー比率 35%(1Qは37% -2%)

7nmウェハー比率 17%(1Qは19% -2%) 先端半導体比率計 67%

HPC(High Performance Computing)比率 52% Q/Q+28%

※主にデータセンター向け(NVIDIA、AMDなど)

Smart phone 比率 33% Q/Q-1%(Apple、Qualcommなど)

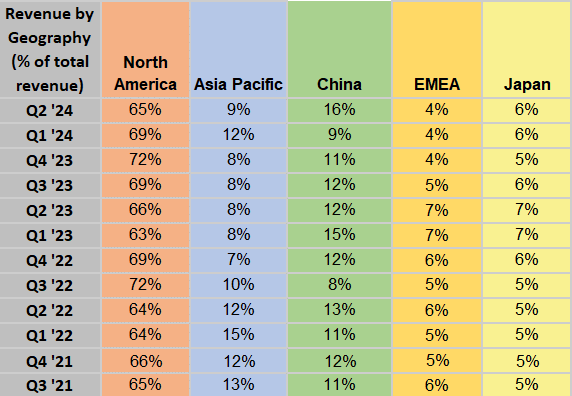

国別売上比率

北米 65%(1Qは69%)

中国 16%(1Qは9%)※近年で最大の売上比率

24’2Q財務状況

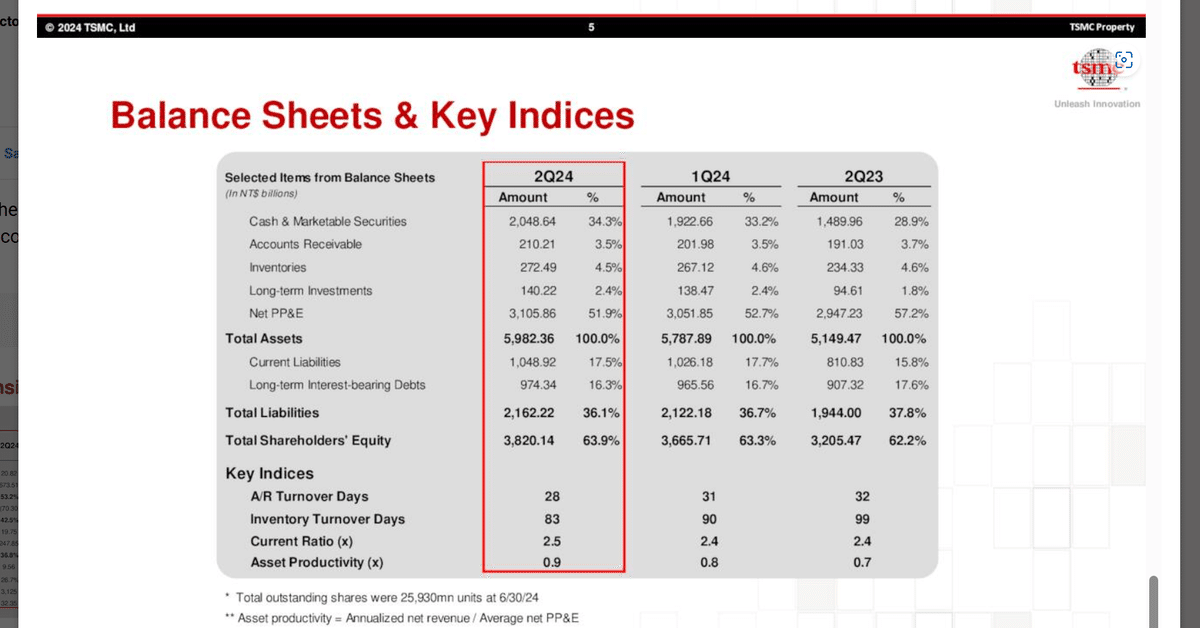

先端技術を追う形になる為どうしても研究開発費は毎期毎に増加傾向で、今後もこれは変わらないのではと思われます。営業コストもそれなりに増加しているのでこの表を見ると値上げはやむを得ない状況だという点が分かると思います。

前年同月比で売上高が+32.8%伸びても同時に営業コスト(Operating Expenses)も20.8%増加しており、設備増強や新工場建設コストもかなり掛る為見た目の数字だけでは読み取れない部分があります。

今年に入ってから営業キャッシュフローの堅調さが目立つ様になりました。同時にフリーキャッシュフローも昨年に比べ大幅に改善し、営業コストの増加分をうまく相殺できている様に思えます。

〈データセンター需要に支えられている為〉

今後新規契約分から3nm,5nmのウェハー価格の5%~10%値上げ、CoWoSやSolCと言った先進パッケージ技術の値上げが波及してくる為増え続ける設備投資にも柔軟に対応していけるのではと予想いたします。

24’3Qガイダンス、レポート

Wendell Huang - SVP, Finance & CFO

決算説明会で、AI関連の需要が高まる中、2024年の設備投資額の範囲を以前提示した280億~320億ドルから300億~320億ドルに縮小すると述べた。

資本予算のうち70%から80%は先端プロセス技術に、約10%から20%は特殊技術に、約10%は先端パッケージング、テスト、マスク製造などに充てられると黄社長は指摘した。

C.C.Wei会長兼最高経営責任者(CEO)は「2024年第3四半期に向けて、当社の最先端プロセス技術に対するスマートフォンやAI関連の旺盛な需要に支えられ、当社の事業が拡大すると予想している」と述べた。

魏氏は、メモリーを除く2024年の半導体市場全体が前年比約10%増となるとの見通しを維持した。〈ここは前回の決算とは違うコメントです、前回は半導体市場がマイナス成長すると懸念があると言っておりました〉

Wei氏によると、過去3ヵ月間、3ヵ月前と比較して、同社の顧客からAIとハイエンドスマートフォンの需要が見られ、2024年後半には3nmと5nmプロセス技術の全体的な稼働率向上につながるという。

TSMは引き続き、2024年が同社にとって好調な年になると予想している、と魏社長は付け加えた。

TSMは、2024年通年の売上高を米ドルベースで20%台半ばよりやや上方へ引き上げるとしており、4月の第1四半期決算説明会では20%台前半から中盤に引き上げるとしていた。

24’3Qガイダンス

Revenue EST 22.4B$~23.2B$(224億$~232億$)

Consensus 22.47B$(224億7000万$)Y/Y+35.8%

※経営陣がこれ以上明確なガイダンスを示していない為、カンファレンスコールの中でのコメントを抜粋するなどしてみるよう努めてみます。

カンファレンスコール

Wendell Huang - SVP, Finance & CFO

まず、24 年第 2 四半期と 24 年第 3 四半期の収益性についてお話しします。 第2四半期の売上総利益率は53.2%となり、ガイダンスの上限をわずかに上回りました。これは主に、3ヶ月前の予想に比べ、全体の稼働率が予想を上回ったためです。〈粗利率50%超えが標準化してきました〉

第3四半期の売上総利益率は1.3%ポイント上昇し、中間値で54.5%となる見通しです。

これは主に、第 3 四半期の全体的な稼働率の上昇と、生産性向上を含むコスト改善努力の成果によるもので すが、N3 の立ち上がりによる継続的な希薄化、N5 から N3 への工具変換コスト、および台湾の電力料金の高騰によっ て一部相殺されました。

我々がコントロールできない為替レートの影響を除外し、グローバルな製造拠点拡大計画による利益率への影響を考慮すると、長期的な売上総利益率53%以上は達成可能と引き続き予想している。

〈TSMCはこの粗利率が非常に重要な指標で、直近でようやく安定して50%を超えるようになってきました〉

次に、2024年の資本予算についてお話しします。

当社の設備投資は毎年、将来の成長を見込んで行われており、設備投資と生産能力計画は常に長期的な市場需要プロファイルに基づいています。

AI関連の旺盛な構造的需要が続くなか、私たちは顧客の成長をサポートするための投資を続けています。

2024年の資本予算の幅を、従来は280億~320億ドルであったのに対し、300億~320億ドルに絞り込んでいる。

資本予算の70%から80%は先端プロセス技術に割り当てられる。

〈TSMCは研究開発や設備投資に莫大な資金が掛かっております〉

約 10%~20%は特殊技術、約 10%は先端パッケージング、テスト、マスク製造、その他に使われる。 TSMCでは、設備投資の高水準は常に、次年度の成長機会の高さと相関している。

C. C. Wei - Vice Chairman & CEO

TSMCの使命は、今後何年にもわたり、世界のロジックIC業界にとって信頼される技術と生産能力を提供する企業になることです。

AI関連需要の継続的な急増は、エネルギー効率の高いコンピューティングに対する構造的な強い需要を支えています。

最も効率的でコスト効率の高い方法で最先端のプロセスおよびパッケージング技術を大規模に提供するTSMCに対する顧客の信頼が高まるにつれ、AIアプリケーションの重要な実現要素として、当社の技術的地位の価値が高まっています。

このように、TSMCは、AI、HPC、5Gという業界のメガトレンドに支えられた長期的な市場需要プロファイルの構造的増加に対処するために、規律ある枠組みを採用しています。

TSMCは顧客と緊密に連携して生産能力を計画しています。

また、トップダウン・アプローチとボトムアップ・アプローチの両方から市場の需要を評価・判断し、適切なキャパシティの構築を決定する、厳格かつロールアウト・システムを採用しています。

すなわち、テクノロジー・リーダーシップ、柔軟で迅速な製造、顧客の信頼の維持、そして持続可能で健全なリターンの獲得である。

投資から適切なリターンを得るためには、価格設定とコストの両方が重要です。 TSMCの価格戦略は、当社が提供する価値を反映するために、場当たり的ではなく戦略的なものです。

最後に、当社のN2の現状とA16の導入についてお話しします。

当社の2ナノメートルおよびA16テクノロジーは、エネルギー効率に優れたコンピューティングに対する飽くなきニーズへの対応において業界をリードしており、AIイノベーターのほとんどがTSMCと協業しています。

我々は、2 ナノメートル技術の最初の 2 年間における新規テープアウト数は、3 ナノメートルおよび 5 ナノメートル技術の最初の 2 年間を上回ると予想している。

N2 は、N3E と比較して、同じ電力で 10~15%の速度向上、または同じ速度で 25~30%の電力向上、15%以上のチップ密度向上を実現し、全負荷性能と電力の利点を提供する。〈決算前記事にて記載しております〉

N2技術の開発は順調に進んでおり、デバイスの性能と歩留まりは計画通り、あるいは計画を上回っている。 N2 は、N3 と同様の立ち上がりプロファイルで、2025 年の量産に向けて順調に進んでいます。

当社の継続的強化戦略により、N2ファミリーの拡張としてN2Pも導入する。 N2Pは、N2に比べ、同じ消費電力でさらに5%の性能向上、または同じ速度で5%から10%の消費電力削減を実現します。

N2PはスマートフォンとHPCアプリケーションの両方をサポートし、量産は2026年後半を予定している。〈これは初耳です〉

また、次のナノシート・ベース技術として、スーパー・パワー・レール(SPR)を特徴とするA16を別製品として発表します。

TSMCのSPRは、革新的でクラス最高の裏面電力供給ソリューションであり、ゲート密度とデバイスの柔軟性を維持するために、業界は別の裏面コンタクト方式を取り入れることを余儀なくされています。

N2Pと比較して、A16は同じ電力でさらに8%から10%の速度向上、または同じ速度で15%から20%の電力向上、さらに7%から10%のチップ密度向上を実現します。 A16は、複雑な信号経路と高密度の電力供給ネットワークを持つ特定のHPC製品に最適です。

量産は 2026 年後半を予定している。 N2、N2P、A16、およびその派生製品は、TSMCの技術的リーダーシップの地位をさらに拡大し、TSMCが将来にわたって成長機会を獲得することを可能にすると確信しています。

〈この先需要減速が起こらない限り、TSMCは伸び続けるでしょう〉

Gokul Hariharan - JPMorgan Chase & Co.(この方の質問)

今後4、5年間のCoWoSの生産能力について、年平均成長率60%、部品成長率60%というお話があったと思います。

では、来年もCoWoSの生産能力をどれくらい増強する予定なのか、少し話していただけますか?

C. C. Wei - Vice Chairman & CEO

需要が非常に高いので、顧客の需要を満たすために懸命に働かなければならない。 2025年か2026年には均衡を保てるようにしたい。

CAGR(年平均成長率)やCoWoS(コウォズ)のキャパシティーの増加について話しているのですね。 今となっては、そんなことは頭の片隅にもありません。 いつでも、どこでも、どんなことでも増やし続けるよ わかりました。 おそらく2025年まで

〈これが現状ですね・・・TSMCの生産キャパをもってしても追い付かない程物凄い需要だという事です〉

Brett Simpson - Arete Research Services(この方の質問)

AIチップメーカーは、特にバックサイド・パワーの問題から、Nマイナス1から最先端へと、より積極的に移行しようとしていると聞いています。

そこで質問ですが、あなたはこの動きを支持できますか?

もしそうなら、N2、A16は構造的に、過去数回のノードよりもはるかに大きなノードになると期待すべきでしょうか?

C. C. Wei - Vice Chairman & CEO

ブレット、君の言う通りだ。 人々は皆、電力効率の良いモードに移行したがっている。

そのため、消費電力を節約できるよう、より高度な技術を求めている。 私の顧客の多くは、N2、N2P、A16への移行を望んでいます。

私たちは、そのようなお客様をサポートできるよう、懸命に努力しています。 現在、少しタイトな状況ですが、少しどころではありません。

来年か2年後には、このような需要をサポートできるだけの生産能力を構築できることを願っている。 今日、そう、我々は彼らをサポートするために懸命に働いている。

Charles Shi - Needham(この方の質問)

CoWoSについてです。 CoWoSのキャパシティは2024年に2倍以上になると申し上げました。

2025年にはさらに倍増すると言ったと理解していいのでしょうか?

そして、顧客がCoWoS-SからCoWoS-LやCoWoS-Rソリューションに移行する際に、多くの技術的な課題や利点があることを知りたいと考えています。

それは容量の制約を緩和するのに役立ちますか? また、それによってCoWoSは2025年に需給バランスに達することができるのか?

※補足説明、CoWoSとは?:TSMCはCoWoS(Chip on Wafer on Substrate)という技術を使用しています。CoWoSは、半導体チップを基板に載せる技術のことです。この技術には複数のバージョンがあります。

顧客ごとに異なるニーズに応じて、TSMCは複数の技術バージョンを使い分けています。

生産能力を大幅に増強しており、これからもさらなる増強を計画しています。

各バージョンの技術に専用のツールが必要ですが、共通のツールも使って効率化を図っています。

C. C. Wei - Vice Chairman & CEO

チャールズ、君は本当に技術の詳細をすべて知っているね。 CoWoS-R、CoWoS-S、CoWoS-L。 こういったものはすべて、お客様の要求によるものです。 同じ顧客であっても、製品によってアプローチが異なるのです。

キャパシティを2倍にしたと言っても、これはCoWoSの一部、あるいは別のバージョンを合わせたものです。

どの部分が本当に2倍なのか、どの部分が他の部分よりずっと多いのか、これは私の顧客の需要に関係しているので、皆さんと共有するつもりはありません。 昨年から今年にかけて、私たちは2倍以上になりました。

そして申し上げたように、今年から来年にかけてはまた倍増したい、あるいはおそらく倍増以上にしたい。

CoWoSのバージョンが違えば、ツールセットも違ってくる。

しかし、共通したツールのいくつかはすべてのCoWoSで使うことができる。

Sunny Lin - UBS(この方の質問)

彼女はスマートフォンとPCに注目しています。 そこでまず、シリコンに含まれるユニット単位で、今後数年間のスマートフォンとPCの見通しを知りたがっています。

N5とN3の供給能力は非常にタイトです。 潜在的なユニットやアップグレードサイクルをサポートするのに十分なキャパシティがあるのでしょうか?

C. C. Wei - Vice Chairman & CEO

AIはとても難しい。 だから今、みんな......私の顧客はみんな、AI機能をエッジ・デバイスに搭載したがっている。

どの程度ですか? つまり、顧客から顧客への製品とは異なるということだ。 しかし、基本的には5%から10%のダイサイズの増加が一般的なルールになるでしょう。 台数の増加は、まだ見られない。

というのも、急に台数が伸びたわけではなく、このAI機能が需要の一部を刺激し、買い替えが短くなることを期待しているからです。

そのため、数年後、おそらく2年後には、スマートフォンやPCといったエッジ・デバイスの大幅な増加が見られるようになるでしょう

※補足説明、ダイサイズの増加とは?:ダイサイズの増加とは、半導体チップにおける回路部分の面積が大きくなることを意味します。

これはAI機能の追加によって必要な回路やトランジスタが増えるためです。これにより、エッジ・デバイスの性能が向上し、将来的にはデバイスの台数の増加が期待されます。

Arthur Lai - Macquarie(この方の質問)

エネルギー効率の高いコンピューティングは、間違いなく人類の目標です。 また、A16のキャパシティを拡大した場合、何が最大のボトルネックになると思いますか?

C. C. Wei - Vice Chairman & CEO

私たちはいつも、TSMCが生産能力を拡大しようとする場合、土地が必要であり、電気が必要であり、優秀な人材が必要であると言っています。

Brad Lin - Bank of America Merrill Lynch(この方の質問)

やはりAI関連のチップではダイサイズがどんどん大きくなっています。

そこで、先進的なパッケージング、特にファンアウト・パネルレベル・パッケージングについて質問します。

これはTSMCが検討していることなのでしょうか?

これはTSMCにとって中長期的なものになるのでしょうか?

C. C. Wei - Vice Chairman & CEO

はい。 私たちはこれをパネルレベルのファンアウト技術と考えています。 しかし、現在ではまだ成熟していませんので、私個人としては、少なくとも3年後だと考えています。

この3年の間に、ラジカル・サイズの10倍以上のダイ・サイズに対応する確かなソリューションはまだありません。

現在では、5倍、6倍のチップサイズまでサポートしています。 燃料サイズについてですが、最大の燃料サイズです。 その3年後には、パネルファンアウトが導入されると思います。

※補足説明、ファンアウト・パネルレベル・パッケージング(FOPLP)とは?

ファンアウト(Fan-Out)技術:

チップの周りに追加の配線領域を作り、配線を広げることで、より多くの入出力(I/O)端子を配置できます。

これにより、チップのI/O密度が向上し、パフォーマンスが向上します。

パネルレベル(Panel Level)技術:

従来のウェハーレベルパッケージング(WLP)では、シリコンウェハーの上でパッケージング工程を行いますが、パネルレベルパッケージングでは、より大きなパネル(ガラスやプラスチックなどの基板)上で行います。

パネルのサイズが大きいため、一度に多くのチップをパッケージングでき、生産効率が向上します。

ファンアウト・パネルレベル・パッケージング(FOPLP)は、先進的なパッケージング技術であり、チップの周りに追加の配線領域を作ることで性能を向上させる「ファンアウト」技術と、大型のパネル上で一度に多くのチップをパッケージングする「パネルレベル」技術を組み合わせたものです。

これにより、コスト効率、性能向上、薄型化が実現されます。TSMCも、この技術を中長期的な視点で検討しており、AI関連のチップの需要に応えるための重要な技術と位置づけています。

まとめ

一通りカンファレンスコールを読みましたのでまとめたいと思います。

TSMCを調べるときに一番多く目にする内容が地政学リスクです。

台湾が中国の支配下に置かれたら確かにチップの生産が止まり、TSMCはもちろんの事NVIDIA、Apple、Qualcommなどのファブレス企業の株価は暴落するでしょう。問題はこのリスクの発生度合いをどのレベルで見るかではないかと個人的に思います。

私自身はテールリスクの扱い(可能性はゼロではないがかなり低いレベルで見ており、避けようのないリスクである)として見ておりますので、それよりもこれだけの時価総額の企業がCAGR 20%で成長するという事の方が大きいです。

決算前記事や今回の決算記事を書くにあたり資料を読み込んでいた中で、CoWoSのキャパ成長率や顧客側(NVIDIAやApple)の要望に関しては知る事ができませんでした。それがこうやってカンファレンスコールの中で見つけられたりするので、改めて経営陣の直のコメントというのはその企業を理解するのにとても重要な点だなと感じました。

2nmウェハーやA16、更にはN2Pという新たな技術にも言及されており、N2とA16に関しては2025年下期より量産化開始、N2Pに関しては2026年下期より量産化開始を目指していると具体的に時期を指しておられました。

こういった点を見てもTSMCはNVIDIAのように代わりが効かない企業であり、世界的にシェアを取り続けて行く事が容易に想像できる様に思えます。

カンファレンスコールの中でウェイCEOが2022年の失敗は決して忘れないと仰っておりました。同じことを繰り返さない為にも懸命に働いているんだとも仰っており、この点を見てもTSMCの未来に明るいものを感じる次第です。投資家としての喜びはこういった世界一の企業が成長していく過程での恩恵を少なからず受けられる事ではないかと思う次第です。

今回色々と調べて勉強できたおかげで今まで知らなかったTSMCの側面を垣間見る事ができたかと思います。引き続きTSMCには注目し、今回のトランプさんの件で急落した所で買い増しをしたいと思います。

長くなってしまいましたが最後までお読みいただきありがとうございました。