アセンブラ命令順序の最適化|行列積高速化#19

この記事は、以下の記事を分割したものです。

[元の記事]行列積計算を高速化してみる

一括で読みたい場合は、元の記事をご覧ください。

次に、各演算器の停止時間を最小化するために、5つの演算器を同時使用できる命令順序への変更を考えます。

今回のプログラムでは、FMA計算・ロード処理・詰め替え処理の3つを行っています。Skylake マイクロアーキテクチャでは、FMA計算は2つの演算器(port0, port1)、ロード処理も2つの演算器(port2, port3)、詰め替え処理は1つの演算器(port5)で実行されます。FMA計算の時間が浮動小数演算の時間=FLOPSになるため、port0とport1がなるべく停止しないようにする必要があります。

19-1. 最適な命令順序の設計

まず、レジスタの依存関係を考慮せずに、理想的な命令順序を考えます。ブロードキャスト命令のレイテンシーが不明なので、L1キャッシュからのデータ転送時間4サイクルを最小値として、ここでは4〜6サイクルで考えることにします。

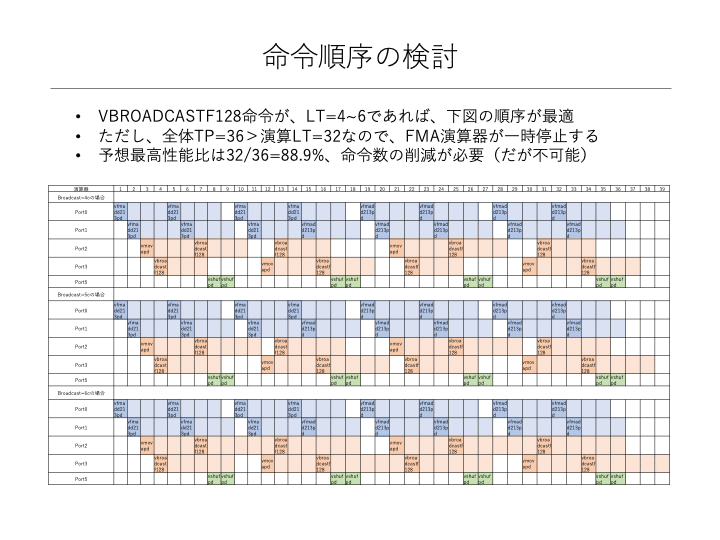

今回の命令群の理想的な順序を検討した結果は下記になります。

この図では、濃い色はスループット(TP)を表し、薄い色はレイテンシー(LT)を表しています。今回使用している命令は、スループット時間は全て1以下なので、TPは全て1サイクルとして扱っています。1未満の場合は、複数演算器で同時実行が可能なことを示しています。また、基本的に命令発行は1つずつ行われ、同時発行はできないものとしています。そのため、命令発行タイミングを表すTP(濃い色)の部分は、1サイクルにつき必ず1つになるようにしています。

検討手順は、次のように行いました。

(1)FMA計算(青色)を埋める

(2)FMA計算の待ち(薄い青色)のときに、ロード処理(オレンジ)を挿入する

(3)FMA計算もロード処理も待ち(薄い青・オレンジ)のとき、詰め替え処理(緑)を挿入する

(4)命令発行タイミングが重ならないように、FMA計算に隙間を開ける

検討の結果、どうしてもFMA計算が止まるタイミングがあることが分かりました。

これは、命令数に比例する総スループット時間が36サイクルなのに対して、FMA計算の総レイテンシー時間が32サイクルと少ないためです。結果として、このアルゴリズムの最高性能は32/36=88.9%あたりだろうと推測できます。

このことから、100%の性能を出すには命令数の削減が必要になります。しかし、今のところ命令数を削減できる見込みはありません。

具体的な実現方法については、有料にさせていただきます。

次の記事

ここから先は

¥ 100

この記事が気に入ったらサポートをしてみませんか?