LTspiceでアナログCMOS集積回路をバイポーラTRと比較しながら体験する

最初にバイポーラトランジスタのアナログ集積回路を習得した設計者にとってCMOSプロセスのアナログ集積回路はプロセス依存度が高く設計しにくいイメージがあります。

そこで、バイポーラトランジスタ回路と比較しながらCMOS的なアナログ回路を設計してみます。アナログCMOS回路の基本回路動作を理解しながら最終的には「Image Rejection Mixer」を設計してアナログCMOS集積回路を体験したいと思います。

「spice」や「アナログ集積回路」の初心者でもわかりやすいように実際の動作をLTspice上で体験しながら理解していただけたら幸いです。

LTspiceのシミュレーションで動作確認するので、最初に使用するCMOSプロセスのNMOSとPMOSのSPICEパラメータ、比較用のトランジスタのSPICEパラメータを準備する必要があります。

(以下、部品登録に関して色々と書いてありますが、指定したフォルダに添付ファイルを保存すれば、集積回路の動作確認はできます)

■集積回路バイポーラTR SPICEパラメータ

データ保存フォルダの設定

今回、新たに使うデータなどは以下のフォルダに保存する前提で説明したいと思います。

[新規SPICEのデータ]

C:\Users\xxxxx\Documents\LTspiceXVII\lib\sub\mylib

(フォルダ名「mylib」は新規作成で追加)

データを有効にするためにコマンド

「.lib mylib/TEG.lib」「.include mylib/TEG.lib」などを忘れずに!

[新規に作成した部品のシンボル]

C:\Users\xxxxx\Documents\LTspiceXVII\lib\sym\AutoGenerated

最初に集積回路用バイポーラトランジスタのパラメータを登録しますが、メーカーからは入手困難なので、ネットから簡単に入手可能な汎用トランジスタのSPICEパラメータを少し変更して代用することにします。

ディスクリート用と集積回路用の大きな違いはトランジスタ1個当たりの扱える電流値が違うと言うことなので、トランジスタ2SC1815と2SA1015のそれぞれのSPICEデータを基に

Vaf/Bf/IKf/Cjc/Cje

の値を変更してファイル名をTEG.libとして保存します。この時、トランジスタ名を2SC1815→TNPN、2SA1015→TPNPに変更します。

.model TNPN NPN(Is=2.04E-15 Xti=3 Eg=1.11 Vaf=50 Bf=120

・・・・・・・・・・・・・・・・・・・・・・・・Itf=0 Vtf=0 Xtf=0).model TPNP PNP(Is=295.1E-18 Xti=3 Eg=1.11 Vaf=50 Bf=60

・・・・・・・・・・・・・・・・・・・・・・・・Itf=0 Vtf=0 Xtf=0)バイポーラ集積回路は比較対象のための参考程度なのでこの程度の変更で集積回路の雰囲気は再現できると思います。

登録した部品を使用するときは普通にトランジスタシンボルを選択し、手動でモデル名をTNPN,TPNPのように書き換えます。

実際にDCシミュレーションしてみましょう。Vaf/Bf/Ikfを変更した影響がグラフに出ています。

Vafを変更したためアーリー効果の影響(下段グラフ)が見えていますし、Bfの大電流時の落ち込む位置(上段グラフ)はIkfの変更で確認できます。

Bfのピーク値はVafの設定値にも影響を受けるようでVafを小さくするとBfは設定値よりも少し高くなるようです。

■集積回路用MOSFET SPICEパラメータ

SPICEデータのダウンロード

大学の講座等で公開しているデータを基に少しパラメータ変更をして使用したいと思います。

https://people.rit.edu/lffeee/CD4007_SPICE_MODEL.pdf

https://cmosedu.com/jbaker/courses/ee420L/s15/students/lej6/Project/CD4007.txt

https://cmosedu.com/cmos1/cmosedu_models.txt

https://nano-lsi.iis.u-tokyo.ac.jp/Lecture_notes/CMOS180.lib

一番最初の場所からCD4007のSPICEパラメータが入手できたので、TEG.libファイルに追加して保存後、LTspice上で上手く動作してくれるか先ずは確認します。

SPICEデータとシンボルの設定方法

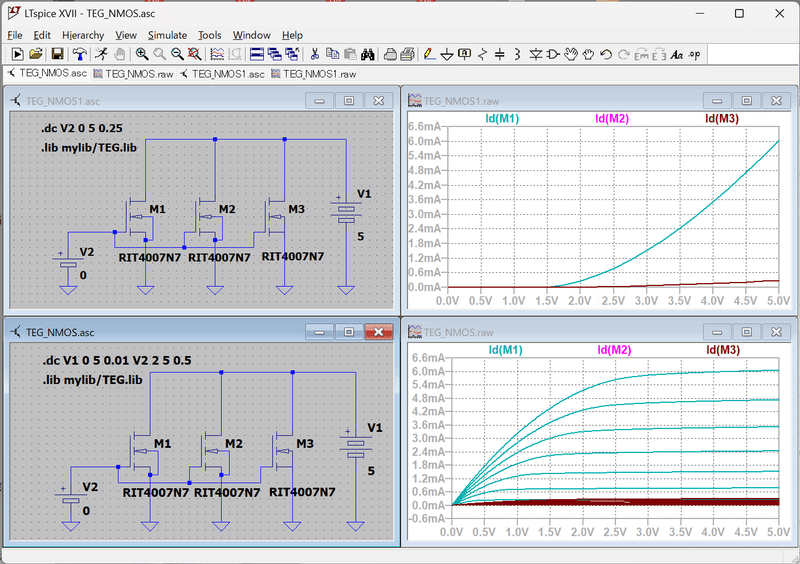

MOSシンボルにはNMOS、NMOS4、PMOS、PMOS4がありますが、先ずは3端子のNMOS、4端子のNMOS4のシンボルを使って動作確認をしてみましょう(但し、4端子のサブストレートはソースと結合して3端子FETとして使用)。

図に於いてM1とM2は4端子のNMOS4シンボル、M3は3端子のNMOSシンボルです。

M2とM3は完全に一致した特性ですが、M1だけは特性が違います。実際のCD4007の特性に近いのはM1のNMOS4シンボルです。

M1とM2(=M3)の違いはそれぞれのFETシンボル上で右クリックするとわかります。M1では入手したSPICEデータではコメント化されていた値を入力しました。

ここから先は

¥ 490

最後まで読んでいただいて有難うございます。 コメントは今後の参考に、フォローやサポートは今後の励みになります。