【Icarus】Verilog開発環境構築【Visual Studio code】

2020/05/18記

今回のnoteはハードウェア記述言語(HDL)の一種であるVerilogを自分のPCで動かすまでの記録です。

HDLとはハードウェアの設計をプログラミング言語のように記述することができるものです。

Verilogでは主にデジタル回路の設計と検証を行うために用いるそうです。

私の場合、今後の業務で使うそうなのですが今のところ完全にド素人なので、自習用に私用PCに開発環境を構築します。

参考サイトは各見出しごとに記載しています。

PCの環境と使用ソフトウェア

OS:Windows 10 Home(×64)

Verilogシミュレータ:Icarus Verilog Simulator (v11-20190809-x64)

波形表示ソフト:GTKWave (Icarusに同梱されてる)

http://bleyer.org/icarus/

エディター:Visual Studio Code

Icarus Verilogをインストール

公式サイトよりiverilog-v11-20190809-x64_setup.exe [17.0MB]をダウンロードし、インストール。

インストール時の注意

① PATH変数の設定(Add executable folder(s) to the user PATH)にチェックが入っていることを確認、チェック外さないで。

② インストール場所のディレクトリ名に日本語やスペースが入っていないように。(Cドライブの直下などがオススメ)

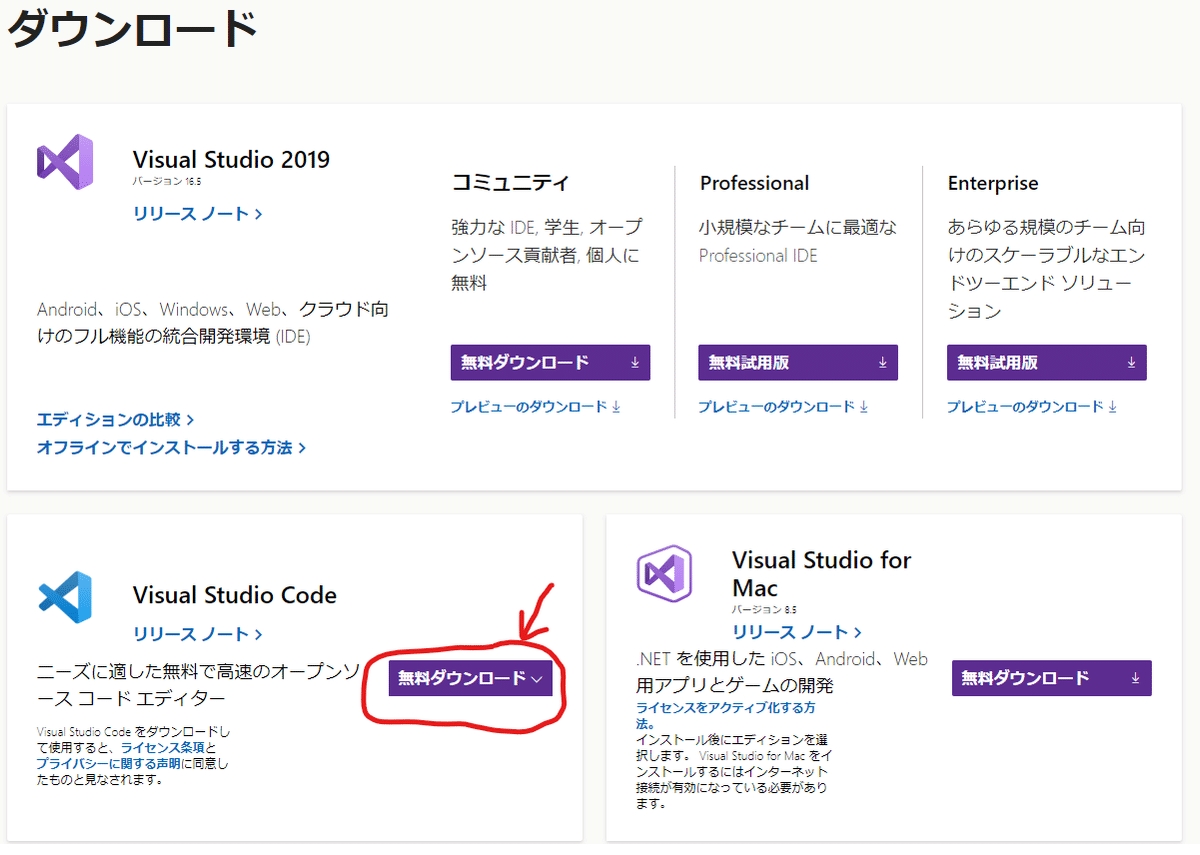

Visual Studio code(VSc)をインストール

公式サイトよりダウンロードし、インストール。

Fig.1 Visual Studio Code をダウンロード

表示に従ってインストールをする。

日本語化する(VSc)

Fig.2 英語無理!まずは日本語化しよう

1. Visual Studioを開く

2. [View]→[Command Palette...]を選択 (Fig.2)

3. 検索に[configure display language]と入力し、選択

4. 左の拡張機能一覧から[Japanese Language Pack for Visual Studio Code]を選択し[install] (Fig.3)

5. インストールが完了したら[Restart Now]を選択し再起動

日本語化完了

Fig.3 日本語化拡張機能が用意されている

Verilog用拡張機能をVScへインストールする

1. 起動画面の左側タブ一番下[拡張機能](□が4つ並んだアイコン)を選択

2. 検索窓に「Verilog」と入力し、[Verilog HDL/System Verilog]をインストール

Fig.4 Verilog用拡張機能のインストール

色分け表示させる

[ファイル]→[新規ファイル]を選択して新規ファイルを作成

エディタに試しにサンプルコードをコピペしてみた(Fig.5)

Fig.5 試しに作成したファイルにサンプルコードをペースト

当然、この時点では何の言語かも指定していないので色分けなどはなされていない。

ここで作成したファイルを保存する際に[ファイルの種類]を「Verilog(*.v,*.vh,*.vl)」を選択すればちゃんと色分けなどが反映される。(Fig.6)

Fig.6 色分けが反映された

コードを作成する

学習用に参考にさせて頂いているこちらのサイトの[問題5]のコードを使っていく。(本noteでは動かす方法だけ書く。)

尚同名の変数やファイル名で混乱したので、一部改変した。

▼ 10進カウンタのコード(ファイル名:10counter.v)

module counter(CLK, RES, Q);

input CLK, RES;

output [3:0]Q;

wire CLK, RES;

reg [3:0]Q;

always @(posedge CLK or negedge RES)

if(RES ==1'b0)

Q = 4'd0;

else if(Q == 4'd9)

Q = 4'd0;

else

Q = Q + 4'd1;

endmodule

▼ テスト・ベンチ(ファイル名:10counter_test.v)

module counter_test;

reg CLK, RES;

wire [3:0] Q;

counter10 i0(CLK, RES, Q);

always #5 CLK = ~CLK;

initial begin

CLK = 0;

RES = 0; #23 RES = 1; #150 $finish;

end

initial begin

$monitor("CLK=%d, RES=%d, Q=%d", CLK, RES, Q);

$dumpfile("counter.vcd");

$dumpvars(0, counter_test);

end

endmodule上記2ファイルを一つのフォルダに保存した。

実行のためにディレクトリを指定することになるので、フォルダ名やファイル名すべてに日本語が入らないようにしましょう。

よくわからなければ、とりあえず分かるようになるまでCドライブの直下に作ったフォルダにでもぶち込めばOK。たぶん。

シミュレーションの実行と波形表示

▼ ターミナルを開く

1.[ターミナル]→[新しいターミナル]を選択

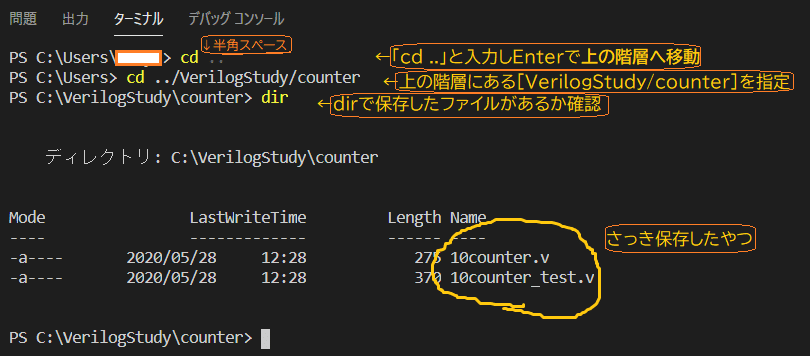

2.画面下にターミナルが表示される(Fig.7)

自分の環境の初期状態は、個人ユーザーのフォルダが指定されていた。

(C:\Users\ユーザー名)

Fig.7 ターミナルの開き方

(本当に詳しいことはコマンドプロンプトのコマンドを調べてください。)

▼ 使うコマンド

cd (ディレクトリ名) :ディレクトリの移動(相対パスで書く)

../ :ディレクトリを指定する際、上の階層へ移動

dir :指定しているディレクトリにあるファイルやフォルダを一覧表示

さっき作ったVerilogファイルは

Cドライブ \ VerilogStudy \ counter

というフォルダの中に保存したので、コマンドを使ってこのディレクトリを指定する。

▼ディレクトリの指定

1.『cd ../../VerilogStudy/counter』と入力しEnter(cdの後ろは半角スペース)

2.『dir』と入力しEnterを押し、先ほど保存したファイルがあることを確認

Fig.8 カレントディレクトリの移動(一気に指定しても順々に指定してもOK)

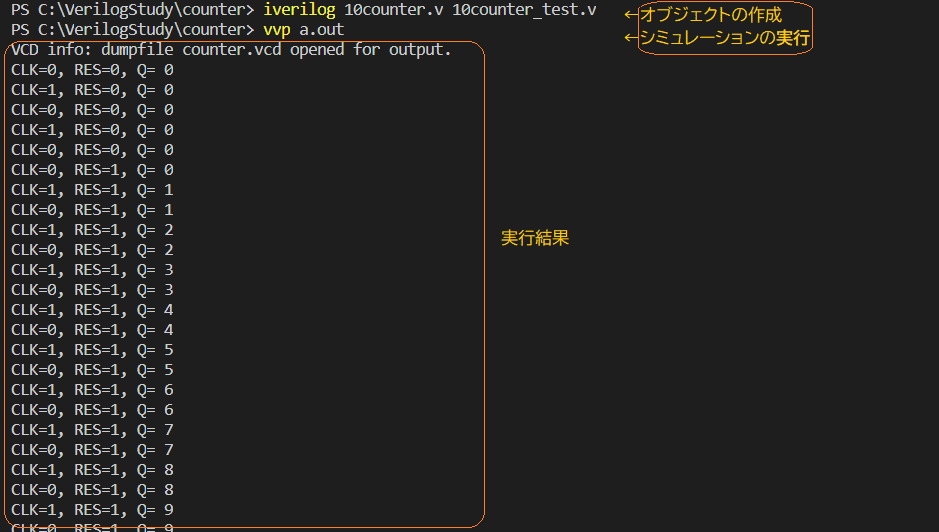

▼シミュレーションの実行

1.『iverilog 10counter.v 10counter_test.v』と入力しEnter

2.『vvp a.out』と入力しEnter

3.シミュレーションの実行結果が表示される(Fig.9)

Fig.9 シミュレーションの実行と結果

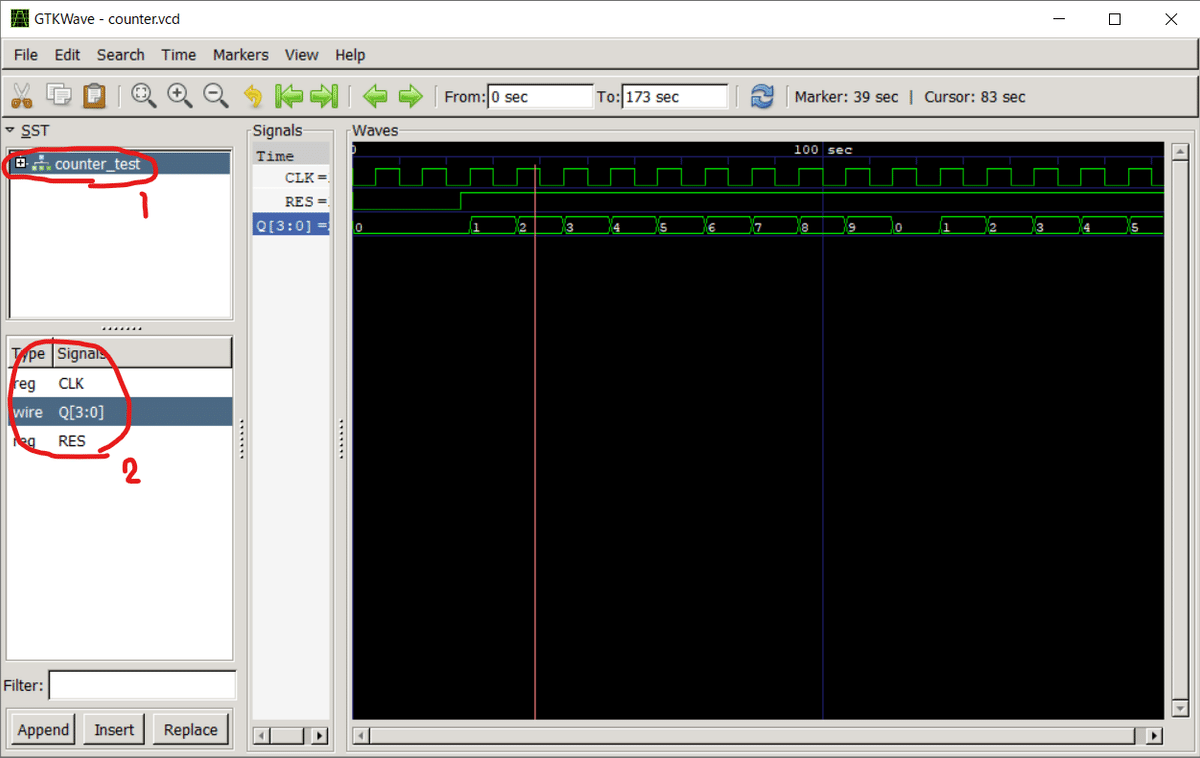

▼ 波形表示

1.ターミナルに『gtkwave counter.vcd』と入力しEnter

2.GTKWaveが起動する

3.左側SST内にある [+]counter_test をクリック

4.波形表示させたい変数(CLK, Q[3:0], RES)をそれぞれダブルクリック

5.波形が表示される(Fig.10)

Fig.10 GTKWaveによる波形表示

まとめ

Icarus VerilogとVisual Studio codeを用いた開発環境構築をして実際に回路シミュレーションを実行することができた。

この記事が気に入ったらサポートをしてみませんか?