僕の歴代赤石CPU(NX RED系)

前回は、名もなき時代の赤石CPUたちをご紹介しましたが、今回はついに名前がついた赤石CPUたちをご紹介したいと思います。

〜NXの初代〜

今では、BEで作っている本命的な赤石CPUはNX RED系ですが、このNX REDの中の真の初代は、NX RED Iではなく、NX Aだったのです。

この赤石CPUは、擬似4コアと2.5hzを目標にして開発が進んでいきました。

BEの赤石CPUを、ストラクチャーブロックの上限である64×64×64以内につくる縛りが始まったのは、このNX Aからでした。

メモリも、サイズ効率を高めるために、レジスタと同じものを並べるこれまでの方式から、メモリ専用にサイズ効率を重視した記憶回路を作る方式になりました。

ですが、この赤石CPUは遅延調整の段階で、完成することなくお蔵入りとなりました。

スペック

8bit

クロック周波数:2.5〜?Hz

ALU:不明

アキュムレータ:無し

レジスタ:8Byte(4Byte×2)

I/Oポート:インプット、アウトプットそれぞれ7or8ポートずつ

データキャッシュ:7or8Byte

メモリ:64Byte

命令キャッシュ:あり(容量不明)

ROM:無し(外付け)

PC:8bit

サイズ:64×64×?

高速化技術:極度細粒化

日付:2022年9月28日〜10月3日?

こんな感じになっています。

ROMが外付けなのは、CPU本体を64×64×64にして、ROMは64×64×64で別に作るようにすることにすることで、プログラミングされたROMの置き換えや、CPUが使えるサイズを向上させようと工夫した構造となっています。

〜NXからNX REDへ〜

NX Aは、失敗に終わりましたが、その次世代としてNX REDを作り始めました。

NX REDは今はNX RED VIのように、最後にローマ数字で世代が分かるようになっていますが、初代はI(ローマ数字の1)とかはなく、「NX RED」でした。

そして、この赤石CPUは(多分)完成しました。

当時の僕はずっと跳ね返る何かのような複雑なプログラムをテストで実行させていなかったので、ほんとうに完成していたのかは不明です…

ですが、NX Aの失敗は最初から擬似4コアと2.5hzを目指したのが原因だと思い、擬似2コア(&低クロック)という方向で作っていってたのを覚えています。

スペック

8bit

クロック周波数:0.38Hz?

ALU:不明

アキュムレータ:無し

レジスタ:8Byte(4Byte×2)

I/Oポート:それぞれ6ポートずつ

データキャッシュ:無し

メモリ:32Byte

命令キャッシュ:無し

ROM:無し(外付け)

PC:7bit×2

サイズ:不明

高速化技術:極度細粒化

日付2022年10月4日〜10月6日?

〜第二世代?第三世代?〜

NX REDの初代は、無事に完成(?)しましたが、やっぱり擬似2コア、低クロックなのにあまり満足いっていませんでした。

なので、また赤石CPUを作り始めました。

ALUも作り直しましたが、このALUがどんな性能を持っていたのかっていうのは、忘れてしましまいました…

レジスタの容量は半減して、データキャッシュ(もどき)が付いていますね。

ですが、やっぱ複雑になってきていたので、当時の僕も失敗する予感がしていたそうです…

ROMにも、手を加えました。

トーチ式なのに変わりはありませんが、トーチを設置ところを回路のブロックにしたり、想定していないところに設置してしまうことを防ぐために、埋めても大丈夫な空白は、色付きガラスブロックで埋めてあります。

実際には、もっと小型化することは可能でしたが、書き込みやすさを重視した設計となっています。

スペック

8bit CPU

クロック周波数:不明

ALU:不明

アキュムレータ:無し

レジスタ:4Byte(2Byte×2)

I/Oポート:それぞれ7ポートずつ

データキャッシュ:8Byte(もどき)

メモリ:32Byte

命令キャッシュ:無し

ROM:無し(外付け)

PC:7bit

サイズ:不明

高速化技術:極度細粒化

日付:2022年10月9日〜10月20日?

PCは7bitと中途半端ですが、7bitのROMを二つ繋げて動かす予定だったので、実質的には256個の命令を扱えます。

むずすぎて、息抜きにマリカーしたら全てを忘れてしまって、お蔵に収納となりました…

ですが、なんとかこのNX RED IIを完成させようと、制御回路だけ取り除いてから、また作り直した個体がありましたが、それも結局失敗に終わっています…

当時は、この個体の名前がよくわからんことになってましたが、今はNX RED II(リフレッシュ)って呼んでます。

intelのraptor lake refreshみたいな感じで

〜シリアルRAMとの出会い〜

NX RED IIIは、NX RED IIの反省を踏まえて、設計図的なのを書きながら進めていました。

NX RED IIの敗因は、やはり複雑すぎたこと…

それで、脳がパンクしていたことが原因だと思っていたので、回路同士の遅延の関係を紙に書くことで、それを抑えられると考えたわけです。

お気付きかもしれませんが、実はメモリの構造が大きく変わっています。

僕が「シリアルRAM」と呼んでいるタイプのメモリになりました。

ちなみに、このメモリは371ttiさんに教えてもらいました。

彼が「シリアルRAM」と呼んでいたので、僕もその名前で呼んでいます。

ただ、このメモリは制御が少し面倒なので、1rt毎に16段階で遅延を可変できる制御回路を、コンパぐるぐるのやつを上手く活用して頑張って作ってました。

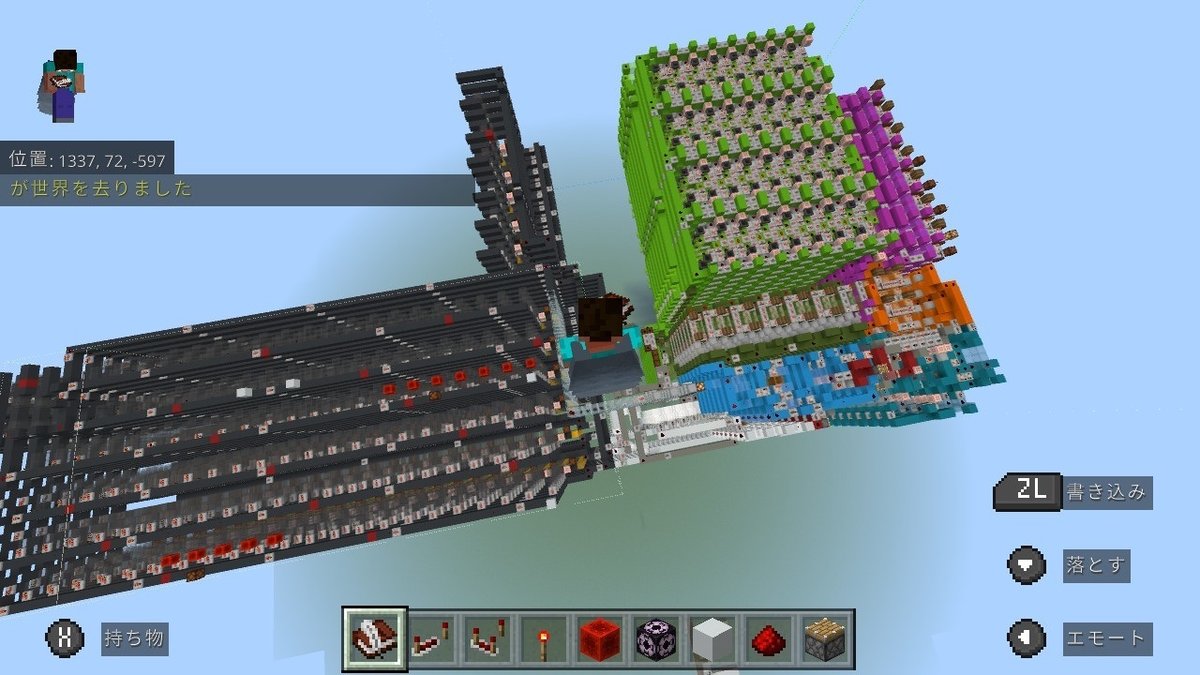

カラーリングは、データキャッシュ(もどき)が緑で、I/Oポートが赤紫、制御回路や命令デコーダー関係は白なので、配線によっては国旗になってそうな組み合わせもあります。

レジスタのアドレスバスには、少し弱めの信号を与えて負荷を軽減する工夫がされていますが、その部分もパウダーを減らせるように工夫してました。

I/Oポート内のデータバスにも、パウダーを減らせるように工夫がされています。

結果的に、この赤石CPUは悪い予感が的中し、完成することなく終わってしまいました…

スペック

8bit CPU

クロック周波数:0.625〜?Hz?

ALU:不明

アキュムレータ:無し

レジスタ:4Byte(2Byte×2)

I/Oポート:それぞれ7ポートずつ

データキャッシュ:7Byte(もどき)

メモリ:64Byte

命令キャッシュ:無し

ROM:無し(外付け)

PC:不明

サイズ:不明

高速化技術:極度細粒化?

日付:2022年10月22日〜10月25日?

〜やり直し〜

NX RED IIIは、残念ながら失敗と終わってしまいました。

なので、NX RED IVをその代わりとして、0から作り直しました。

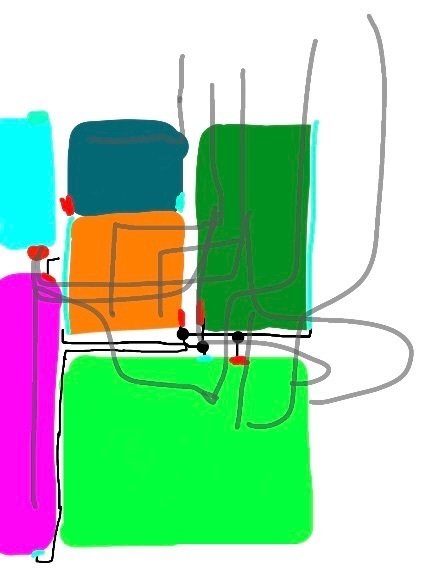

NX RED IVは、これまでとは違い、まず絵で回路のレイアウトを考えるところから始まりました。

青がALU、オレンジがレジスタ、緑がキャッシュ(もどき)、空色がPC、黄緑がメモリ、赤紫がI/Oポートで、空色の辺が出力部で赤色の辺が入力部です。

そして、この絵に近い感じのレイアウトでマイクラ上にも組み立てられていきました。

ですが、2022年10月27日、あることに気づきました……

このコンパレータのバグによって、XORも機能しなくなり、一部のCCAもお亡くなりになりました…

さらに、このバグはしばらく放置されなかなか修正されませんでした……

当然、このままじゃ回路は動かないので、しばらくこの赤石CPUは放置されることになるのです……

ちなみに、ROMの方も作り直しました。

トーチ式から信号強度式へ切り替えようと試みていました。

そして、信号強度式ROMの研究の結果、今のCRED Vや NX RED VIにも使われ続けられることになった強度式ROMが生まれたのです。

そして、このROMをたくさん並べて、デコーダーも取り付けられました。

端子?の部分が金ブロックで作っているところが、いい感じだ思ってます。

ちなみに、たしか金ブロックのところがCPUのストラクチャーとROMのストラクチャーの境目だったはずです。

I/Oポートの部分も、回路剥き出しという感じではなく、コンクリの壁で覆うような形となっています。

ちなみに、NX RED IVも設計図的なやつで各回路同士の遅延の関係を紙に書いていましたが、それでも無茶苦茶 苦戦してました、、、

結果的に、NX RED IVは完成することなく終わりました。

スペック

8bit

クロック周波数:0.625〜?Hz?

ALU:不明

アキュムレータ:無し

レジスタ:6Byte(3Byte×2)

I/Oポート:7ポートずつ

データキャッシュ:7Byte

メモリ:64Byte(シリアルRAM・16Byte×4)

命令キャッシュ:無し

ROM:無し(外付け)

PC:8bit

回路サイズ:不明

高速化技術:不明(無し?)

日付:2022年10月26日〜11月2日

〜SwitchからPCへ〜

これまでは、Nintendo Switch(初期型液晶モデル)で赤石CPUを作ってきていましたが、NX RED IVから PCで作り始めました。

Switchだと、やっぱり処理性能に限界あるし、なにより回路の移動とかマルチプレイもずっと楽なんです。

Switchの場合は、サブスクに入らないとマルチプレイなどはできませんでしたが、PCならタダですし。

そんなわけで、NX RED VはPCのBEで作られていきました。

NX RED Vは、ALUに僕が磨き続けたALUを使い、これまでと同じ形でレジスタと配線しています。

レジスタは8Byte(4Byte×2)になっています。

なんと、このNX RED Vには、僕の赤石CPUとしては初めてとなる乱数生成機が搭載されています。

これは、当時僕はライバルだと思っていた371ttiさんの赤石CPU(JE)にも、搭載されていたので、それに影響を受けたためです。

I/Oポートは、インプット・アウトプットともに7ポートとなっています。

メモリには、NX RED系では初めての信号強度式が採用されました。

この信号強度式RAMは、ループ式になっていて、これによりこのサイズで256Byteを実現しています。

この容量、このサイズというのは、結構満足しています。

まぁ、二進数と信号強度の変換や、ALUたちと少し距離があるので、そこは違和感がありますが、、、

NX RED Vでは、確実に動作させるために、赤石CPUの制御回路の構造を変えて開発されていきました。

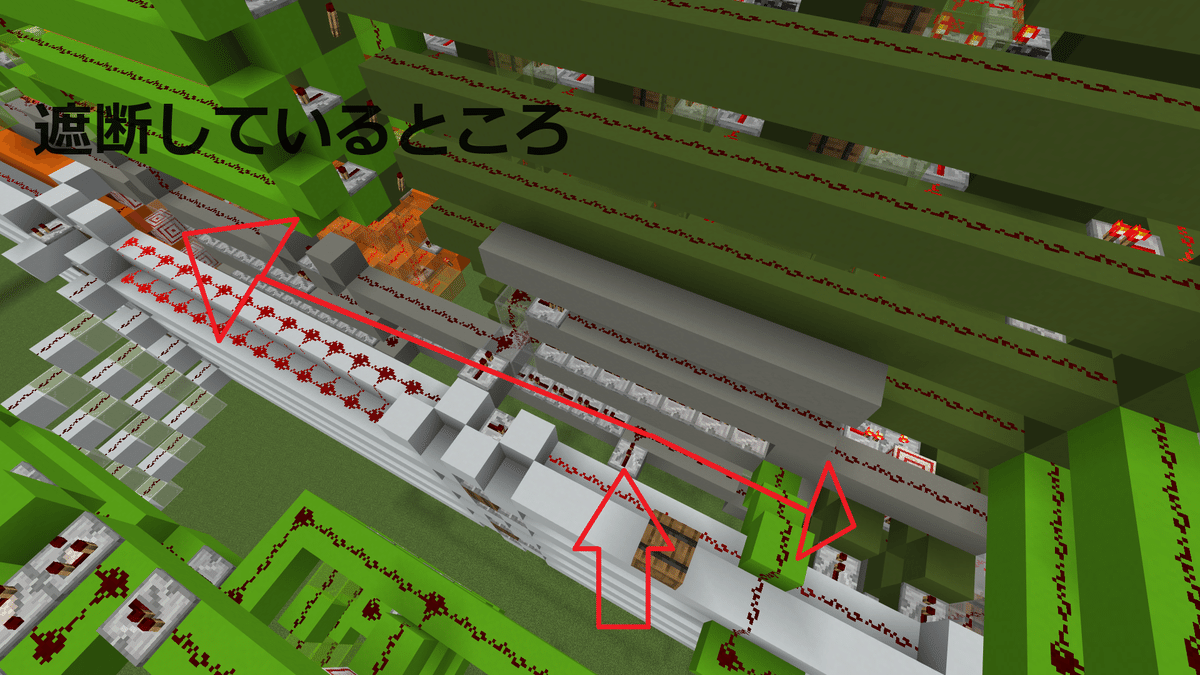

アドレスなどを入力する場所を一か所に集約しているのは、これまでと変わりませんが、その先にアドレスバスの信号を遮断している回路があります。

例えば

「レジスタ同士で加算してレジスタに保存」という命令を実行する場合はこの配線に信号を与えます。

次に、

「メモリからキャッシュへ情報を移動させる」という命令だった場合は、こちらの配線に信号を与えます。

こうすることで、各命令を実行させたときに、遅延の調整や原因の発見がしやすくなる。と僕は考えていました。

ところが、長い時間がたち、この赤石CPUのROMなどを悩んでる最中に、JEにはまり始め、結果的にこの赤石CPUのことはだんだんと忘れ去られていってしまい、次はNXREDJIの方になってしまいました、、、

スペック

8bit

クロック周波数:0.833〜?Hz

ALU:加減算、インクリメント、デクリメント、XOR、AND、OR、論理右シフト、右ローテート

アキュムレータ:無し

レジスタ:6Byte(3Byte×2)

I/Oポート:7ポートずつ

データキャッシュ:15Byte

メモリ:256Byte(HEXループ RAM・64Byte×4)

命令キャッシュ:無し

ROM:無し(外付け)

PC:10bit

回路サイズ:不明

高速化技術:不明(無し?)

日付:2022年11月25日〜12月?日

当時は、僕の誕生日が近かったのでHDDでも買おうかなぁ、、

とか考えながら作っていたのを覚えています。

~10Hzの夢へ~

NX RED系は、NX RED Vを最後に、しばらく放置されていました。

NXREDJ系や、CRED系の方をずっとやっていました。

2023年の1月から2023年の12月上旬まで、NX RED系は放置されていましたが、ここでついに再びNX RED系の赤石CPUが復活を果たします、、!

NX RED Vを作っているときから、10Hzの赤石CPUを夢見ていました。

やはり、高クロックというのに憧れていたんですよね。

ですが、10Hz化すると、レジスタの帯域が不足する問題が発生してしまうため、なかなかできない状態でした。

ですが、ある日の夜に突如それを解決する方法を思いつき、それを採用した赤石CPUの開発が始まりました。

もともとは、真のマルチコアとして、ALUを二つ搭載しようと考えていましたが、その必要もなくなったわけですね。

ですが、当時の僕にとってはこれは本当に重要なプロジェクトであり、本当はこの赤石CPUを作り終わったら、赤石勢を引退しようかと考えていました。

まぁ、その話はNX RED VIの解説記事を書くときがあったら、その時にお話ししたいと思います。

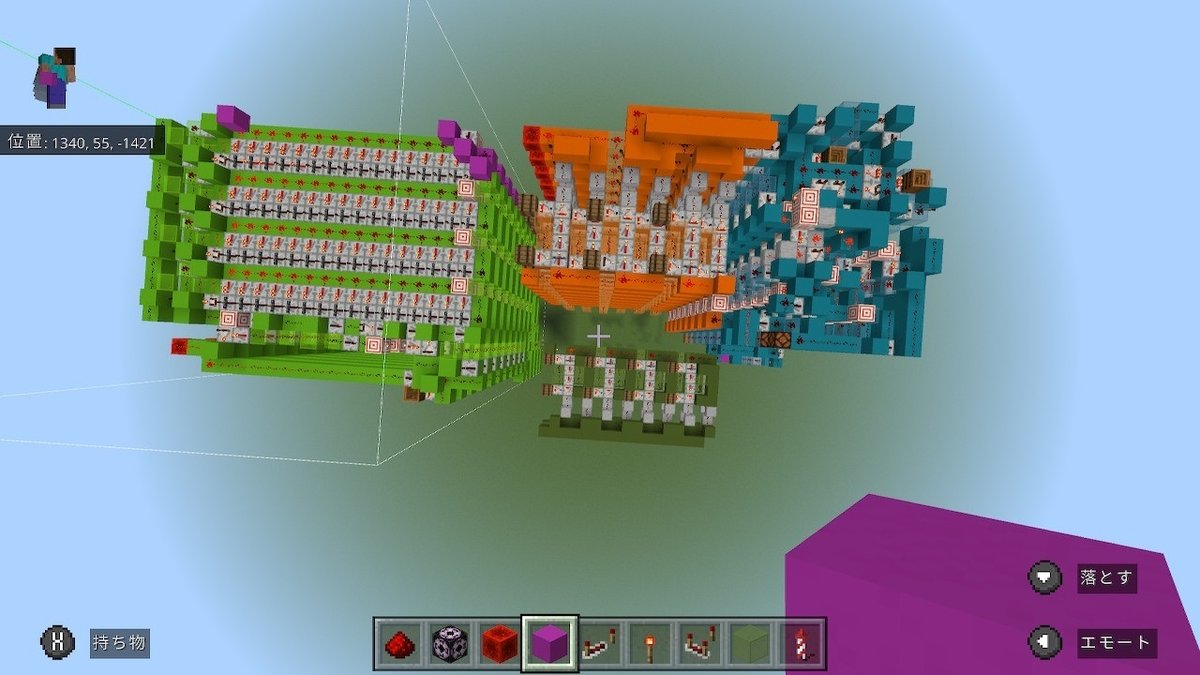

ALUとアキュムレータは、この赤石CPUのために専用に0から作りました。

10Hzに対応させる必要もありましたが、この赤石CPUの開発に着手するずっと前(NX RED VIの時)からALU&アキュを研究していて、その時に6rt毎や5rt毎のALU&アキュも可能であることが判明したので、そのALU&アキュも参考にしながら、これまで通りの演算機能を維持しながら6rt毎化を実現しました。

黄色の回路は、レジスタの効率を維持しながら10Hz化する独自の技術のための回路です。

レジスタとキャッシュもどきも、NX RED VIのために専用に開発しました。

ループ式となっているため、サイズ効率が向上しています。

レジスタの一部をキャッシュもどきとしても扱えるようにしているので、

レジスタは各疑似コア毎に16Byteで、そのうちの8Byteをキャッシュにも割り当ててるようなイメージになっています。

また、レジスタのサイズはかなり大型になっていますが、左右とループの合計容量は96Byteと、こちらも圧倒的に過去最高となっています。

I/Oポートは、CRED Vなどの過去作と似ているものを使っていますが、その合計ポート数はインプット・アウトプットどちらも16ポートとなっていて、過去最多です。

そのため、僕がBEで作る赤石CPUに自分で設けている64×64×64のサイズ上限ピッタリとなっています。

ちなみに、ROMは幅9CPUなどと同じものを使っていて、640Byte(命令256個分)となっています。こちらは、64×64×64からはみ出してしまったので、1列だけ別のところに配置しています。

メモリには、シリアルRAMが使われており、容量は256Byte(8Byte×32)となっていて、疑似的な別のコアが同時に同じアドレスにアクセスしてしまった場合に、誤作動を起こさないように専用のMMU(メモリマネジメントユニット)も開発し、ROMから読み出された命令は、MMUを経由してからメモリに指示が送られるような構造になっています。

NX RED VI(ver.6)(ver.1~4.6は失敗作です)

スペック

8bit

クロック周波数:10~0.082Hz

ALU:加減算、インクリメント、デクリメント、XNOR、XOR、AND、OR、論理右シフト、右ローテート

アキュムレータ:L1~L3

レジスタ:96Byte(16Byte×6)

I/Oポート:16ポートずつ

データキャッシュ:48Byte(8Byte×6)

メモリ:256Byte(シリアルRAM・8Byte×32)

命令キャッシュ:無し

ROM:640Byte(命令256個分)

PC:8bit(4bit×2)

回路サイズ:64×64×41

高速化技術:ROMキャンセラー(2.0)、多段階アキュムレータ(L3)、極度細粒化、分岐予測

日付:?~2023年12月13日〜2024年2月7日

NX RED系は約1年近く放置されていましたが、逆に言えば1年ぶりに10Hzへ進化して復活した赤石CPUとも言えますね。

ただ、10Hzで動いてるときはたしかにすさまじい速度なのですが、条件分岐命令などを実行したときは、とんでもなくクロックが低下してしまい、ずっと跳ね返る何かの速度では約半年前のNXREDJVと比べても、大差をつけられてしまっているので、まだまだ改善できるところはありそうです。

この記事が気に入ったらサポートをしてみませんか?