高速に動く波形について考えてみる。

HBM3の記事を見ていてASICと積層したDRAMが同じパッケージ内に組み込まれているのをみたとき、すごく衝撃を受けました。前職では、映像を制御くする高速伝送用のICの開発に携わっていたこともあり、技術の進歩のすごさを実感しています。

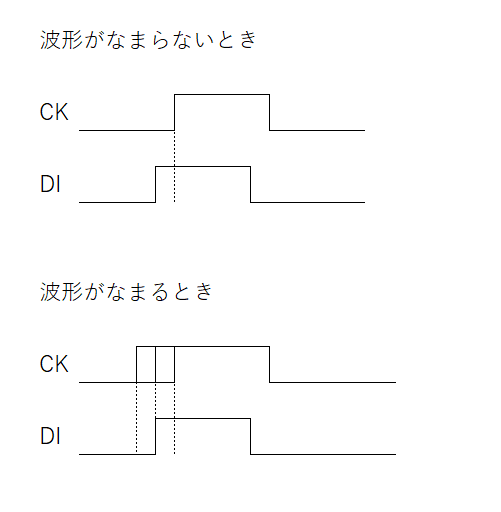

波形が高速になってくると、データの誤作動が起きるリスクが増えていきます。ICを動作させるには、データを取り込むための波形をCK信号、入力するデータをDI信号があり、クロックが立ち上がった時のDI信号の状態を信号として伝えてロジック回路が動作していきます。動作の仕方は、仕様書で決められた順番でデータを入れてあげることで、出力する信号が変化することでICはディスプレイに画像を表示するような操作ができるようになります。

高速になってくると、CKやDIの立ち上がりが短くなってしまうことで期待してないタイミングでデータを取り込んでしまいます。そうすると、下記の波形がなまる状態となり、誤作動が生じてしまいます。

パソコンが活用される前の時代では、CKやDIの信号の制御はシンプルでした。しかし、回路をコードで書くようになってくると複雑な制御もできるようになり、外部に出すピン数を減らす設計が求められるようになり、パラレルの信号を使うことからシリアルの信号へと変化してきました。

誤作動が起きる要因を回避するための技術として、シリアル信号を高速かつ正確に伝送する技術としてCKを差動にする技術が生まれました。ICからICへ信号を正確に伝えるには、差動信号を同調配線にしたり、電源が安定してノイズの生じにくい場所にICを配置したり、高速に動作すると電力が消費しやすくなり発熱しやすい問題が生じてきました。

それを解決して実装しているところが、すごく衝撃的でした。シンプルに考えると、IC同士の信号をノイズを抑えていくのは、近くに配置が最適です。発熱 = 消費電力を抑えるには、微細化して動作電流を小さくさせる必要があります。それを解決するために微細化して同じチップに組み込むということは、なかなか高いハードルがあります。例えば、パッケージに3つのチップを積層させる場合、この3つのうち1つでも不良品があれば使えなくなります。たとえ不良品が出る確率が1チップ当たり0.1%だったとしても、3つ組み込めば0.3%近くの確率で使えなくなります。

新しい技術が実用化されていくために、今までの技術の中に何かプラスとなる問題を解決することがあって発展していくんだなぁ。。

この記事が気に入ったらサポートをしてみませんか?