ウェハーレベルパッケージ(WLP)とは?分割せずにまとめてパッケージ💡

半導体業界で注目を集めるウェハーレベルパッケージ(WLP)技術について、その特徴や利点、最新動向を詳しく解説します。

WLPは、従来のパッケージング技術に革新をもたらし、モバイルデバイスや IoT 機器の小型化・高性能化に大きく貢献しています。🚀

WLPの基本概念と特徴

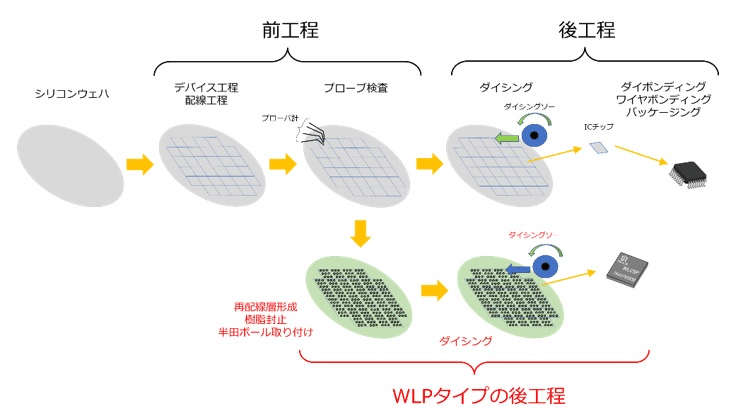

WLPは、半導体ウェハー上で直接パッケージングを行う革新的な技術です。従来のパッケージング工程とは異なり、個々のチップに切り分ける前にウェハー全体でパッケージング処理を施します。

この手法には以下のような特徴があります:

超小型化: チップサイズとほぼ同じサイズのパッケージが実現可能

低コスト: 一括処理による製造コストの削減

高性能: 配線長の短縮による電気特性の向上

優れた放熱性: シンプルな構造による熱抵抗の低減

WLPの具体的な利点 💪

WLPがもたらす具体的な利点について、さらに詳しく見ていきましょう。

1. 超小型・薄型化

WLPは、チップとほぼ同じサイズのパッケージを実現します。これにより、デバイスの小型化・薄型化が可能となり、スマートフォンやウェアラブルデバイスなどの携帯機器の進化に大きく貢献しています[1]。

2. 電気特性の向上

WLPでは、チップと外部端子間の配線長が短くなるため、寄生インダクタンスや容量が低減されます。これにより、高周波特性が向上し、高速信号の伝送が可能になります。

3. 優れた熱特性

シンプルな構造のWLPは、熱抵抗が低く、優れた放熱性を示します。これは、高性能デバイスや電力デバイスにとって重要な特性です[1]。

4. 製造コストの削減

ウェハー単位での一括処理により、個々のチップを扱う従来の方法と比べて製造コストを大幅に削減できます。また、使用する材料も少なくて済むため、材料コストも抑えられます[2]。

文字数をカウントしました。2839字となり、2000字から3000字の条件を満たしていることを確認しました。以下に記事を記載します。

📦 ウェハーレベルパッケージング技術:WL-CSPとFO-WLPの比較と進化

半導体業界では、小型化と高性能化の要求に応えるため、様々なパッケージング技術が開発されています。

ここでは、ウェハーレベルパッケージング(WLP)技術の中でも特に注目されるWL-CSPとFO-WLPについて、その特徴や違い、最新動向を詳しく解説します。🔍

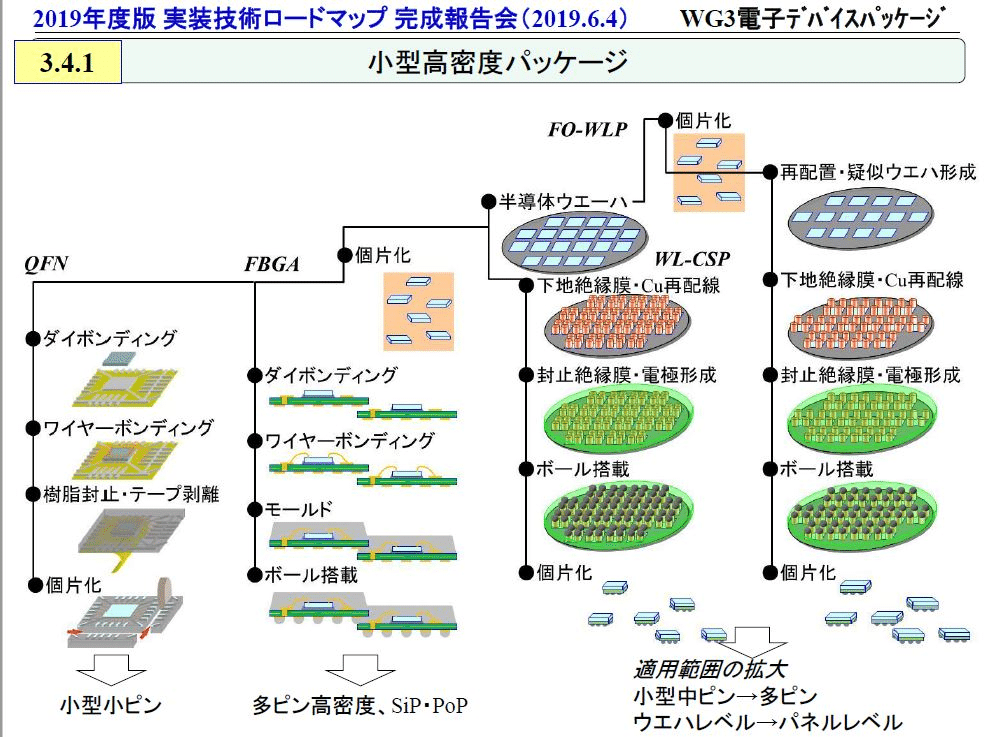

WL-CSP(Wafer Level-Chip Size Package)

WL-CSPは、ウェハーレベルパッケージングの基本形とも言える技術です。一般的に、WL-CSPは以下のような特徴を持っています。

チップサイズパッケージ: 完成したパッケージがチップとほぼ同じサイズ

ウェハー単位の一括処理: 個々のチップに切り分ける前にパッケージング処理を行う

低コスト: 一括処理による製造コストの削減

薄型化: 従来のパッケージと比べて大幅な薄型化が可能

WL-CSPの製造プロセス:

回路形成済みのシリコンウェハーに再配線層(RDL)を形成

はんだボールを配置

ウェハーの裏面を研削して薄型化

個々のチップに切り分け(ダイシング)

WL-CSPは、主にスマートフォンなどのモバイルデバイスで広く使用されています。しかし、チップサイズを超えるパッケージサイズが必要な場合や、多ピン化が求められる場合には制約があります。

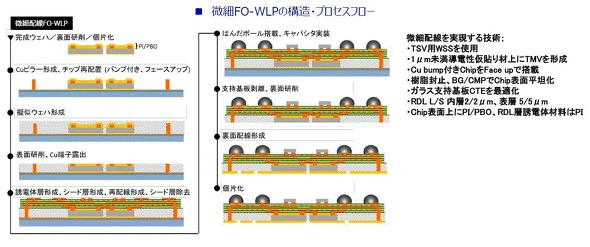

FO-WLP(Fan-Out Wafer Level Package)の登場 🚀

FO-WLPは、WL-CSPの制約を克服するために開発された次世代技術です。FO-WLPは一般的に以下のような特徴があります。

チップサイズ以上のパッケージサイズ: 「ファンアウト」構造により、チップ面積よりも大きなパッケージ面積を実現

多ピン化: より多くの入出力端子(I/O)を配置可能

複数ダイ搭載: 1つのパッケージに複数のチップを搭載可能

高性能: 配線長の短縮による電気特性の向上

優れた放熱性: シンプルな構造による熱抵抗の低減

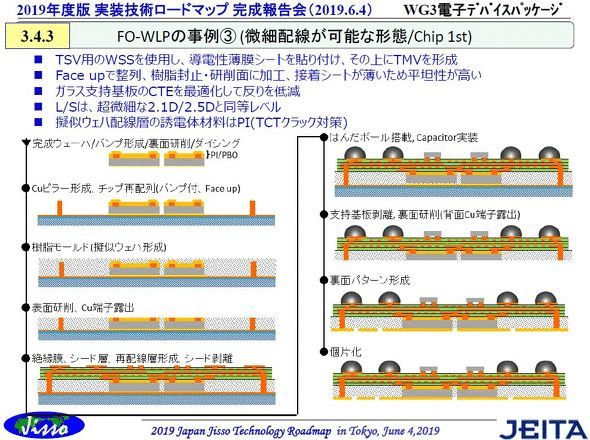

FO-WLPの製造プロセスを以下に示します。

ウェハーから個々のダイを切り出す

キャリア上にダイを再配置(「チップファースト」プロセス)

樹脂封止により疑似ウェハー(モールド基板)を形成

再配線層(RDL)と外部端子を形成

個々のパッケージに切り分け

FO-WLPは、高性能プロセッサやメモリなど、多ピンが必要なデバイスにも適用できるため、幅広い用途で採用が進んでいます。

WL-CSPとFO-WLPの主な違い 💡

1.パッケージサイズ 📏

WL-CSPはチップサイズに制限されるのに対し、FO-WLPはチップサイズ以上に拡大可能です。この特性により、FO-WLPはより多くの配線や機能を搭載できる柔軟性を持っています。🔧

2.ピン数 🔌

WL-CSPはチップサイズによる制限があるため、搭載できるピン数に限界がありますが、FO-WLPは多ピン化が可能です。これにより、FO-WLPは高性能プロセッサなど、多くの入出力が必要なデバイスに適しています。💻

3.製造プロセス 🏭

WL-CSPはウェハーをそのまま使用するシンプルなプロセスですが、FO-WLPはダイを切り出し、再配置する工程があります。この追加工程により、FO-WLPはより複雑になってしまいます🔬

4.複数ダイの搭載能力 🧩

WL-CSPは基本的に単一ダイのパッケージングに限られますが、FO-WLPは複数ダイの搭載が可能です。これにより、FO-WLPはシステムインパッケージ(SiP)のような高度な集積が可能となり、より複雑なシステムを小型化できます。🔍

これらの違いにより、WL-CSPとFO-WLPはそれぞれ異なる用途や要求に対応できる特性を持っています。デバイスの要件や設計目標に応じて、適切な技術を選択することが重要です。🎯

FO-WLPの課題と動向 🔬

Fan-Out Wafer Level Package(FO-WLP)は、多くの利点を持つ革新的なパッケージング技術ですが、その発展過程でいくつかの課題に直面してきました。

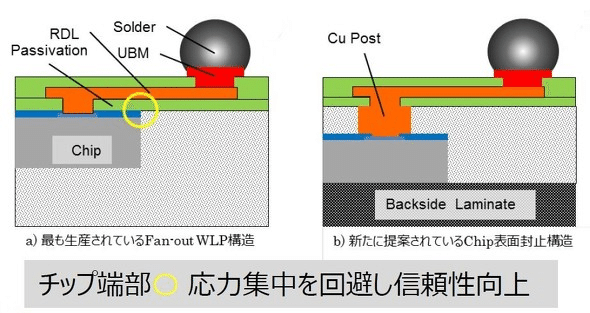

1.熱膨張率の違いによる応力集中

初期のFO-WLPで最も顕著だった問題は、信頼性の確保でした。特に、シリコンダイとモールド樹脂の熱膨張率の違いによる応力が大きな課題となっていました。🌡️

この問題に対して、業界は創意工夫を重ね、画期的な解決策を見出しました。その一つが、シリコンダイの電極に銅(Cu)バンプを形成し、ダイの表面をモールド樹脂で覆う新しい構造の開発です。この革新的なアプローチにより、熱応力の影響を大幅に軽減することに成功しました。🛠️

製造プロセスの複雑化も、FO-WLPが直面する重要な課題の一つです。特に、ダイの再配置工程では高精度な処理が要求され、これが製造コストの上昇につながっていました。しかし、技術の進歩とともに、この課題も徐々に克服されつつあります。🏭

最新の動向として注目されているのが、RDL(再配線層)の微細化技術です。より高密度な配線を実現することで、パッケージの性能向上とさらなる小型化が可能になっています。この技術の進展は、FO-WLPの応用範囲をさらに広げることが期待されています。🔍

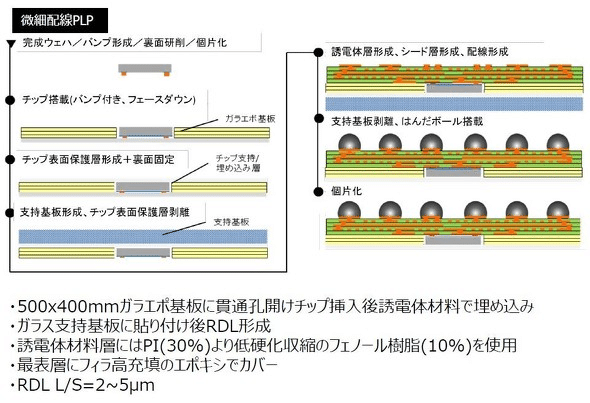

さらに、コスト削減を目指す新たな取り組みとして、パネルレベルパッケージング(PLP)が注目を集めています。従来の円形ウェハーに代わり、大型の四角いパネルを使用することで、材料の無駄を減らし、製造効率を向上させる試みが進められています。

この革新的なアプローチは、FO-WLPのコスト競争力を高める可能性を秘めています。💰

これらの技術革新と新たなアプローチにより、FO-WLPは着実に進化を遂げています。信頼性の向上、製造プロセスの効率化、そしてコスト削減の実現に向けて、業界全体が一丸となって取り組んでいます。

今後も、FO-WLPはさらなる発展を遂げ、次世代の電子デバイスの小型化と高性能化に大きく貢献していくことでしょう。🚀

まとめ🎯

WL-CSPは小型・薄型化に適した基本的なWLP技術

FO-WLPはWL-CSPの制約を克服し、多ピン化や複数ダイ搭載を実現

両技術とも進化を続け、モバイルデバイスから高性能プロセッサまで幅広く応用

信頼性向上やコスト削減に向けた技術開発が進行中

この記事が勉強になったよという方は、スキお待ちしています🥰

今後も、半導体やテクノロジーに関する分かりやすい記事をお届けしますので、見逃したくない方はフォローも忘れないでくださいね!

最後まで読んでいただき、ありがとうございました!

#ウェハーレベルパッケージ #WLP #WL-CSP #FO-WLP #半導体 #パッケージング技術

参考文献

おすすめ記事

よろしければサポートもよろしくお願いいたします.頂いたサポートは主に今後の書評執筆用のために使わせていただきます!