フリップフロップ回路まとめてみた

授業でフリップフロップ回路を学んだが、モヤモヤが残ったので、色々調べてまとめてみた。

イントロダクション

パソコンは二つの方法で情報を記憶してます。コンデンサーを使う方法と回路を使う方法です。

コンデンサーで記憶する場合は、0/1の情報を電気のON/OFFの関係に対応させます。半導体メモリのDRAM(Dynamic RAM)と呼ばれるものです。

一方、回路で記憶する場合は、電圧の高低を情報の0/1の関係と対応させます。半導体メモリのSRAM(Static RAM)と呼ばれるものです。

そして、この時に使われる回路を記憶回路と言います。

記憶回路

記憶するとは、ある(物理的な)状態を保持することだと言い換えられるでしょう。

これを実現するために記憶回路では、出力を再び入力(フィードバック)することで回路に高電圧/低電圧が流れている状態をつくります。

状態を保持するために電流が絶えず流れているのです。

これは入力の組み合わせによって出力が変わる一般的な回路と違う点です。

次に一般的な記憶回路の仕様を確認しましょう。

図1に最も基本的なフリップフロップである、RSフリップフロップを構成する記憶回路を描きました。

ご自分で(S,R)に0,1の入力値をいれて、動作確認をしてみてください。

図2のような真理表になったはずです。

情報が記憶されていることが確認できたでしょうか。これで2進数を表すことができますね。

このように真理表(動作表)を使うと、回路の動作を分かりやすくまとめることができます。

ここで(0,0)が禁止である理由を説明します。入力を(0,0)にすると、出力が前の状態に依らず(1,1)になります。

しかし、記憶回路は両出力が互いに逆であって初めて機能するので、出力を同じにしてしまうのは設計上許容し難いです。

この(1,1)の状態は非安定状態とも呼ばれています。非安定状態とは、Qが高電圧でも低電圧でもなく(電圧の高低は相対的なものでQ=_Qの時、区別ができない)、どのような入力でもこの状態を壊すことができる状態です。

記憶回路としては役に立ちませんが、「チャージ増幅器」として実際はとても有効です。

なお、NANDゲートをNORゲートに置き換えて同じ回路を作れますが、その場合は結果が反転することに注意しましょう。

クロックパルス

さて、これで情報を記憶することはできましたが、マルチプロセッサのように記憶した情報を使って複雑な計算する場合は、入力・出力の動きを同期させる必要があります。

例えば、三つの入力を加算する回路において、本来(0,1,1)であるはずが、一部の入出力の遅れで(0,0,1)となったら大変ですよね。

そこで、クロックパルスの登場です。

クロックパルスは、高電圧と低電圧の2値をとる周期的なパルス信号です。

単にクロックとも呼ばれます。図3にクロックパルスのつくる方形波を載せました。

さて、クロックパルスが指揮者のように振る舞い、他の回路がタイミングを合わせるわけですが、そうなるとクロックパルスのどこにタイミングを合わせるかが悩ましいところです。

一つの方法としては、ゲート型というものがあります。ゲート型はクロックが1の時は任意の出力を受け入れます。

あたりまえですが、これは同期が難しいのであまり使われません。

実際には、電圧が変化する瞬間に合わせることが多いです。

これをエッジトリガ動作(edge-triggered action)と呼びます。

これらはさらに、立上がり(ポジティブエッジ)か、立下り(ネガティブエッジ)かで、ポジティブエッジ型とネガティブエッジ型に分けられます。

余談ですが、パソコンの性能を表す指標であるクロック数もここからきています。

前述の通り、クロックパルスに同期して情報の取り出しや演算が行われるため、「クロック数が高い=同じ時間でもより多く演算ができる」ということになり、パソコンの能力に直結するのです。

このクロックパルスによって駆動される記憶回路をフリップフロップと言います。

ただ一部、記憶回路だけをRSフリップフロップと呼ぶ場合もありますが、説明がしやすいので今回は記憶回路とクロックパルスを合わせてフリップフロップと呼ぶことにします。

RSフリップフロップ

RSフリップフロップは最も基本的なフリップフロップになります。

名前の由来

フリップフロップは、RSフリップフロップの前身となるマルチバイブレーターに由来します。

初期のマルチバイブレータは、記憶の保持のために、回路のフィードバックではなく、リレーを使って物理的に記憶していました。

リレーとは、電気信号を受け取り、ON/OFFの切り替えを行うスイッチみたいなものです。

このリレーがFlip(跳ね上がる)、 Flop(ばたんと倒れる)を繰り返すことから名前が付きました。

ちなみに、ビーチサンダルのことも英語でFlipflopと呼びます。

リレーもビーチサンダルもパタパタと繰り返し動くことから同じ名前になったと推察されます。

また"RS"の部分ですが、こちらもマルチバイブレータが由来です。

メインの出力であるQに注目すると、Q=0がデフォルトで、S=1を入力するとQが0->1でSet(S)された状態になり、R=1を入力するとQが1->0でReset(R)された状態になります。

このことから入力はRとSであり、Q=1がSet状態、Q=0をReset状態と呼びます。

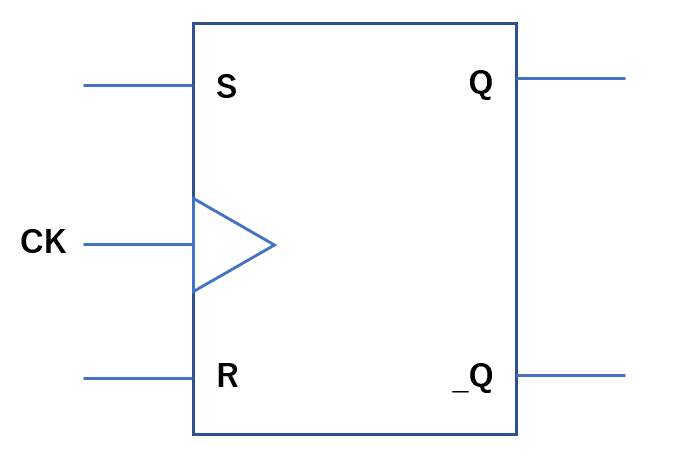

回路図と記号

回路図と記号は、それぞれ図4と図5のようになります。

エッジトリガ型は少し複雑になってしまうので図4はゲート型です。

エッジトリガ型の機能を含めた回路は後ほど出てくるDラッチの方で説明します。

仕様

記憶回路にクロックパルスがついただけなので基本的な仕様は同じです。

なお、フリップフロップの場合は入出力だけでなく、状態も考慮しなければいけないので、真理値表の代わりに特性表というものを使うことがあります(図6)。

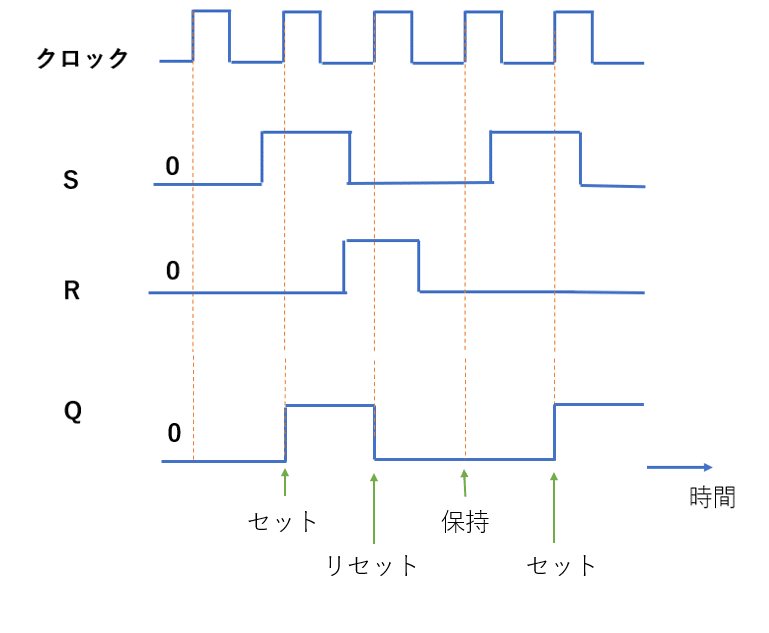

さらに、図7のタイミングチャートという図を使って仕様を確認しましょう。

このRSフリップフロップはポジティブエッジ型なので、例えば立ち上がりのタイミングで(S,R)=(1,0)だと、Q=1にセットされます。

Dラッチ

RSフリップフロップの入力をDだけにしたバージョンです。

入力Sを反転させて入力Rに入れます。

ラッチとは留め金の意味です。"D"の由来は諸説あり、データの’D’であるとも言われています。

以下詳しく見ていきましょう。

回路図と記号

Dラッチの回路図は、図8のようになります。

エッジトリガ型RSフリップフロップを使うと図9のようにも書けまが、Dフリップフロップとの対比のためDラッチは基本的にゲート型なので、この書き方はあまり見ないです。

Dラッチの仕組みを理解するのが目的なら、図9は分かりやすいでしょう。

記号は図10のようになります。

Dフリップフロップと区別するためにクロックの三角はかかないことに注意しましょう。

Sの入力をインバータで反転させてRに入れていることが分かる。

仕様

図9にあるようにDラッチはRSフリップフロップの入力’_S’にしただけです。

したがって、特性表及びタイミングチャートは図11,図12の通りです。

一点、Dクラッチはゲート型なので、クロックが論理1である間は全ての変化を受け取ってしまうことに注意しましょう。

Dフリップフロップ

エッジトリガ型のDラッチです。

Dラッチの改良版とも言えるでしょう。

図13のように、Dフリップフロップは二つのDラッチを使ってつくることができます。

クロックの入力が反転されているので、エッジの部分でしか反応しないことがわかるでしょう。

また、記号は図14のようになります。

Dラッチの部分でも書きましたが、クロックの三角形がつくことに注意しましょう。

回路図と記号

仕様

仕様についてはDラッチとほぼ同じです(図16)。ゲート型かエッジトリガ型かの違いです。それを踏まえて、図17のタイミングチャートも確認してください。

参考文献

AC Fischer-Cripps, Rhe Electronics Companion, 朝倉書店, 217

Myke Predko, Digital Electronics Demystified, 翔泳社, 307

金子峰雄, デジタル電子回路, 培風館, 220

以上。