VHDL初級編 ~VHDL記述の基本フォーマット~

ミンガラバー(Mingalaba)!

“ミンガラバー” はミャンマー語で “こんにちは” という意味です。

私は2020年度にPALTEKに入社したミャンマー出身のシーでございます。

私はミャンマーの大学で、電気やハードウェアの基本を学びました。

ハードウェア記述言語(HDL)の基本も学習しましたが、実際にXilinxのボードを動かしたことはありませんでした。そんな私が社内研修ではじめてHDLを使いXilinxボードでスロットマシンを開発できるようになりました。

このブログでは研修で学んだVHDL記述の基本フォーマット、VHDLやVerilog-HDLについて簡単に紹介させていただきます。いろいろなことを学習中なので至らないところは多いかと思いますが、同じく学習中の方に少しでも役に立てば幸いです。

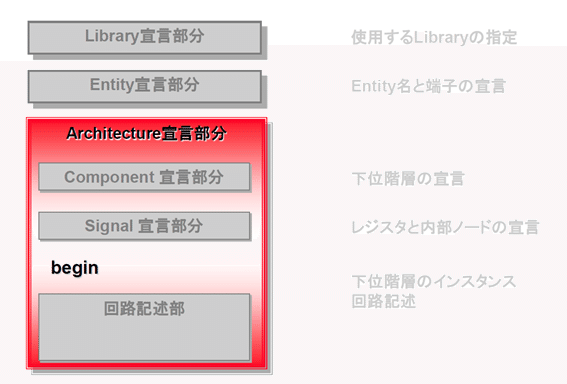

前回は、Library宣言部分とEntity宣言部分を学びました。

ここまでは、回路の外側の箱を用意するイメージとなりますが、今回学習するArchitecture宣言部分で、回路の中身を作ることになります。

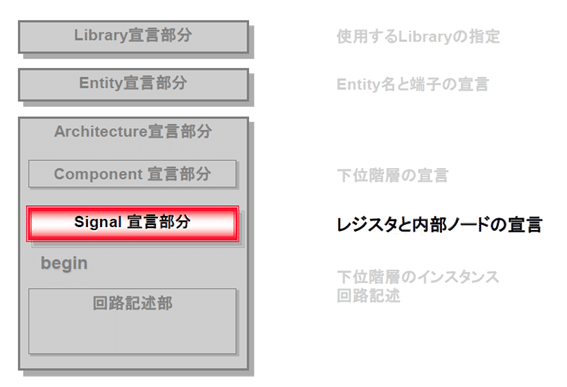

Architecture宣言部分は、主に①Component宣言部分、②Signal宣言部分、③回路記述部から成り立ちます。

今回は、②③を学びます。

※①Component宣言部分については、次回以降での説明となります。

図 1- Architecture宣言部分

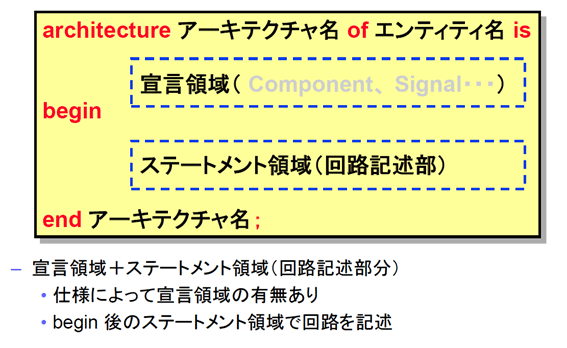

図 2- Architecture 文法

Signal宣言部分

図 3-Signal宣言部分

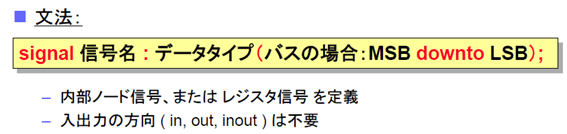

Signal宣言

図 4-Signal文法

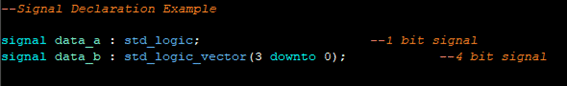

図 5-Signal宣言例

※内部ノード信号がレジスタ信号のどちらかになるかはSignal宣言の段階では決まらない。回路記述部での使い方で決める。

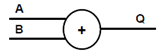

◆信号代入文①

文法

図 6-信号代入文法

信号接続は、両辺のビット幅を揃える。

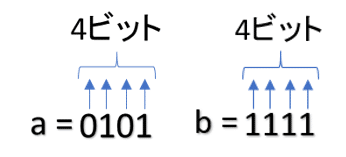

例1:b <= a;

※両辺のビットの幅がそろっている場合、ビット幅を省略できます。

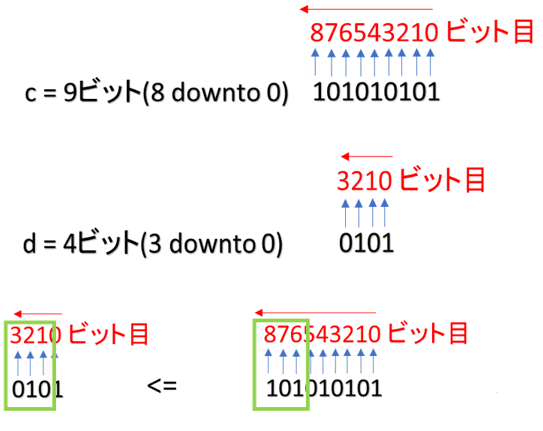

例2:d(3 downto 1) <= c(8 downto 6);

結果は、代入した「101」+元々残った1ビット目のデータ「1」、

「d = 1011」 になります。

◆信号代入文②

●信号や演算式を代入する場合、

例1:dout <= din + 1; (+‘1’/-‘1’の場合のみ、‘’は省略可。)

例2:C <= not (A and B);

● 固定値を直接代入する場合、

-1bit値はシングル・クォーテーション

例3:rst <= ‘1’;

-バス値はダブル・クォーテーション

例4:din_F <= “000”;

例5:data__in <= “00000000”;

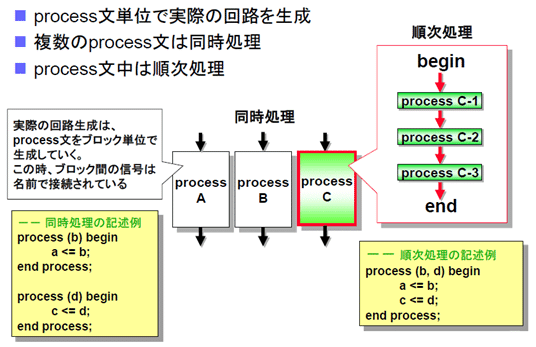

◆Process 文

図7-process文

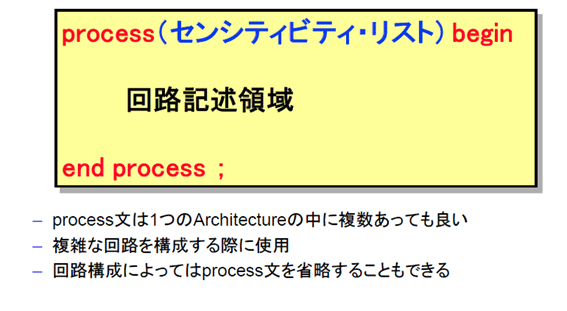

◆Process 文の書式

文法

図 8-process文法

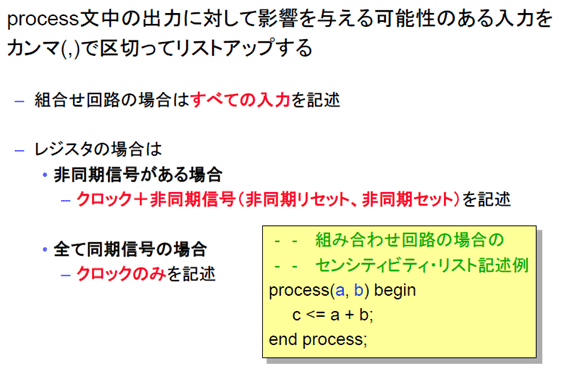

◆センシティビティ・リスト

図 9-センシティビティ・リスト

process(------)begin

(------)の部分にセンシティビティ・リストを入力します。

上の例の場合は、「c」は、「a」と「b」に対して変わりますので、

「a」と「b」はセンシティビティ・リストに入力します。

VHDL設計での演算子の種類

◆VHDL設計での演算子の種類

1. 論理演算子(and、or、nand、nor、not、xor)

i. 例:Q <= not A

![]()

2. 算術演算子(+、-、*、/)

i. 例:Q <= A+B;

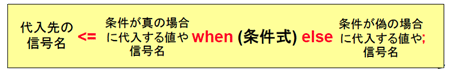

3. 関係演算子(=、/=、<、<=、>、>=)

i. 文法:

例:q <= ‘1’ when (a=b) else ‘0’;

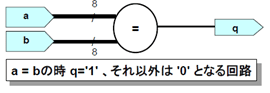

4. 連接演算子(ビットの結合、&)

i. 複数の信号を結合し、新しい信号を作成する

例:D (2 downto 0) <= E & F & G;

複雑な組み合わせ回路

◆演算子、if文、case文を使用して記述

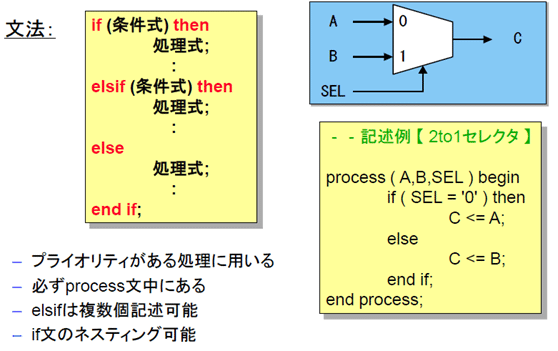

- If文

最初の案件が処理された後、次の案件が実行される。(プライオリティあり)

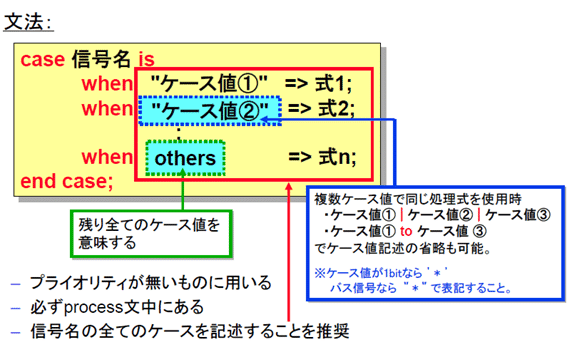

- Case文

値の順番に関係なく全て並列に処理がせれる。(プライオリティなし)

全てのケースを記述しないと文法エラー。

Others は残り全ての場合という意味。

(othersに“XXX”と記述し、冗長回路を省略)

◆If文の文法

図 11-if文法

◆Case文の文法

図 12-case文法

◆Case 文の記述例

図 13-case文の記述例

組み合わせ回路記述例(1)

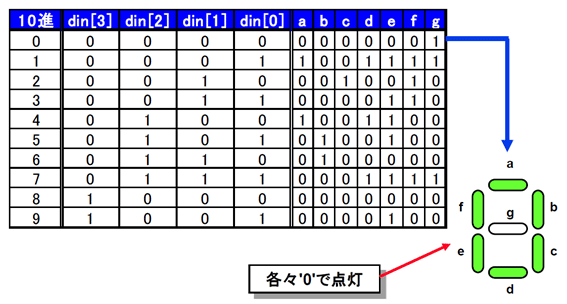

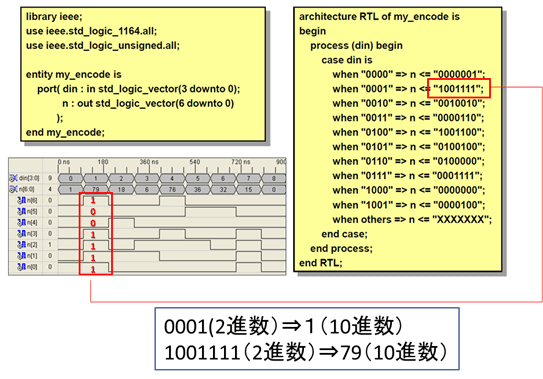

◆エンコーダ(符号器)

• 情報を特定のルールで符号化する回路

• 例:数字→Seven Segmentに表示

(0~9)の数字を表示するためには、Seven Segmentにどこのsegment はonにしてどこにoffにするかを指定する必要があります。よって、エンコードするのは 表示したい信号(0~9)からそれによって Seven segmentにon/off する信号(例:0000001, 1001111, ..)にすることです。

図 14-Seven Segmentエンコーダ表例

◆エンコーダ記述例

図 15-エンコーダ記述表

組み合わせ回路記述例(2)

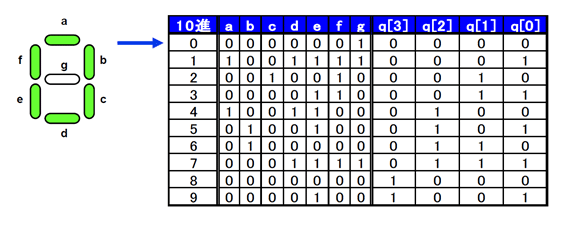

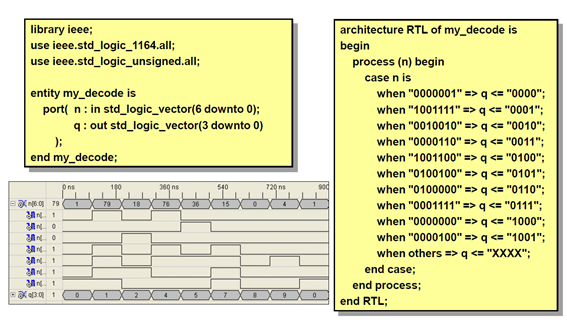

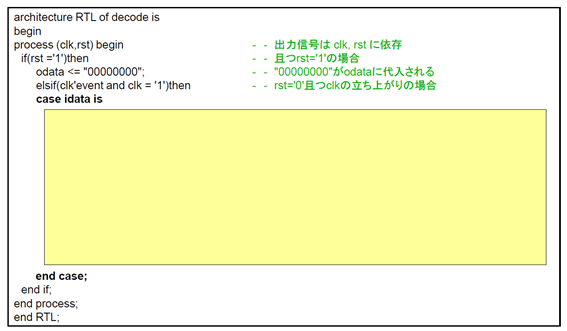

◆デコーダ(復号器)

• 特定のルールのもとに符号化された情報を元に戻す回路です。

図 16‐Seven Segmentデコーダ表例

◆デコーダ記述例

図 17-デコーダ記述例

組み合わせ回路記述例(3)

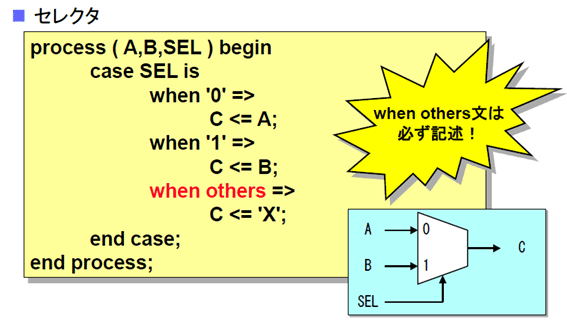

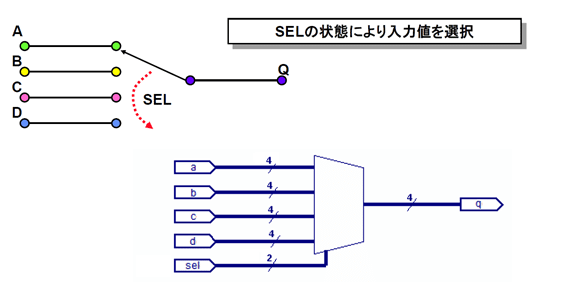

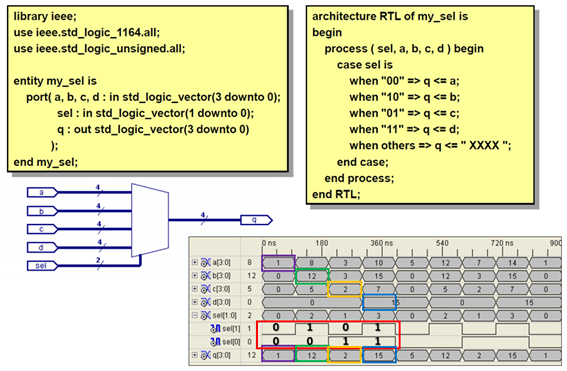

◆セレクタ(マルチプレクサ)

複数の入力信号のうち1つを選択して出力する。

図 18-セレクタ

◆セレクタ(マルチプレクサ)記述例

図 19-セレクタ記述例

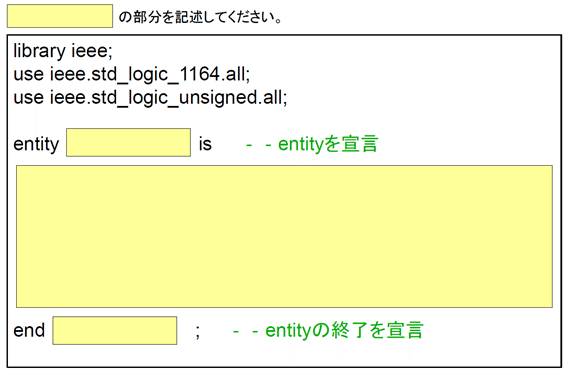

作業手順は以下の通りです。

手順1: 新規プロジェクトの作成

1. Vivadoの起動

2. 前回の新規プロジェクト作成手順と同じように新規ファイルを作成しま す。

2-1. 新規プロジェクト名 : LAB2

2-2. 保存先フォルダ:C:/Home/VHDL(自分で適当にしても構いません)

2-3. 新規ファイル名:decode とします。

手順2:作成した decode.vhdファイルが開かれます。

以下の図の中のコードを記入し、黄色い部分に課題の解答コードを記入して保存します。

※緑色のコードは書かなくてもいいです。

図 21-組み合わせ回路演習1/2

図 22-組み合わせ回路演習2/2

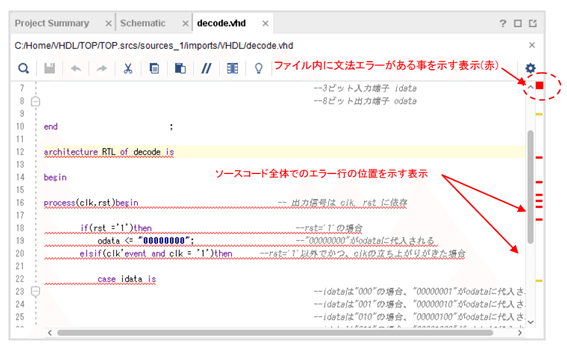

ソースコードに文法エラーがある場合、

ソースコードの該当箇所がハイライト表示されたり、赤い波線が引かれたりします。カーソルを合わせると、メッセージがポップアップされます。

テキストエディタの表示で判断できるエラーは、解る範囲で、Vivadoで文法チェック前に修正しておくと効率的です。

図 23-ファイルの編集画面

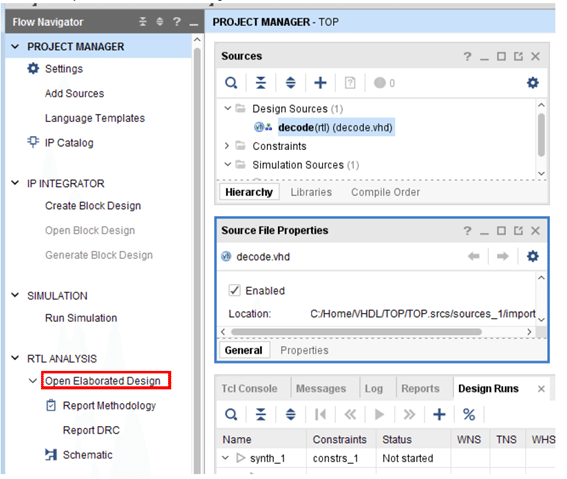

手順1:

RTLのElaborateを実施します。

Open Elaborated Designをクリックします。

確認ダイアログが表示された場合は、OKをクリックします。

文法エラーがある場合、エラーメッセージダイアログが表示されます。OKをクリックします。

図 24-Elaborateの実行

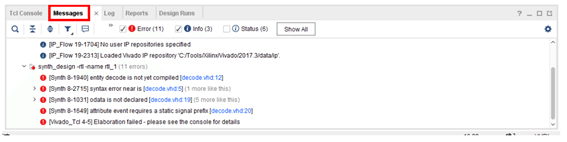

手順2:

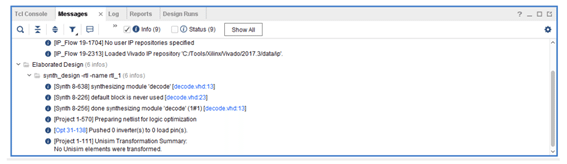

エラーがあった場合、GUI下部のMessageウインドウに、

ファイル名、行数と共に、エラーメッセージが表示されるので、ソースコードを修正します。

図 25-Messageウインドウのエラー表示

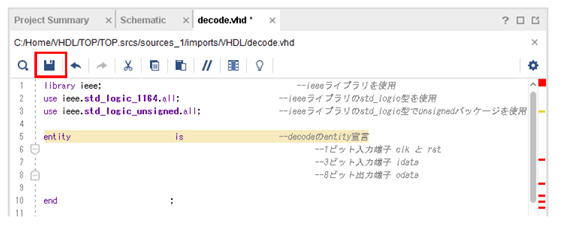

手順3:

ソースコードの修正後、ファイル保存します。

ファイルを保存する際、メニューバー : File – Save File Asを選択するか、

又は、 “保存”ボタン をクリックしてください。

図 26-Messageウインドウのエラー表示

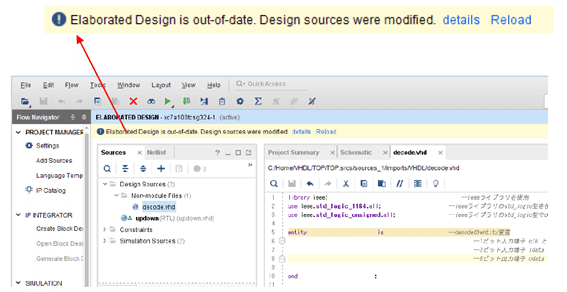

手順4:

デザインのリロード

ファイルを保存すると、デザインをReloadするか否か、問うメッセージがひょうされるので、Reloadをクリックします。

エラーが表示されたら、ソースコードを修正し、保存します。

図 27-Elaborate DesignのReloadメッセージ

手順5:

文法チェックOK

最後的に以下のように赤いエラーが表示されなくなれば、文法チェックOKとなります。

図 28-Message ウインドウの表示

![]()

作業を振り返って

![]()

今回の演習を通じて、組み合わせ回路を作成するときに使える if文とcase文、それぞれの違いが理解できたかと思います。

また、Vivadoで文法チェックする方法も理解できたかと思います。

筆者個人の感想として、気を付けなければならない点は、レジスタ設計なのでループ作成時には直接記述ができず、別の信号をカウンターとして作成してから、そのカウンターに対してループを作成しないといけないことです。

次回の演習(3)は「順序回路」です。

最後までお付き合いいただきありがとうございました!

次回もご覧ください。

この記事が気に入ったらサポートをしてみませんか?