Processor System Reset

Xilinx のFPGA開発ツールである Vivado では多くのIPが提供されています。

FPGAに備わった機能のうち、メモリーや高速シリアル等の特別な機能を使用するためのIPです。

逆に言えば、IPを理解し使い熟せないと、高級なFPGAの機能の大部分が使い物になりません。

そんなわけで何回かに分けて、個人的によく使うIPの説明をしていきたいと思います。

※ この記事はVivado 2019.2、及びProcessor System Reset 5.0を用いて説明を行います。

今回の Processor System Reset というのはリセット信号を分配するための IP です。

一見、そんな機能に IP を使う必要があるの? という感じですが、必要な幅のリセットを出力してくれるもので、Zynq とセットで使用されます。

Xilinx の開発ボードを使用するための Example Project を開いて見ると分かり易いと思います。

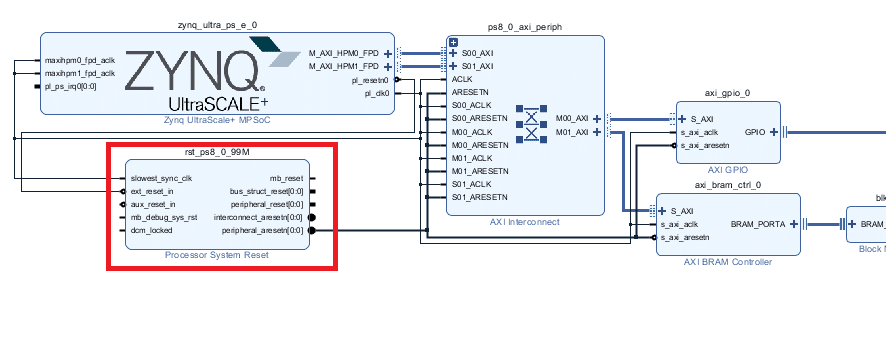

Zynq UltraScale+ ZCU102 Evaluation Board の Example Project で Block Design を貼っておきます。

この図の左下。赤い四角で囲んだものが Processor System Reset です。

図を見て分かるとおり、Zynq のクロックとリセット信号は、Processor System Reset に接続され、他の IP へのリセットは Zynq から 直接ではなく、Processor System Reset を経由して接続されます。

Zynq を使用する時には、このような接続が基本となります。

……まあ、簡単に言うと、こう接続してさえくれれば IP の説明なんて蛇足でしかありませんが、一応、解説します。

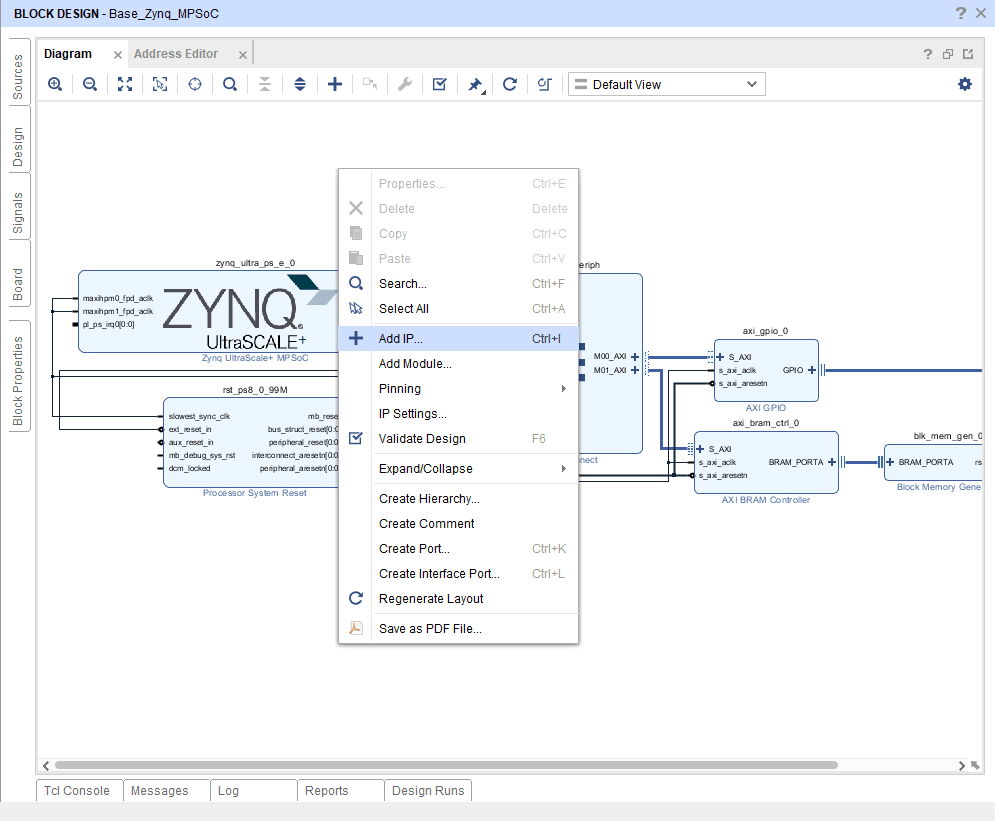

Processor System Reset を使うためには、他のIP同様、Vivadoでプロジェクトを開いた上で Block Design を開きます。

次に Block Design 上で右クリックをし、 Add IP を選択します。

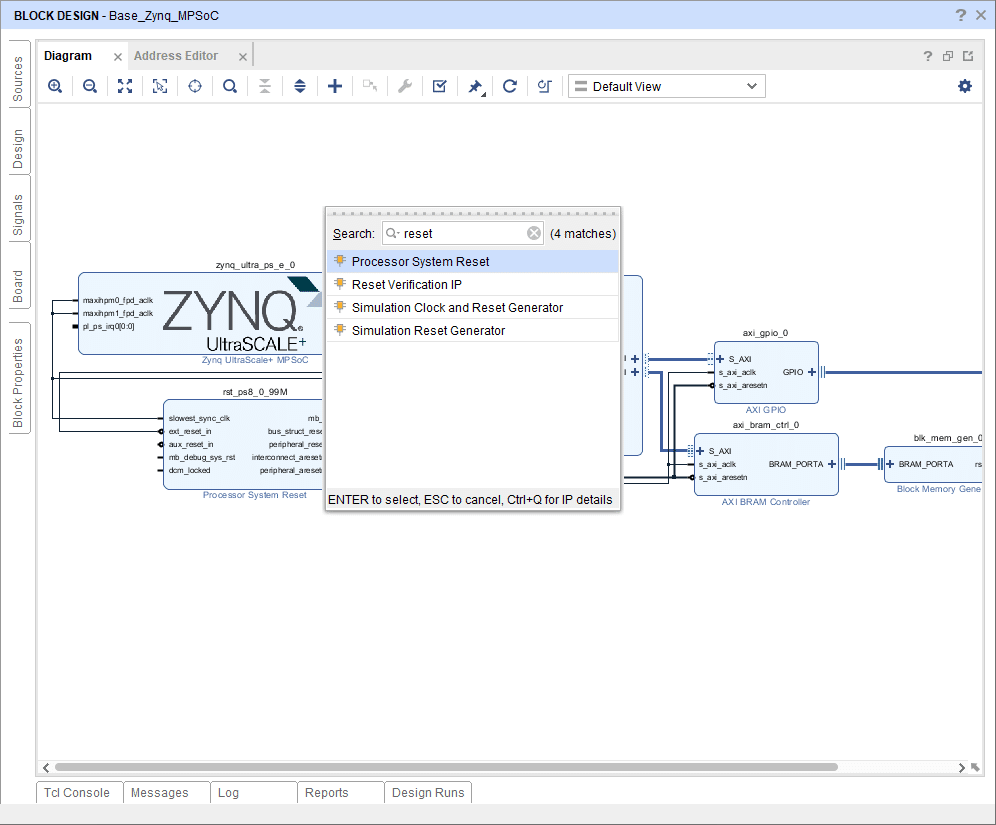

検索窓に reset と打ち込むと、簡単に Processor System Reset が見つかります。これを選択すると IP が作成されます。

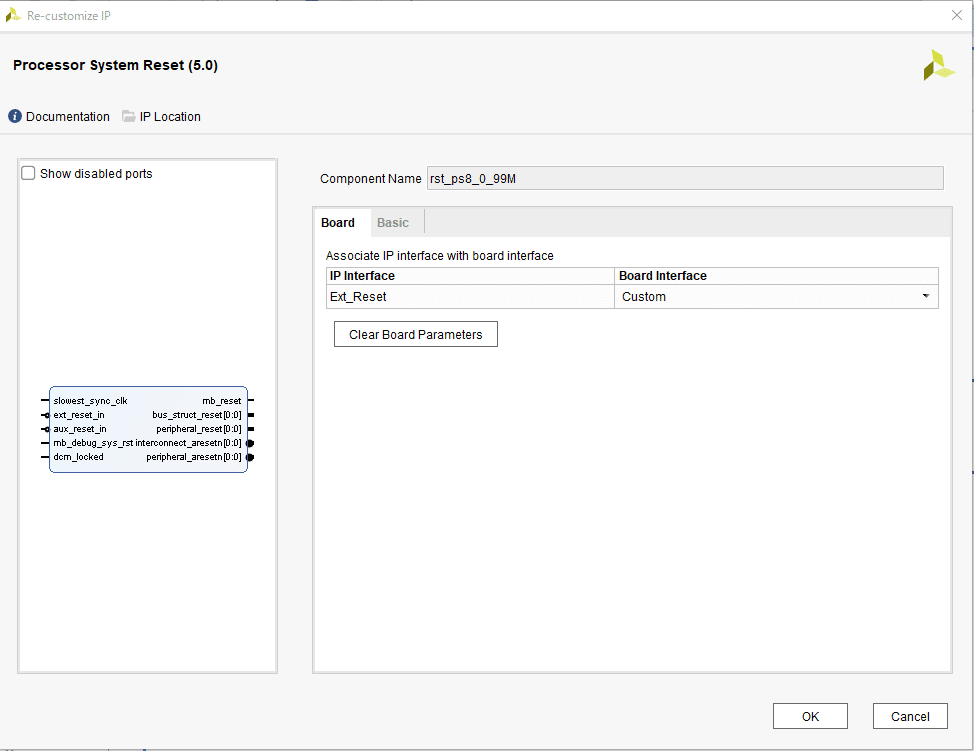

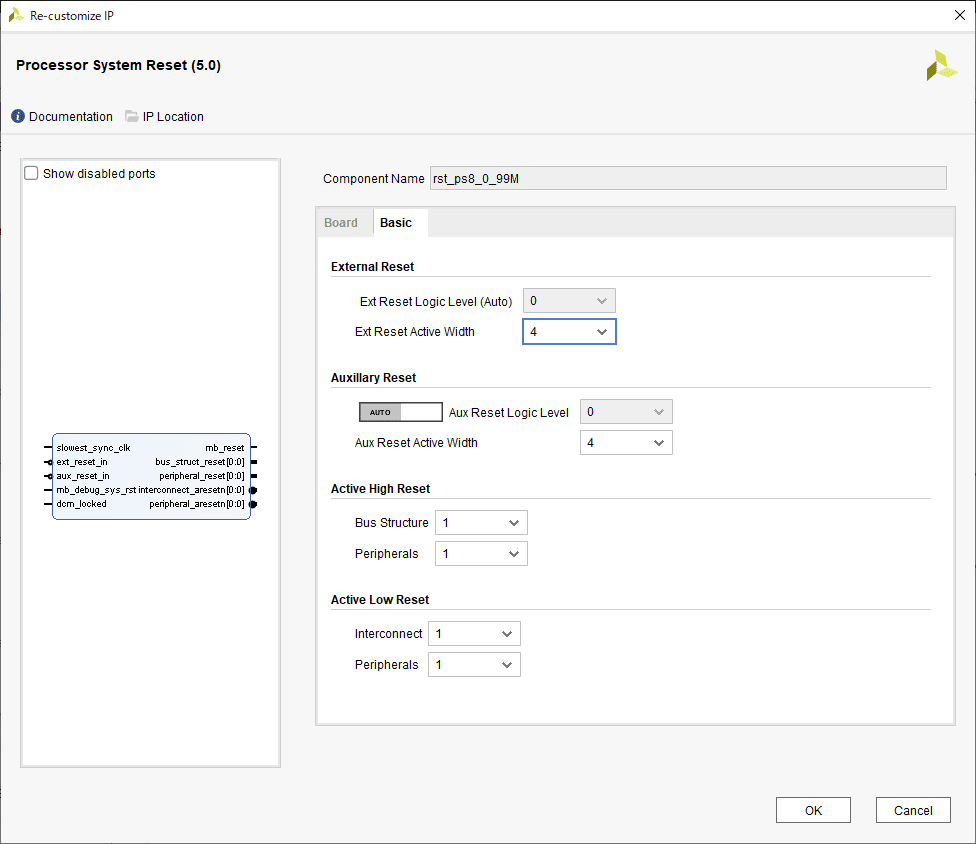

作成された IP は Design Block の適当な位置に配置されますので、ダブルクリックして設定を行います。設定が終わってからも、再びダブルクリックすることで設定を変更することが可能です。

1.Board

リセット信号の入力についての設定項目がありますが、デフォルトの Custom のままで問題ありません。

2.Basic

リセット入力、リセット出力の設定タブです。

External Reset

ext_reset_in 入力の設定を行います。

Ext Reset Logic Level (Auto) は1でリセットするのか、0でリセットするのかの設定です。リセット入力を Zynq に接続していると灰色になって入力出来ません。ここは自動的に正しいリセットのレベルを設定してくれていますので、そのままで問題ありません。

Ext Reset Active Width は反応するリセット信号の幅について設定します。

デフォルトの幅は 4 clk となっています。この値もデフォルト値のままで問題ありませんが、本当に正しいのか知りたい場合には Zynq のユーザーマニュアルでリセット信号の出力幅を確認してください。

Auxiliary Reset

aux_reset_in 入力の設定を行います。

Aux Reset Logic Level は1でリセットするのか、0でリセットするのかの設定です。AUTO 時には Block Design の接続先 IP に合わせて自動的に設定されます。MANUAL 時には自分で設定を行いますが、これは Block Design の外からリセット入力をする場合や、Block Design の中であっても、独自に作成したロジックから接続する場合に使用します。

Aux Reset Active Width は反応するリセット信号の幅について設定します。ここで設定した幅より短い幅のリセット信号には反応しません。

Active High Reset

リセット時1を出力するリセット信号の設定です。

それぞれ、bus_struct_reset 出力の信号幅を Bus Structure で、 peripheral_reset 出力の信号幅を Peripherals で設定します。信号幅が1bitでも普通に複数の IP に分配出来るので、ここを変更することは少ないと思います。

リセットの解除は、先に bus_struct_reset が、その後 16 クロックが経過してから Bus Structure の順番です。バス幅の設定はありませんが、 mb_resetは一番最後、更に16 クロック経過してから解除されます。

Active Low Reset

リセット時0を出力するリセット信号の設定です。

それぞれ、interconnect_aresetn 出力の信号幅を interconnect で、peripheral_aresetn の信号幅を Peripherals で設定します。信号幅が1bitでも普通に複数の IP に分配出来るので、ここを変更することは少ないと思います。

リセットの解除は、先に interconnect_aresetn が、その後 16 クロックが経過してから peripheral_aresetn の順番です。

以上。設定項目の説明をしてみましたが、変える場所というのはほとんどありません。複数ある出力のリセットが解除される順番だけ把握しておけばいいと思います。

この記事が気に入ったらサポートをしてみませんか?