6832 アオイ電子

半導体の組み立て、検査受託の会社。半導体の製造は大きく前工程・後工程に分けられますが、前工程の受託製造がファウンドリと呼ばれるのに対し、後工程を受託製造する企業はOSATと呼ばれるようです。

ファウンドリはほぼTSMCの独壇場で、TSMC一社で50%以上のシェアを占めています。

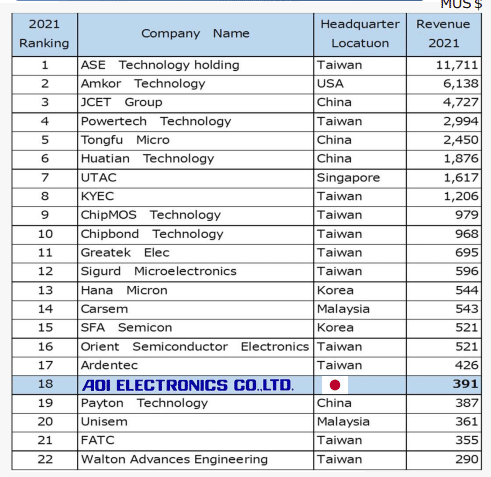

OSATの方も台湾勢が強いのは変わりませんが、一位でもシェアは25%以下に過ぎず、ファウンドリと比較すると大きな企業が存在しています。

日本から唯一OSATの売上ランキングにランクインしているのがアオイ電子です。このデータを見ただけでは唯一の日本企業とはいえ世界では弱小で、泡沫半導体企業の一つにしか見えませんが、技術的な特徴があるようです。

半導体はこれまで微細化を進めることで高性能化を図ってきました。最近では線幅2nmの半導体が話題になっていますが、微細化による高性能化はそろそろ限界に近付いているようです。線幅は当然原子よりも小さくすることはできないわけですが、銅原子の原子半径(ファンデルワールス半径)は128pm(=0.128nm)です。つまり、線幅2nmというのは回路の幅方向には銅原子が15~16個しか並んでいないことになります。

微細化の余地が全くないわけではないでしょうが、限界は精々ここから半分くらいで、どう頑張っても1/10にはできなさそうです。

では今後どうやって高性能化していくか?の一つの答えがアオイ電子の技術です。

通常、ICチップ上にはすべての構成要素を載せて接続するようですが、アオイ電子の技術では機能や構造の異なる構成要素をブリッジというもので接続して集積度を上げるというもののようです。

素人が見るとなぜこんなシンプルなことが今までできなかったの?という感じなのですが、半導体の線幅が狭すぎるため、他の構成要素と接続する際の組立精度がシビアになり過ぎ、現実的に製造できない、ということのようです。これは構成要素やブリッジの回路を別々に描画してから組み立てるから発生する問題であり、アオイ電子ではあらかじめチップレットを組み立ててから回路を描画することを考えているようです。こうすれば組立精度の問題は解決できます。

これだけ聞くと、割と小さい企業が画期的なブレイクスルーの方法を開発したということで夢があるのですが、恐らく色々と問題もあるんだろうと思います。

アオイ電子は受託製造なので、この技術を前提設計してくれる半導体設計会社が別に必要。その設計をしてくれる会社はあるのか?

複数の構成要素を組み立てた状態で回路の描画(露光)が可能なのか?半導体製造装置側には何も工夫をしなくても良いのか?

本来、回路の描画は前工程の領域であり、ファウンドリの所掌である。アオイ電子の技術が実現すればファウンドリも含めて製造の手順や所掌が変わるが、それは業界として許容されそうなのか?

アオイ電子がこの技術で本当に飛躍できるのかは正直なところ不明ですが、課題やその解決方法は非常に実務的だと思いました。

この記事が気に入ったらサポートをしてみませんか?