XLS: Accelerated HW Synthesisとは

概要

Googleが提供するEDA(半導体設計ソフトウェア)らしいです。Facebookの友人から紹介されました。

調査してみよう。

XLSは、高レベルの機能記述から合成可能な設計(VerilogおよびSystemVerilog)を生成する高水準合成ツールチェーンを実装しています。これはApache 2ライセンスのもとで提供されています。

**XLS(Accelerated HW Synthesis)**は、ムーアの法則の終わり(EoML)時代に向けたソフトウェア開発キット(SDK)を目指しています。この「特化の時代」において、ソフトウェアエンジニアとハードウェアエンジニアは、ドメインの境界を越えてより多くの共同設計を行う必要があります。共有されるアーティファクトを協力して作成し、お互いのコストモデルを理解し、ツールや手法を共有することが求められます。XLSは、この全体のプロセスを加速するために、自動化、ソフトウェアエンジニア、およびマシンサイクルを活用することを目指しています。

XLSは、ハードウェアIPの迅速な開発を可能にし、ホストソフトウェアとしても効率的に動作します。XLSの設計は、ホストソフトウェアまたはシミュレータでネイティブ速度で動作し、同時にハードウェアブロック出力も生成できます。XLSツールの正確性は、(形式的に検証するためのツールも提供しつつ)それらが機能的に同一であることを保証します。

XLSは、(オプションでパイプライン化された)純粋なワイヤI/Oインターフェースを持つ関数や並行処理(プロセス)をサポートします。プロセスは状態を持ち、時間の経過とともに誘導を行うことができ、より一般的な通信インターフェースを含みます。

参考リンク

XLSとは

Linux上で動作する

Condaでも動作可能

コマンドラインツール

自動パイプライン合成

他は?

XLSのインストール

Conda-eda環境でインストール、テストしてみよう

加算器の設計はこうると。

fn adder1(a: u1, b: u1) -> u2 {

let n: u2 = a as u2 + b as u2;

n

}

fn user_module(io_in: u8) -> u8 {

adder1(io_in[0:1], io_in[4:5]) as u8

}

#[test]

fn test() {

let _ = assert_eq(adder1(u1:0b1, u1:0b1), u2:0b10);

let _ = assert_eq(user_module(u8:0b0001_0001), u8:0b000000_10);

_

}参考。乗算器では

パイプライン化は自動でやってくれるそうです。

fn mul4(a: u4, b: u4) -> u8 {

u8:0 // TODO(YOU) implement mul4

}

fn user_module(io_in: u8) -> u8 {

mul4(io_in[0:4], io_in[4:8]) as u8

}

#[test]

fn test() {

let _ = assert_eq(mul4(u4:8, u4:8), u8:64);

let _ = assert_eq(user_module(u8:0b1000_1000), u8:0b0100_0000);

_

}合成、SImはエラーでうまくいかないようです!

一旦はここで中止

所感

大学4年生の時からVerilogを使っていて、XX年ずーと変わらない言語にむしろ驚いてました。ソフトウェアの世界ではC++、Java、Pythonと変化してるのに変わらないVerilog。今まで何度か流行したC言語ハードウェア設計。あれは、ほぼ役に立ちません。

ここらで主流設計言語がかわるのもいいでしょう。

さらに、Googleでは

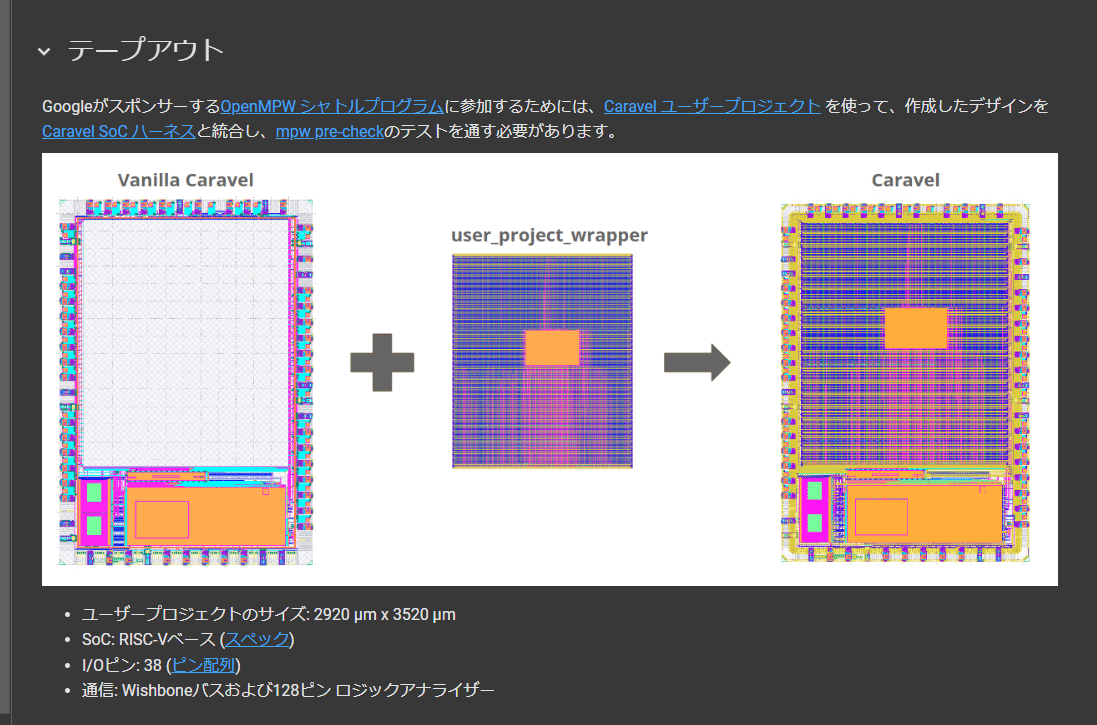

設計データで実物LSIを製造してくれるようです。

おいくらなのでしょうか?←無料だそう

設計データはオープンにしろと。応募してみようかな?

(業界の人には常識なのでしょうが)