【How we innovate】02:半導体の製造プロセスとASMLが誇る露光技術

こんにちは、エーエスエムエル・ジャパンです。

この記事では、ASMLに興味を持ってくださった読者のみなさまへ、

「私たちが生み出してきた”イノベーション”を知っていただきたい。」

「より深くASMLのことをご理解いただきたい。」

そういった思いから、半導体の歴史や私たちが作る”露光装置”について、解説する内容となっています。半導体がどのような仕組みで、どんな工程で作られているのか。そしてASMLは半導体業界にどのようなイノベーションを起こしてきたのかについて、3部に分けてご紹介していきたいと思います。

第1回の記事「半導体はなぜ微細な構造を必要とするのか?」はこちら

第2回は「半導体の製造プロセスとASMLが誇る露光技術」についてです。半導体の製造において、最も高い精度を求められるプロセスが”露光”。今回の記事では半導体全体の製造プロセスをなぞりながら、ASMLが誇る露光技術の重要性について解説していきます。

今回の記事は、ご自身も半導体業界でご活躍されながら、半導体関連の著書『「半導体」のことが一冊でまるごとわかる』(共著、ベレ出版)も出版されている蔵本貴文氏に執筆いただきました。

半導体の製造プロセスは長く複雑で、それぞれの工程に高度な技術が用いられており、先端テクノロジーの塊とも言われるものです。

この記事では、半導体製造の全体の流れから始め、前工程と呼ばれる微細な回路をシリコンウェハの書き込む工程を詳しく説明します。さらに前工程の中で中心的なリソグラフィー工程についてお伝えし、最後にASMLの露光装置がどのように活躍しているか、をお伝えしたいと思います。

半導体の製造プロセス全体

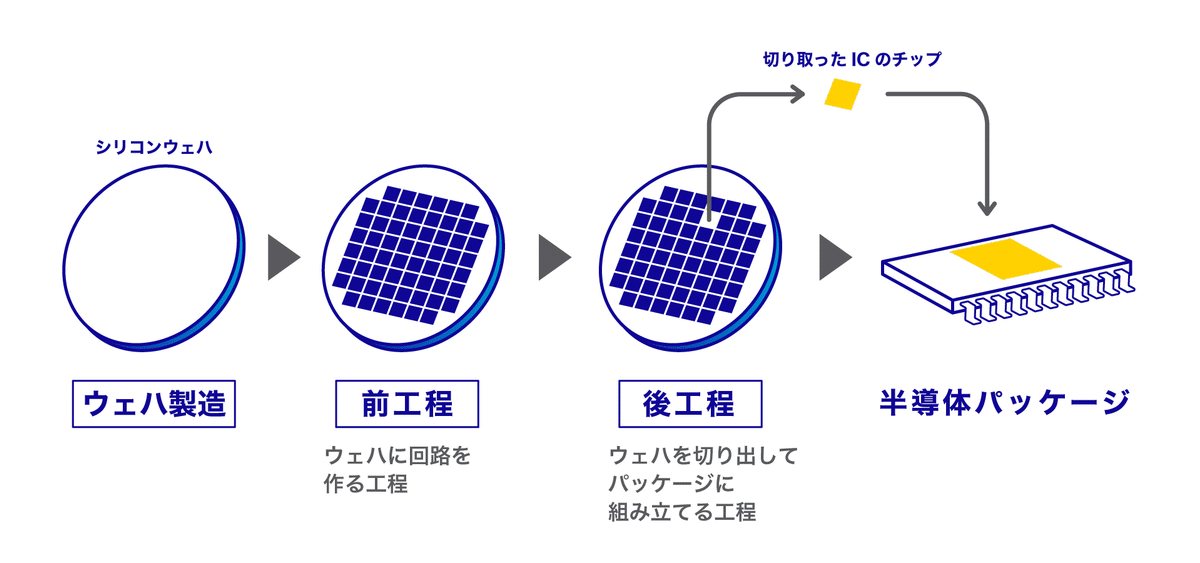

半導体の製造を大きく3つにわけます。最初は原材料であるシリコンウェハの製造、次に前工程と呼ばれるウェハに回路を作る工程、最後に後工程と呼ばれるウェハを切り出してパッケージに組み立てる工程です。

このそれぞれのプロセスについて説明します。

シリコンウェハ製造

半導体の回路はシリコンウェハの上に作られます。この原材料のシリコンはガラスから得られ、地球上に大量に存在しています。しかし半導体製造に使うウェハは、イレブンナインと言われる99.999999999%の純度、9が11個並ぶ純度が必要となります。さらに、ナノメートル(1マイクロメートルの千分の一)の精度で加工されるものですので、表面の凹凸も、原子レベルで抑える必要があります。

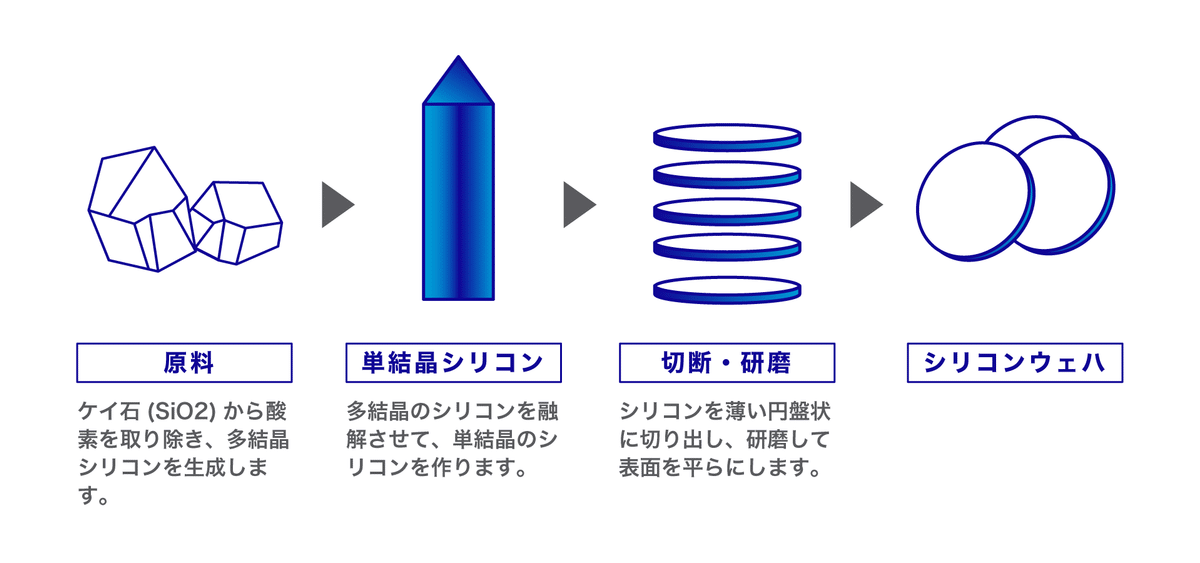

下の図にシリコンウェハの製造工程を簡単に示しています。

■ 原料

原料はケイ石(SiO2)です。これはガラスの原料で簡単に得られます。このSiO2を還元(酸素の除去)して、多結晶シリコンを生成します。

■ 単結晶シリコンの製造

多結晶のシリコンを融解させて、単結晶のシリコンを作ります。これは純度が非常に高い(99.999999999%以上)大きなシリコンの塊です。これを「インゴット」とも呼びます。

■ 切断、研磨

得られたインゴット(単結晶のシリコンの塊)を円盤状のウェハに切り出します。多くのウェハは直径が300mmの円形で薄さは0.8mmほどです。表面を1nmレベルの凹凸に仕上げるために、研磨して表面を平らにします。これでウェハの完成です。

前工程

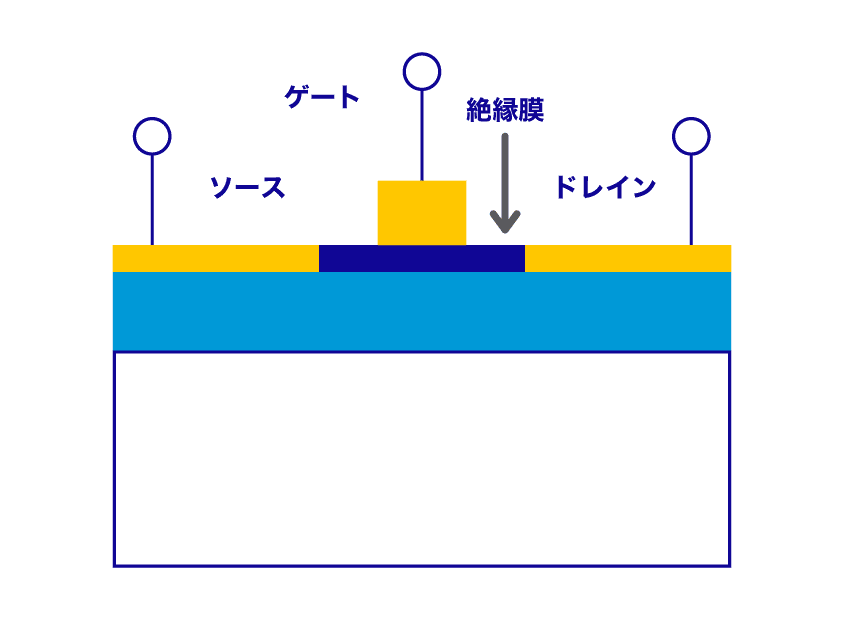

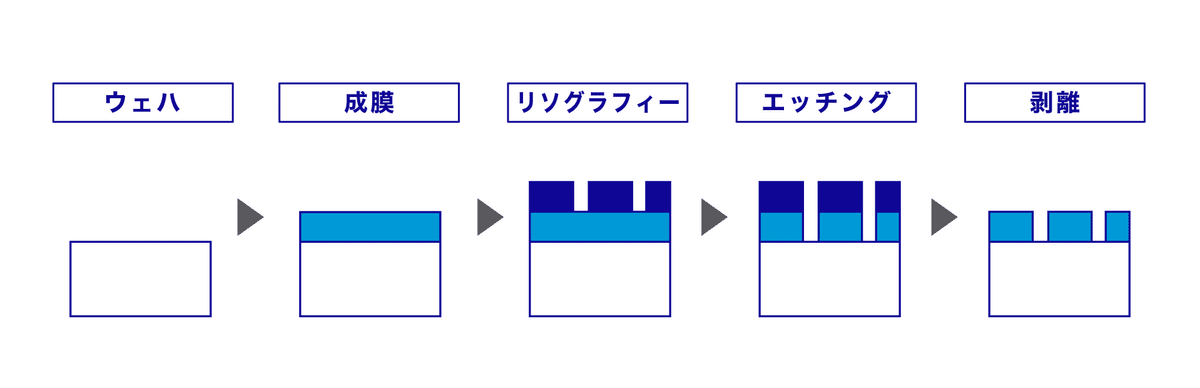

前工程では、ウェハにさまざまな成膜技術とパターニング技術を利用して、MOSFETと呼ばれる素子や配線を形成します。この半導体前工程では、リソグラフィーという技術を用いて、ナノレベルの微細加工がおこなわれます。

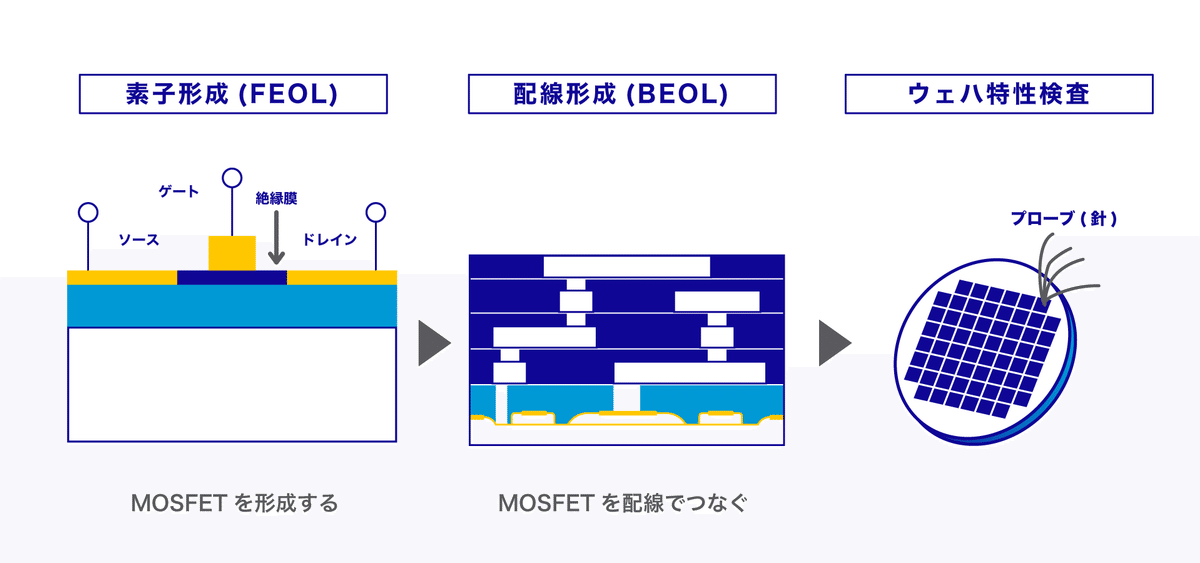

前工程は大きく2つに分けられます。

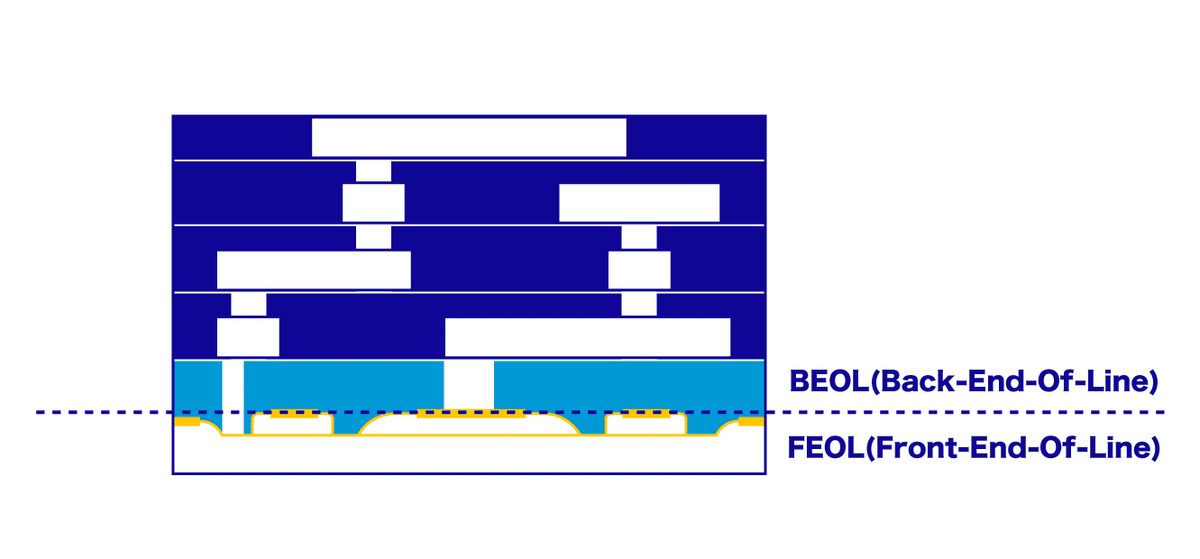

1つ目はウェハにMOSFET(モスエフイーティー)と呼ばれる電流を制御する素子を形成する工程です。これをFEOLという工程(Front-End-Of-Line)と呼びます。もう1つはそのMOSFETを配線でつないで回路を形成するBEOL (Back-End-Of-Line) という工程です。これでウェハ工程は完成になります。最後に検査をして、期待通りの動作をするか確認します。

■ FEOL工程

この工程でMOSFETと呼ばれる、電流を制御するスイッチの役割を果たす素子をウェハに作りこみます。

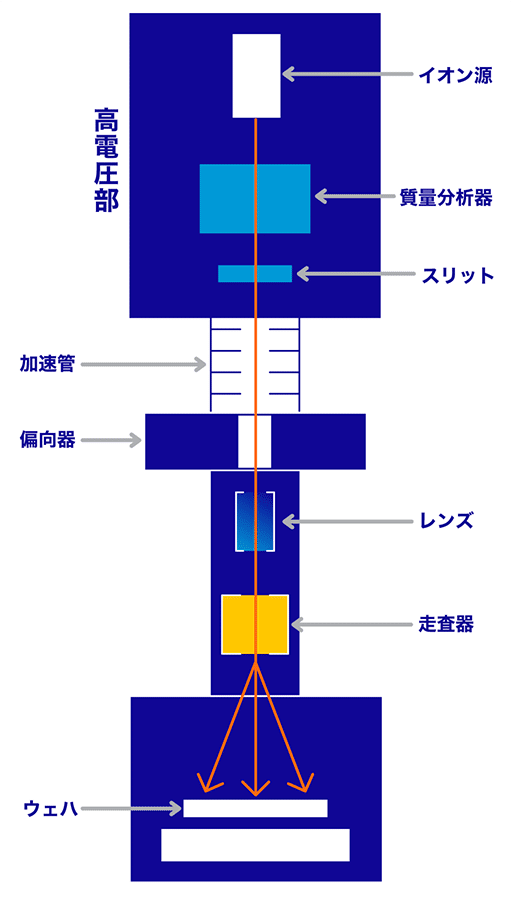

99.999999999%の純度のウェハはほとんど電流を流しませんが、微量の不純物原子を入れることで電流を流せるようになります。不純物は主にイオン注入と呼ばれる方法で注入します。これはイオンを鉄砲玉のように飛ばしてウェハに注入する方法です。

微細構造の形成にはリソグラフィーと呼ばれる技術を使います。半導体工程の中でも最も微細な構造はゲートです。ですから、最も精度が必要となるのがMOSFETのゲートを形成する工程になります。

■ BEOL工程

BEOL工程では、FEOLで形成したMOSFETを金属配線でつなげて、回路を形成します。回路は非常に複雑で、1層だけでは必要な配線ができません。ですので、ビアと呼ばれる上下層を繋ぐ配線を使いながら、3次元の配線を形成します。最先端の半導体製品ではこの配線が10層程度に及ぶこともあります。

配線金属は蒸着と呼ばれる技術やめっきの技術でウェハ上に堆積されます。配線パターンを形成するのは、リソグラフィー技術です。配線パターンが形成されたら、その上に絶縁膜(SiO2;ガラス)を堆積させた後にビアを形成して、上層配線を形成します。最上層には後工程でボンディングワイヤーを圧着させるため、特に厚い配線が使われます。

■ ウェハ特性検査

最上層の配線まで完了すると、ウェハの工程は完了です。ここで作られたチップ(1製品の領域のウェハ)が期待された動作をするかチェックします。完全な製品ではないので、ウェハ上にプローブと呼ばれる針を当てて、電気特性のチェックをします。

後工程

半導体製品というと、パソコンの内部に存在する黒いものをイメージする人が多いと思います。チップをその黒い物で覆うのが後工程です。後工程では、ウェハをチップに切り出し(ダイシング)、そのチップを黒い樹脂で固めて端子を出します(パッケージング)。最後に動作のテストをして、出荷可能な半導体製品となります。

■ ダイシング

ウェハを四角いチップに切り出します。ただ切るだけと思われるかもしれませんが、チップ内部にダメージが少なくなるように切り出すことは非常に高い技術が必要です。また、ウェハを研磨して薄くする作業が行われることもあります。

■ パッケージング

パッケージングは大きく二つの工程に分けられます。まずは、チップとパッケージの端子を繋ぐワイヤボンディングという工程、そしてチップを黒い樹脂で覆うモールディングと呼ばれる工程です。この工程を経て、見慣れた黒い半導体製品になります。

■ テスト

最後に出来上がった半導体が正常に動作するかテストして、出荷できる製品となります。初期不良を起こす個体を検出するために、高電圧、高温などストレスのかかる環境に置いてからテストを行う、バーンインと呼ばれる工程を経ることもあります。

微細化のキーとなる前工程

先ほど紹介した中でも、前工程は半導体製造プロセスの中心的な部分となります。半導体はナノレベルの加工精度という話をしましたが、その加工精度は前工程で実現されるのです。

最先端製品だと、前工程の工場を作るのに億の単位では収まらず、兆のレベル(円換算の場合)の資金が必要になります。また工程も1000工程を超え、ウェハが完成するのに3ヵ月程度かかる場合もあります。まさに人類が製造するものの中で、トップレベルの複雑さを持つ工程と言えるでしょう。

ここでは、その前工程の内容について解説します。前工程ではウェハに、成膜技術とパターニング技術を利用して、微細な回路パターンを形成します。

■ 成膜

成膜工程ではウェハ全面に膜を成膜します。例えば、絶縁膜(ガラス)を成膜するときにはCVD(化学気相成長)という方法が使われることが一般的です。これは複数のガスを加熱したウェハ上に流して、化学反応を起こして成膜する方法です。

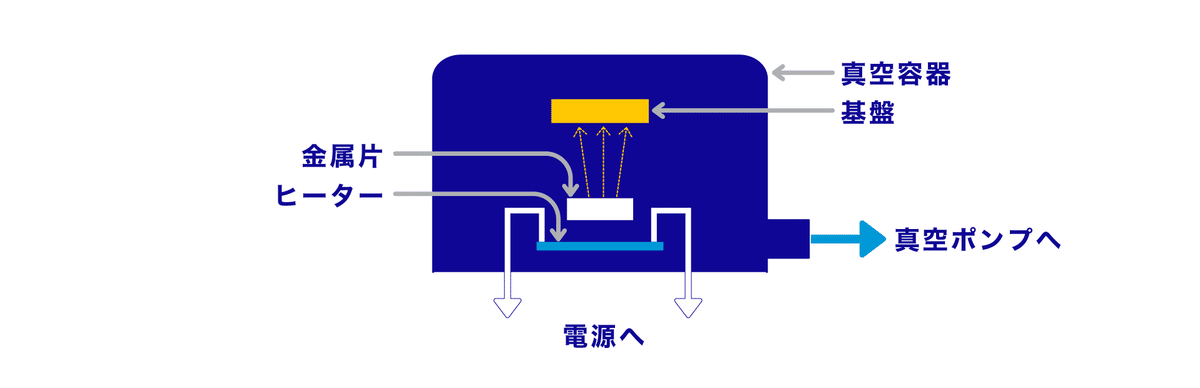

金属のパターンを形成する時には、まずウェハ全面に金属の膜を着けます。この金属の成膜の方法としては、スパッタリングという方法が使われることが多いです。スパッタリングとは、下に示すように、真空にした容器内で金属を加熱して蒸発させ、ウェハ上に堆積させる方法です。

現在の工程ではウェハの直径は300mmが一般的ですが、ナノレベルの構造を生成するためには、そのウェハ全面での膜厚のばらつきをナノレベルに抑える必要があります。

■ リソグラフィー

リソグラフィー行程は、後で詳しく説明するのでここでは簡単に概要をお伝えします。

まずレジストと呼ばれる膜をウェハ全面に塗布します。そして、欲しい回路パターンが書いているフィルムのようなもの(レチクルと呼ばれます)を通して光を当てます。レジストは光が当たった部分が変質して、薬液に溶けやすくなります。このレジストを薬液につけると、光を当てなかった部分のレジストが選択的に残るわけです。こうして微細な構造を形成します。

■ エッチング

薬液などで、最初に成膜した膜を取り除く工程です。この時にウェハの上にレジストがあれば、レジストの下の部分は保護されて残ります。ですから、狙ったところだけの膜を取り除くことが可能になります。

薬液でエッチングすることをウェットエッチングと呼び、これに対してドライエッチングという技術もあります。これはプラズマを使って、物理的に膜を取り除く方法です。

■ イオン注入

ウェハ上にMOSFETなどの素子を形成するために、シリコンに不純物を打ち込む工程がイオン注入です。下のような装置で、P(リン)やAs(ヒ素)、B(ホウ素)といった原子を真空中でイオン化させ、これを高電圧で加速してウェハに打ち込みます。

注入が不要な部分にはレジストを残しておくことにより、狙った場所に不純物を注入することができます。

この他にも半導体製造にはたくさんの工程が存在します。まずこれらの工程ごとに、ウェハを洗浄する工程が必要になります。洗浄といっても前工程の中では微小なゴミも許されないし、洗浄後の乾燥もうまく行わないと、ウォーターマークという不良の原因になります。通常、私たちが考えるレベルの洗浄とは、はるかに高いものが要求されるのです。

ウェハを加熱する熱処理の工程も重要です。ウェハ内の不純物の分布を正確に制御するために、わずか1秒で100℃温度を上昇させるなど、普通の感覚とは大きく異なるレベルの熱処理が行われます。さらに、300mmのウェハの温度を均一に熱する必要があるので、その制御は非常に高いレベルになります。

また、各工程で狙い通りの品質が保たれているか、確認する検査も重要です。成膜した膜の厚さを測ったり、パターンのズレ量をナノレベルで計測したり、微小なゴミがないか調べたりと、非常に高い精度が必要となる装置ばかりです。

このような高精度の工程を経て、ようやくウェハが完成するわけです。

リソグラフィー技術の重要性

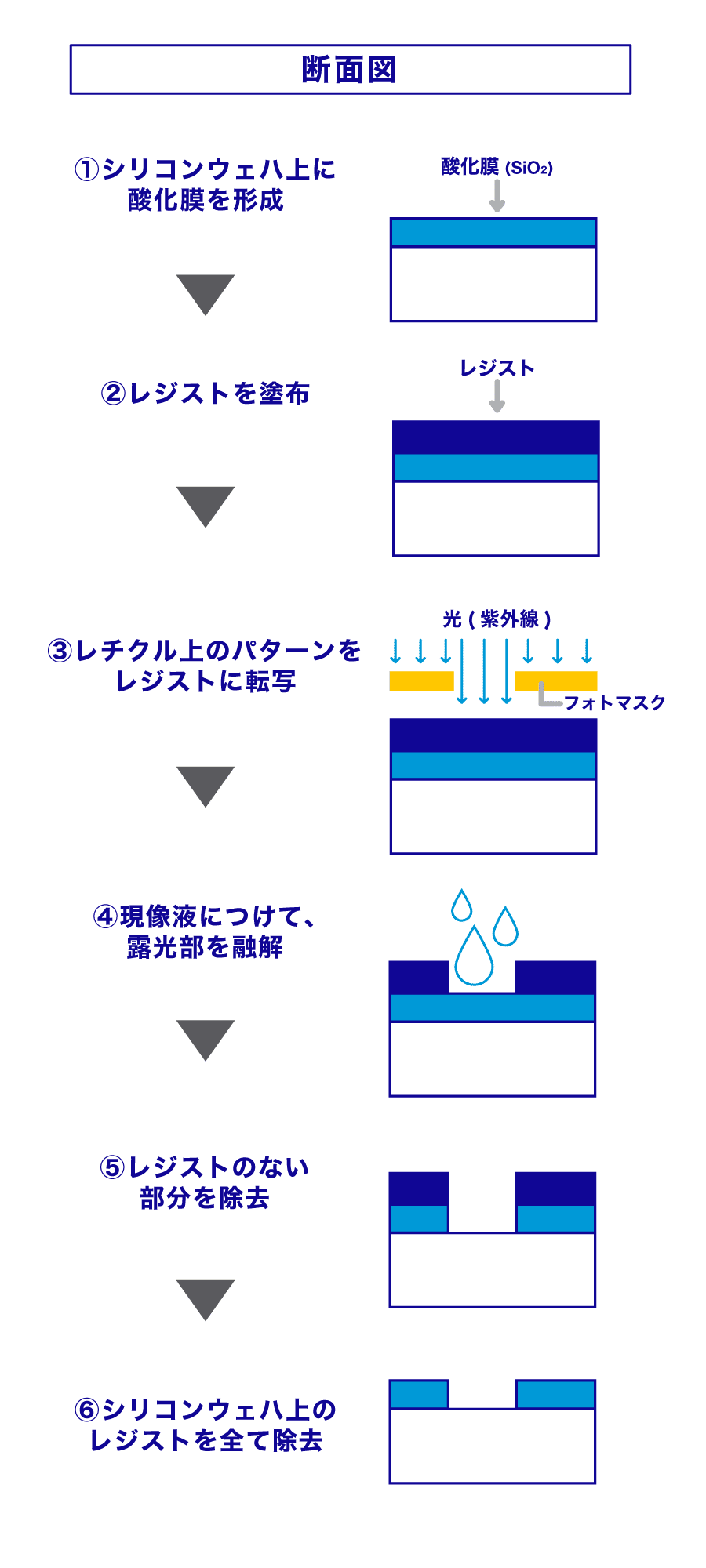

前工程の中でも、リソグラフィー工程は特に重要なステップです。リソグラフィー行程は微細なパターンをシリコンウェハ上に正確に転写することが目的です。この工程は主にレジスト塗布、露光、レジストの現像、レジストの剥離のステップから構成されます。

以下に、酸化膜上にパターンを形成する例を通して、リソグラフィーのプロセスを詳しく説明します。

① 酸化膜が形成した状態

今回は酸化膜にパターンを形成する工程ですので、まずシリコンウェハ全面に酸化膜がある状態からスタートします。

② レジストの塗布

ウェハの酸化膜の上に、レジストと呼ばれる感光性の薬品を塗布します。

③ 露光

露光はレチクルを通してウェハに光を当てる工程です。レチクル上のパターンがレジストに転写され、レジストの化学構造が変化します。

④ 現像

露光したレジストがついたウェハを、現像液と呼ばれる薬液につけます。すると感光して化学構造が変化した部分だけが選択的に溶解します。つまり、レチクルのパターンがレジストを通じて、ウェハ上に転写されたことになります。

⑤ エッチング

この状態でエッチングをします。するとレジストがない部分が選択的に除去されるので、酸化膜上にレジストのパターンが転写されることになります。今回はエッチングでしたが、ここでイオン注入を行えば、選択的に不純物を注入することも可能になります。

⑥ 剥離

最後に露光させなかった部分(化学構造が変わっていない部分)も融解する薬液を使って、ウェハのレジストを全て取り除きます。

この①~⑥のプロセスにより、レチクルのパターンをウェハ上に作成することができるわけです。

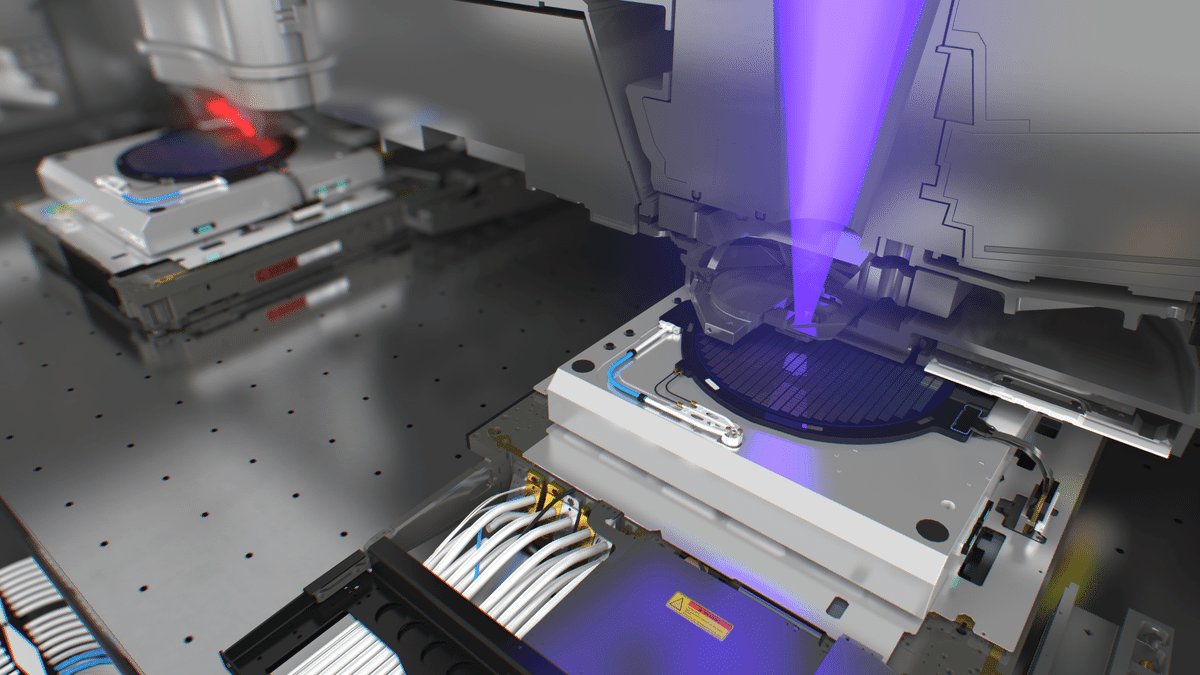

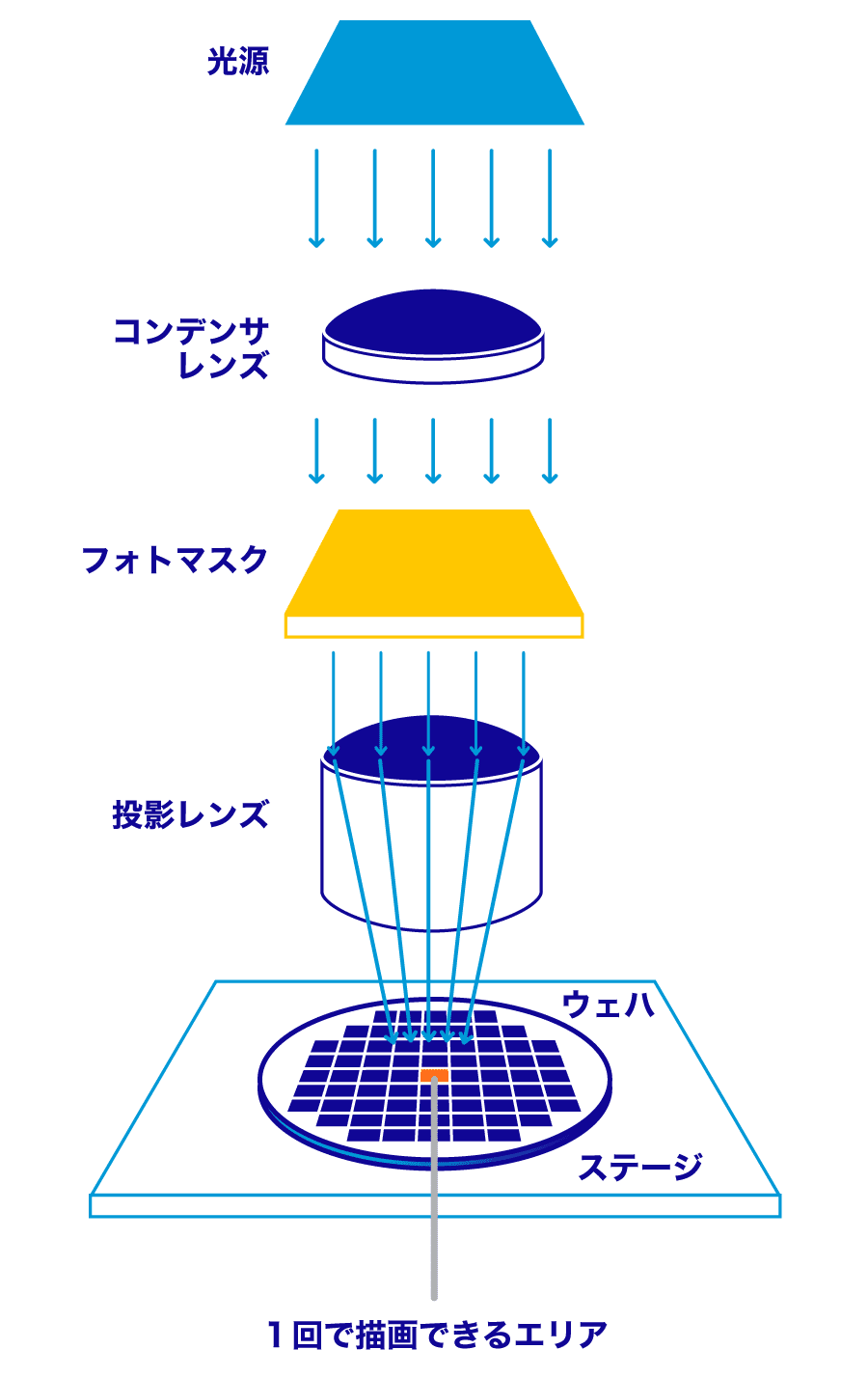

この中でも、露光工程は半導体製造の中で最も精度が必要な装置とされています。一般的な露光装置の詳細を図に示します。

露光機はこのような構成になっていて、光源からの光を2枚のレンズを通してレチクルのパターンをウェハ上に照射します。光学系で縮小されるので、実際はレチクルに描かれたパターンは1/4程度に縮小されます。

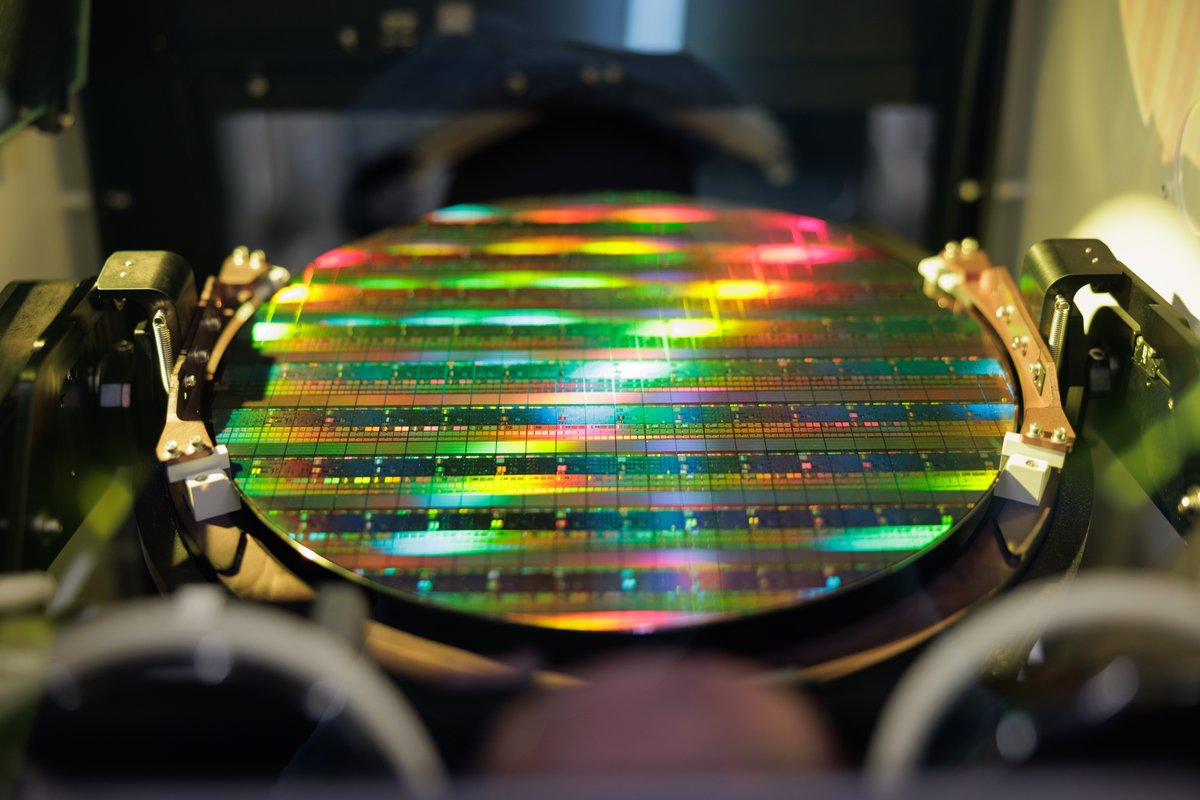

1枚のウェハは20mm四方程度の数十個のショットに分けられて、これが1回の照射で露光されるエリアになります。ですから、ウェハ1枚の露光ではステージを動かしながら、数十ショットを露光することになります。当然、そのステージの移動の精度もナノメータレベルに抑えることが重要になります。

このように精度の高い装置なので、露光装置は効果な設備が並ぶ前工程の半導体工場の中でも最も高価な装置になります。また、微細なパターンを描くレチクルも高度な技術が必要となるので、先端プロセスでは1枚数億円になることもあります。

ASMLの露光技術

ASMLは露光装置の世界1のベンダーであり、その技術は高い評価を受けています。以下に、ASMLの露光技術に関するポイントを2つ紹介します。

1. 高い解像度

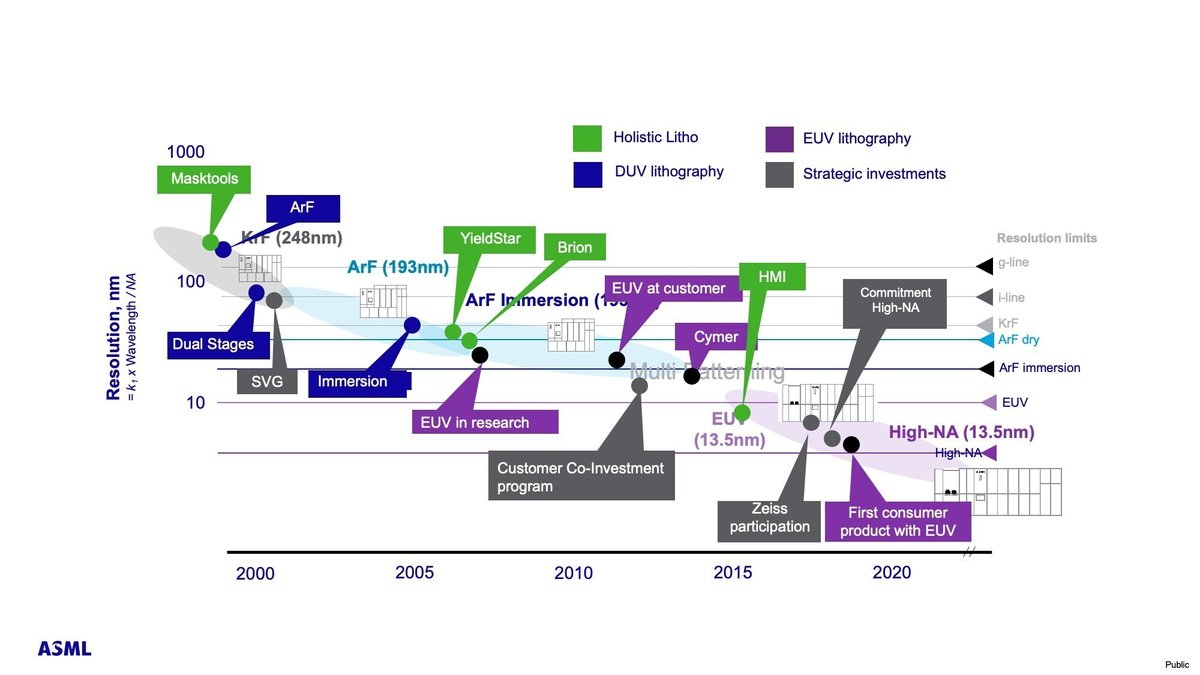

より微細なパターンを転写するために、物理的な限界となるのは光源の波長です。光は、その波長程度の大きさのパターンしか露光できません。ですから、光源を短波長化することが重要になります。

半導体は微細化の歴史を辿っていますが、下の図に示すように、その歴史は露光装置の進化の歴史です。光源の短波長化によって、微細化が進んできました。

ASMLはこの微細化のリーディングカンパニーです。上の図に示すArF液浸(Immersion)は液浸を必要とする半導体メーカーのほとんどで採用されており、EUVに至っては装置を出荷できる会社は世界にASML一社です。EUVとは約13.5nmという短い波長の光源を使用して、微細なパターンをシリコンウェハに転写するもので、5nm以下の先端ノードにおいて必須の技術となっています。

2. 高い生産性

先ほど説明したように、露光工程には高価な設備が必要です。よって、露光装置ができるだけたくさんウェハを処理できることが、工場の生産性向上に重要になってきます。

ASMLはTwinScan技術と呼ばれる、露光と測定のステージを別々にする技術を他社に先駆けて実用化し、その露光装置は高い生産性を実現しています。これが半導体メーカーがASMLの装置を選ぶ大きなポイントとなっています。

ASMLの露光技術は、半導体産業の進歩を支える基盤となっています。その技術は、半導体デバイスの性能向上とコスト削減に貢献して、現代社会の進歩を支えているのです。

エーエスエムエル・ジャパンでは、年間を通してエンジニアの採用を行っています。興味をお持ちになった方は、ぜひ弊社HPをご覧ください。

■ エーエスエムエル・ジャパン採用情報

■ ASML日本法人サイト(エーエスエムエル・ジャパン)

■ ASMLグローバルサイト