GF180レイアウト設計: 基板・ウェルの扱い

この記事ではレイアウト設計で特に分かりにくい基板・ウェルの扱いについて,GlobalFoundries 180 nm プロセスを題材に説明します.

レイアウトと製造工程の基本的な事項は以下の記事を参照してください.

1.基本のおさらい

基板・ウェルの挙動の話をする前に,半導体の性質についておさらいしておきます.

1.1 n型半導体

シリコンにドナーをドーピングして電子が余っている半導体.ドナーの数だけ自由電子があるので,金属ほどではないですが導電性を持ちます.GF180では nwell (nウェル),dnwell (ディープ nウェル),nplus+comp (nplus と comp のオーバーラップしている領域) の3つで,このうち nplus+comp はドーピングの濃度が高い領域です.nwell と dnwell の違いについては後ほど.また,nplus+comp と書くのは面倒なので,この記事では以後 nplus と書いたら nplus+comp のことということにします.

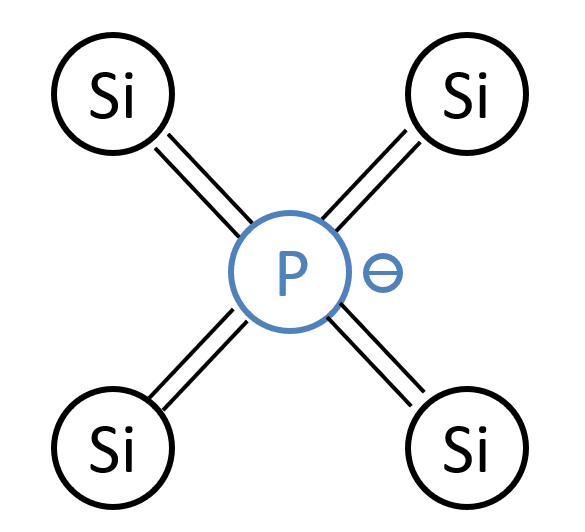

1.2 p型半導体

シリコンにアクセプタをドーピングして電子が足りない半導体.アクセプタの数だけ電子が足りない「穴」,つまり正孔ができます.正孔がキャリアとなるので n型半導体と同じく導電性を持ちます.シリコンウェハはまず全体がp 型半導体にされますので,何も加工されていない領域はすべて p型半導体となります.この何も加工されていない領域が基板 (substrate) で,p型であることを表すために p-sub と呼ぶことが多いです.「何もしていない領域」なので,レイアウト設計で p-sub のレイヤーはありません.レイヤーがある p型の領域として,GF180 では LVPwell (pウェル),pplus+comp の2つがあります.n型と同じく,pplus+comp が高濃度の領域です.pplus+comp も面倒なので以後 pplus と書きます.

1.3 pn接合,空乏層

p型とn型を接合すると,接合面付近の電子と正孔が再結合して接合面近傍のキャリアがなくなります.これが空乏層 (depletion layer) で,絶縁膜だと思ってください.つまり,n型半導体とp型半導体はそれぞれ導体ですが,貼り合わせるとその接合面には絶縁膜ができて n型と p型の間では導通しません.

ただし,この絶縁膜は決まった方向に電圧をかけると簡単に消滅します.p型を高い電位,n型を低い電位にするよう電圧をかけることを順バイアスと呼び,ある決まった電圧 (順方向電圧) 以上の順バイアスをかけると,空乏層が消えてp型とn型の間が導通します.この状態を「pn接合が ON する」と言ったりします.順方向電圧はシリコンでだいたい 0.6 Vです.

一方,p型を低く,n型を高くする電圧のかけ方が逆バイアスで,こちらは空乏層が維持されますので,逆バイアスはいくらかけても電流は流れません.(もちろんブレイクダウンするまで電圧をかけたら流れますが)

MOSFET における pn接合は,すべて空乏層が維持されていなければなりません.MOSFET において pn接合が導通したらそこには想定外の大電流が流れますので,高い確率でデバイスは破壊されます.空乏層は死守しないといけないのです.基板・ウェルの扱いにおいて第一にすべきことはこの空乏層を維持することです.

1.4 MOSFET の構造

プレーナ型MOSFETの断面は下のような構造です.

nMOSFET は p-sub の中に作られた nplus の ソース・ドレイン領域の間に,ゲート電界によってn型のチャネルを作ることで導通させます.電流はドレインの nplus → n型チャネル → ソースの nplus のように,n型の領域のみを通って流れます.もし p-sub と nplus が ON したら電流は p-sub に流れてしまうので,p-sub と nplus/n-channel の間は空乏層で絶縁されていなければなりません.つまり,p-sub の電位は少なくともソース・ドレインと同じか低い電位である必要があります.

pMOS も同様で,pplus と nwell の逆バイアスを維持するために nwell の電位はソース・ドレインと同じか高い電位である必要があります.

つまり,上の図では何も端子がついていないように見える p-sub,n-well にもどうにかして適切な電位を与える必要がある,ということです.

1.5 基板タップ

p-sub,n-well に電位を与えるための構造を基板タップと呼びます.substrate contact の略でサブコンと呼んだりもします.下図のように,p-sub に pplus を作りそこにコンタクトを打つことで金属配線と基板を接続します.p-sub と pplus は同じ p型半導体なので,空乏層はできず常に導通します.

なぜわざわざ pplus を作る必要があるのか? と思うかと思いますが,コンタクト (金属) と接続できる半導体は pplus と nplus (とポリシリコン) だけです.金属と半導体を接合すると,条件によっては pn接合のようにある方向の電圧をかけたときしか導通しない整流特性を示すことがあります (ショットキー接合).それでは困るので,どちら向きの電圧をかけてもちゃんと電流が流れるようにする必要があります (オーミック接合).pplus/nplus 相手でないとオーミック接合にできないので,必ず pplus か nplus が要ります.

ショットキー接合とオーミック接合についてはバンド図を理解しないと難しいので,理屈が気になる人は半導体の教科書を読みましょう.なお,実際には pplus/nplus にするだけではダメで,仕事関数調整のためにコンタクトと nplus/pplus の接合面にはタングステンが貼られていたりします.

pMOS の場合は下のような構造になります.pMOS は n-well に囲まれているわけですが,n-well は p-sub に囲まれているので,n-well,p-sub の両方にタップが必要です.

「順方向電圧がかからなければ導通しないんだから別にタップ打たなくてもいいんじゃないの?」と思った人がいるかも知れませんが,タップは必要です.電気回路において,どこにもつながっていないノードをフローティングノードと言いますが,フローティングノードは誰からも電圧を制御されていないので,もしノイズが入ってきた場合,ノイズに従って電位が大きく変動します.つまり,ノイズによって pn接合が ON する可能性があるということです.ノイズで ON するだけなら,ノイズが消えたらすぐに導通は解除されますが,一旦ONになったらノイズが消えても導通が解除されないという恐怖の現象ラッチアップ (Latch-up) があるため,これを避けるために必ずタップは必要です.

1.6 トリプルウェル構造

なんか pMOS はウェルと基板にタップ打たなくて面倒臭いな,という感じですが,見方を変えると pMOS は nwell という個室を持ち得ると言えます.トランジスタ1個ずつ nwell を独立させれば,pMOS は空乏層の壁に囲まれた個室に引き込もれるわけです.nMOS の場合は p-sub の中にいるので,大部屋です.隣の nMOS との間に壁を作ることはできません.

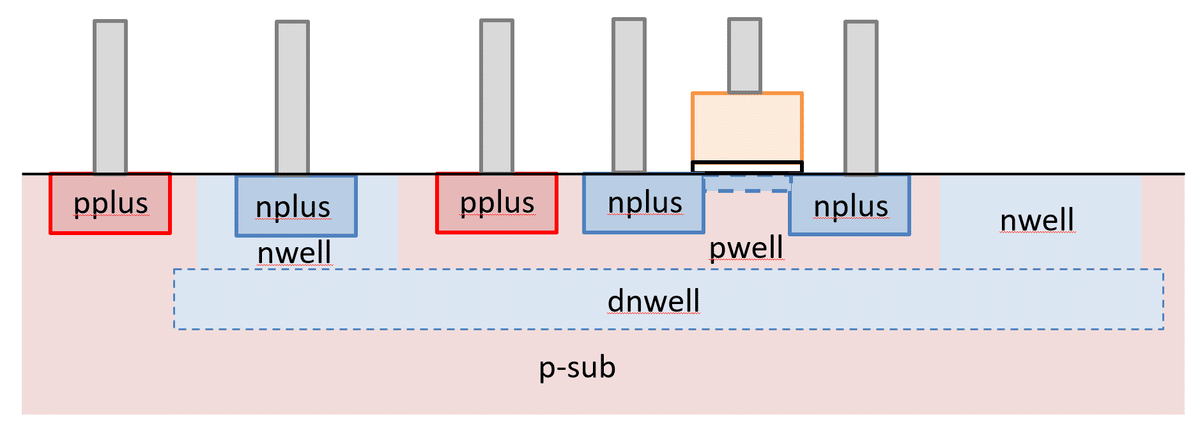

pMOSだけ個室なのはズルいので,nMOS でも個室を持てるようにしたのがトリプルウェル構造,トリプルウェル構造を実現するために使うのがディープnウェル (dnwell) です.dnwell はその名の通り深い場所にある nwell で,nwell・pwell よりも深い場所にあります.そのため,下図のように,dnwell の上に nwell・pwell を作ることができます.このような構造にすることで,pwell が dnwell の床と nwell の壁に囲まれて p-sub と分離されます.nwell と dnwell は n型同士なので,導通しています.pwell,nwell+dnwell,p-sub それぞれに電位を与える必要があるため端子の数は多くなりますが,これによって nMOS も pwell の個室を手に入れることができるというわけです.

ただし,バックゲート (ボディ) 端子には pwellとnwell+dnwell間の空乏層からなる容量が接続されることになりますので,注意が必要です.

2.基板・ウェルの役割

基板・ウェルの設計がよく分からないのは,基板・ウェルの役割が複数あることが理由の一つだと思います.基板・ウェルに電位を与えるにしても,目的によってレイアウトの仕方が違います.そのため,「あっちはこういうレイアウトなのにこっちはなぜこういうレイアウトになってるの?」という感じになります.ここでは基板・ウェルの役割を説明します.

2.1 空乏層による絶縁

すでに説明したように,MOSFET においてすべての pn接合は空乏層によって絶縁されています.MOSFET は空乏層によって適切に領域同士が絶縁されているのが動作の前提なので,空乏層を維持するのは大前提となります.そのために基板タップ・ウェルタップを打ちます.もし空乏層が維持できなくなったらデバイスは壊れます.

基板タップ・ウェルタップの目的はラッチアップを防ぐことです.ラッチアップがどういう現象かは付録で解説しますが,とにかく基板の電位を適切な電位 (p-sub なら Vss,n-well なら Vdd) に押さえ込みたい.では基板タップはどのぐらい打てばいいでしょうか? もし基板の抵抗率が0ならどこか一箇所にタップがあれば基板の電位は完全に固定されますが,基板・ウェルは金属ほど抵抗率は低くなく,nwell でシート抵抗 1000 Ω□ 程度です.配線が90 mΩ□なので10,000倍ぐらいあります.

そうすると,下図のように基板は抵抗メッシュと見なすことができます.抵抗はけっこう高いので,一つの基板タップが電位の変動を押さえ込める範囲は限られます.そのため,ある程度の間隔で基板タップを打つ必要があります.

デジタル回路では基板タップを持つセル (GF180 では filltie) が自動的に挿入されるので設計者は意識する必要はありません.

アナログのフルカスタム設計では手動で挿入する必要がありますが,Pcell を使えば自動挿入も可能です.

2.2 基板バイアス効果

基板・ウェルは電源 (VDD),グラウンド (VSS) に接続することが多いですが,基板・ウェルの電位はトランジスタのしきい値電圧 Vth に影響します.まずしきい値電圧 Vth が何だったかをおさらいしましょう.MOSFET はゲート電極に電位を与えることで,ゲート直下に電荷を集めます.nMOS であればゲートに正の電位を与え,ゲート直下に電子を集めます.ゲート直下は p-sub なので,集まった電子は正孔と再結合して消え,空乏層を形成します.これが弱反転領域 (weak inversion) です.ここからさらにゲートに電圧をかけると,ついには集まった電子が正孔より多くなって余り,ゲート直下の p-sub をn型半導体に反転させます (チャネル).この状態が強反転 (strong inversion) であり,強反転に必要なゲート-ソース間電圧がしきい値電圧 Vth です.

さて,ここで p-sub の電位が変わった場合を考えましょう.p-sub の電位とソース端子の電位が等しい状態を基準にします.p-sub の電位がソース電位より下がった場合,p-sub が電子を引っぱるわけですから,チャネルを作るためにゲートはより強い電界を必要とします.そのため,しきい値電圧は大きくなります.逆に,p-sub の電位がソース電位より高くなるとしきい値電圧は下がります.このように,基板・ウェル (Body,Backgate) の電位によってしきい値電圧が変化する現象を基板バイアス効果 (body effect)と呼び,しきい値電圧が上がる方向に基板・ウェルに電圧をかけることを逆方向基板バイアス (reverse body bias, RBB),しきい値電圧が下がる方向を順方向基板バイアス (forward body bias, FBB) と呼びます.なお,FBB をpn接合の順方向電圧 (0.6 V)以上にかけるとpn接合が ON するのでトランジスタは壊れます.FBB による pn接合ONは SPICE ではモデル化されません.SPICE ではいくら FBB をかけても動きますが,それはシミュレーション上だけの話で実デバイスは動きませんので,注意しましょう.

デジタル回路では特殊な場合を除いて基板バイアスを回路設計者が操作することはありませんが,基板バイアス効果自体はデジタル回路の性能に影響しています.例えば下図は NAND2 の回路図です.デジタル回路ではすべての nwell は VDD,基板は VSS になりますので,バックゲート (ボディ)の端子は省略されることが多いですが,バックゲートも描くと下図になります.この回路の中で Mna を見ると,バックゲートが VSS に接続されていますが,ソース電位は Mnb のドレイン電位ですから,VSS よりも高い電位になります.よって Mna についてはバックゲート-ソース間電圧はマイナス,つまり逆方向基板バイアスがかかり,しきい値電圧は他のトランジスタよりも高くなります.

アナログ回路ではデジタル回路よりも積極的に基板バイアス効果を使うことがありますが,それゆえの悩みが生じる場合もあります.下図は nMOSソースフォロワですが,バックゲートをVSSにつないだ場合とソース端子につないだ場合でどういう違いがあるでしょうか.図左の VSS につないだ場合は,基板バイアス効果によって Vth が上がる上に,$${v_{\mathrm{bs}}\neq 0}$$ なので小信号特性にも影響があり,利得が下がります.図右では基板バイアス効果も利得の低下もありませんが,バックゲート端子が出力端子に接続されていますので,バックゲートにつく大きな寄生容量が出力端子にのしかかることになります.これによって,右の回路は周波数特性が悪化します.

2.3 ノイズの経路

A. ラッチアップ

この記事が気に入ったらサポートをしてみませんか?