レイアウト設計と集積回路製造プロセス

集積回路の設計は最終的にはレイアウト (マスクデータ) を工場に提出 (テープアウト) することで完了します.おそらく最も簡単なレイアウト設計ツール Siliwiz を下の記事で紹介しました.

しかしこのレイヤーはなんでこんなにたくさんあるんだ.配線はまぁいいとして p とか n で始まるやつが6種類もあるのは何なんだ,という人のためにレイアウト設計で使われるレイヤーの意味を解説します.

1.集積回路の材質

集積回路はまぁ半導体と呼ばれるぐらいなので半導体でできているわけですが,他にもいろいろ使われています.ということでまずは使われている材質を把握しておきましょう.

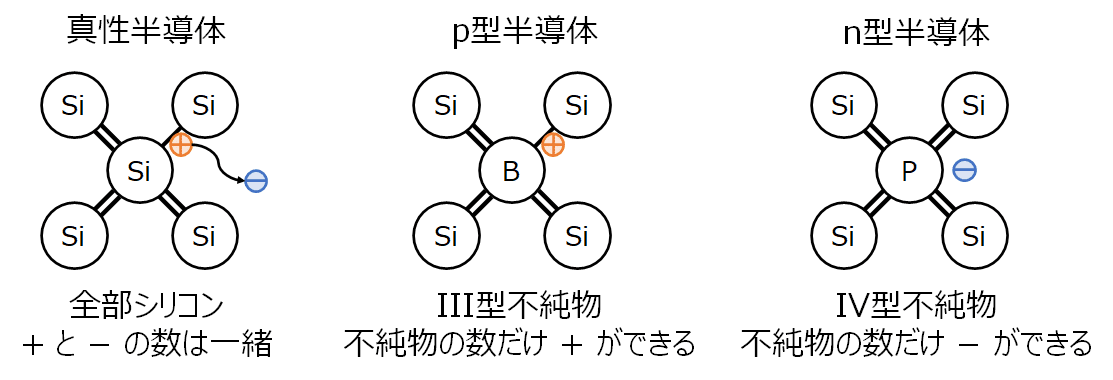

1.1 p型/n型半導体

集積回路はシリコンウェハの上に製造されます.シリコンウェハは超高純度の単結晶シリコン (シリコンインゴット) を薄く切り出したもので,この時点では 99.999999999%ぐらいシリコンです.この状態では真性半導体と呼ばれる状態なんですが,真性半導体はちょっと扱いにくいので不純物を入れます.正の電荷 (正孔) がたくさんできるようにしたのが p型,負の電荷 (電子) がたくさんできるようにしたのが n型です.

まぁ細かいことが知りたかったら半導体工学を勉強してもらうとして,ここで知っておくべきことは

p型もn型も(金属ほどではないけど)電気を通す

p型とn型を貼り合わせると,

p型とn型の境界面に電気を通さない「膜」(空乏層) ができる

p型の方の電位をn型よりもある値以上高くすると,p型から n型の方に電流が流れる

n型の方をいくら高くしても n型から p型の方に電流が流れることはない

このように電流が一方通行になります.このような特性を整流特性と呼び,素子をダイオード (Diode) と呼びます.

そして集積回路の中で使われる MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) は追加ルール

電界をかけることで p型をn型に,n型をp型に一時的に変換することができる

を使います.「電界をかけることで」が電界効果 (Field-Effect) で,電界効果をかけるための構造が MOS です.つまり,p-n-p という並びだと電流は流れませんが,この真ん中の n を電界効果で p にしてしまえば p-p-p になって電流が流れる,という寸法です.

実際にはp型/n型でも不純物の量などでいろいろ使い分けるので,Siliwiz では p-substrate/n-well/p-diffusion/n-diffusion/p-tap/n-tap の6種類があります.ただ,p型とn型の基本ルールは上の箇条書きのルールを知っておけばとりあえず問題ないです.

1.2 ポリシリコン

多結晶シリコン (polycrystalline silicon) 略してポリシリコン.もっと略してポリ (英語でも poly で通じます).小さいシリコン結晶の集合体ですが,別の材質を入れたりして導電率を高くしてあります.まぁ金属みたいなものと思えばいいです.というか,合金化処理 (シリサイド化) してるのでほぼ金属です.電界効果をかけるための「ゲート」と呼ばれる部分,つまり Metal-Oxide-Semiconductor の Metal の部分を担当します.

… Metal なのに金属じゃなくポリシリコン使うのは何故? と思ったあなたは鋭い.話すと長くなるので詳しくはおまけ A.3 に.

Siliwiz では polysilicon と polyres がポリシリコンです.polysilicon はゲートを作るための「普通の」ポリシリコン.polyres は抵抗を作るために抵抗率を高くした「高抵抗ポリ」と呼ばれるもので,同じポリシリコンですが電気的特性が違います.実際,Siliwiz では金属配線やポリシリコンの抵抗は0 で polyres のみ抵抗値が発生します.

1.3 金属配線

素子をつなぐための線には金属配線を使います.材質としてはアルミもしくは銅が使われます (一桁nmプロセスではコバルトだったりもしますが).

1.4 絶縁膜

簡略化した図では描かないことも多いですが,集積回路内の素子はSiO2によって封入し,配線や素子を絶縁しています.要はガラスですね.細かいことを言うとエッチングを止めるために窒化膜挟むとか,比誘電率を下げるために気泡を入れてスポンジ状にした多孔質シリカ (porous silica) を使うとかいろいろありますけど.

2.集積回路の作り方

2.1 フォトリソグラフィー

フォトリソグラフィー (photolithography) は光学的に (photo) 版画 (lithograph) をすること.原理としては (フィルム時代の)写真や影絵です.光源からの光をマスクを使って遮ることでパターンをシリコンウェハ上に塗られた感光物質 (レジスト) に転写します.

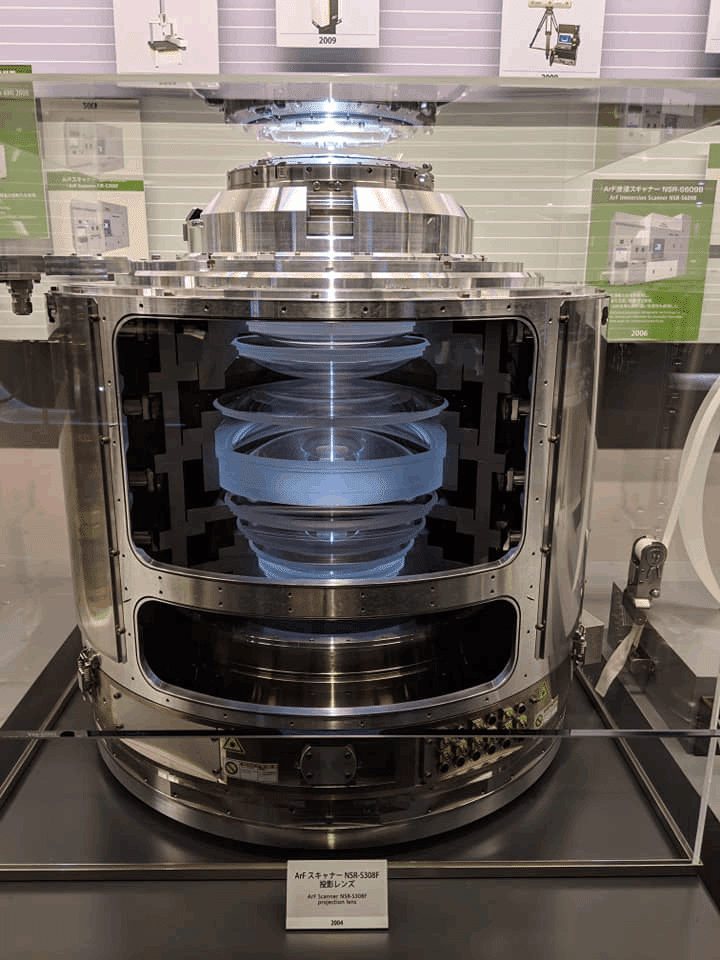

上の図は超簡略化して描いていますが実際はレンズだけでこんなのです (ニコン NSR-S308F).

光源

影絵なので光源が要ります.昔は高圧水銀灯を使っていましたが,その後エキシマレーザーが使われるようになりました.代表的なのが ArF (波長 193 nm)です.微細なパターンを描くために波長は短かい方がいいのですが,それ以外にも発光強度や安定して連続発光できることなどが求められます.EUV (波長 13.5 nm) はこのあたりの問題解決にずいぶん手間取りました.

マスク (フォトマスク) / レチクル

影絵の影をつくるための板です.写真のネガに相当する… とかつては説明していたんですが今の人はフィルム知らないですよね.フォトマスクと呼んだりレチクル (Reticle) と呼んだりします.

かつて,マスクを基板に直接接触させてリソグラフィをやっていた頃はマスクが消耗品だったので,レチクルが原版,レチクルからマスクを作ってフォトリソに使うのはマスク,という使い分けがあったとか聞いたことがありますが,本当かどうかは知りません.現在はマスクと基板の間にはレンズがあり,マスク上のパターンを基板上に縮小投影するようになっているのでマスクは消耗品ではなくなっており,レチクルとマスクの区別はないような気がします.そもそもマスク1セット作るのは余裕で数億円~数十億円かかるのでそれを消耗品扱いなんてとんでもない.

レジスト (フォトレジスト)

マスクを通ってきた光に反応して基板上に保護膜を作る物質です.塗装のときのマスキングのようなもの.光に反応して化学的な性質が変化し,現像液によって不要な部分を除去することで基板上に保護膜を作ります.光が当たったところだけが現像液に溶けるようになるものをポジティブレジスト,光が当たったところだけが硬化し現像液に溶けなくなるものをネガティブレジストと言います.マスクと同じ形のレジストが残るのがポジ,マスクと反転した形が残るがネガというわけです.

フォトリソグラフィとは基板上にこのレジストのパターンを作ることです.これによって,レジストで保護されていない領域だけに様々な加工を施すことができるというわけです.

2.2 加工

主な加工方法は以下のようなものがあります.レジストで守られていないところだけ選択的に加工することで微細加工ができるというわけです.

不純物注入

不純物を注入することで,半導体の p型と n型を変えることができます.p型/n型だけでなく,不純物の多い「濃いp型」「濃いn型」といった領域も作ることができます.かつては物質同士を接触させて熱拡散を行っていましたが,微細加工が難しいため加速したイオンを打ち込むイオン注入 (Ion Implant) が主要な方法になっています.

エッチング

余計な部分を削る工程です.かつてはエッチング液に浸すウェットエッチングが行なわれていましたが,ウェットエッチングは削れ方が等方的で,下の図のようにレジストの下も削ってしまうので微細加工に向いていません.現在は異方性エッチングができるプラズマガスエッチングが使われます.ガスに電界をかけて反応が一方向にだけ進むようにしています.

堆積

ウェハ表面に物質を積む工程.ポリシリコン,絶縁膜 (SiO2),金属配線などを積み上げていくのはこの工程です.ガス状にした物質に表面で化学反応を起こさせて物質を堆積させていく CVD (Chemical Vapor Deposition),もしくは蒸着 (PVD: Physical Vapor Deposition) が使われます.SiO2 やポリシリコンは CVD,金属は PVD です.たぶん.

研磨・平坦化

堆積した後の表面は凹凸があったり,余分なものが堆積されていたりするので,そういうものは研磨して表面を平坦にします.かつて配線が1層か2層しかなかった時代は平坦化しないこともありましたが,現在の多層配線構造では必須の技術です.CMP (Chemical Mechanical Polishing) と呼ばれます.先端プロセスのDRCで設計者の心を折りに来る配線密度ルールはこの CMP に起因しています.

アニーリング

不純物打ち込みや堆積を行なっただけでは,不純物の分布が不均一だったり金属が粒状になっていたりと品質の悪い状態になっています.そのため,アニーリング (焼きなまし) によって均質にします.炉に入れて焼きなましをしますが,レーザーで局所的かつ短時間にアニーリングする RTA (Rapid Thermal Annealing.Real Time Attack じゃないよ) なんかもあります.

酸化

基板のシリコンを熱酸化させると,絶縁物の SiO2 になります.素子分離の酸化膜 (FOX: Field OXide) を作るときにやります.

3.各レイヤーの解説

3.1 p substrate

p型基板.p-sub と呼んだりする.言うまでもなくp型半導体です.基本的に基板は一旦p型半導体に改質されます.というわけで多くのPDK では「何も描いていないところは全部 p-sub,ということも多いです.

3.2 n well

nウェル.ウェル (well) は井戸という意味だったりしますが,まぁ穴というぐらいの意味でしょうか.p-sub の中に不純物を打ち込んで n型半導体にした領域です.

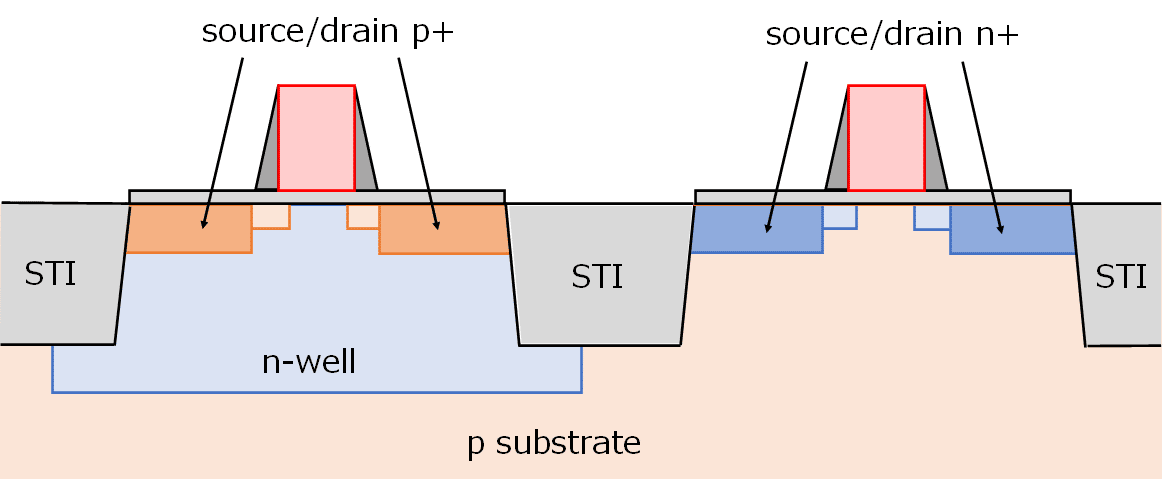

3.3 p diffusion/n diffusion

p拡散/n拡散.略して p-diff/n-diff.トランジスタのドレイン/ソースになる領域です.不純物を熱拡散させて作っていたから拡散,と呼ぶんでしょう.たぶん.p-sub の中には n-diff,n-well の中には p-diff というように,必ず p/n が異なる領域の中に作ります.そうしないと基板/ウェルと導通しますから.

プロセスによってはアクティブ (active) という呼び方だったりします.また,p-sub の中にあるのは n型,n-well の中だったら p型と決まるので p/n の区別なく単に active という1つのレイヤーに統合されていることもあります.

3.4 p tap/n tap

pタップ/nタップ.基板/ウェルに金属 (ビア) を打ち込むための領域で,不純物密度が高くなっています.タップは基板/ウェルと導通するのが目的なので,p-sub には p tap,n-well には n tap を使います.拡散層と p/n の使い型が逆になるので間違えないように注意しましょう.

プロセスによっては,不純物が多いことから p+ (pp),n+ (np) と呼んだりもします.

3.5 polysilicon

ポリシリコン.p-diff/n-diff の上に置くと,その下がチャネルになりMOSFETが形成されます.p-diff/n-diff 以外のところにはMOSFETは形成されません.(なぜ? と思った人はおまけ A3 を見ましょう.)

3.6 polyres

高抵抗ポリ.

3.7 metal1/metal2

金属配線.metal1 が基板に近い方.略して M1,M2 と呼ぶ.

SkyWater では li (Local Interconnect) が M1 にあたるので注意.

3.8 MIM capacitor

3.9 metal1 via/metal2 via

下からM1につなぐビアが metal1 via,下 (M1) からM2につなぐビアが metal2 via.略して via1,via2 と呼ぶ… ことにしますが,多くの場合 metal1 via はコンタクト (contact,略して cont とか cnt とか書く) と呼ぶことが多い.で,metal2 via に相当するビアを via1 と呼ぶ.ビアがどの層とどの層をつないでいるのかは間違えやすいので注意が必要です.間違えると配線がおかしなことになります.間違えないようにM1とM2をつなぐビアを「via12」という名前にしたりします.

SkyWater 130nm だと li があるせいで licon,mcon,via1 とさらに複雑な名前に… (でもやっぱり "via1" は「M1から生えるビア」になっているので Siliwiz のナンバリングは異端な気がする…)

4.製造工程と各レイヤーの使われ方

4.1 基板を p型にする (p substrate)

まず基板は一旦全部 p型半導体にします.p substrate です.Siliwiz では p substrate を描画する必要がありますが,たいていの製造プロセスではこの p substrate に対応するマスクはありません.せっかくがんばって超高純度のシリコンウェハ作ったのに… と思うかも知れませんが,

MOSFET は p-n接合で作るので,真性半導体は困る

基板の電位を安定させるために,基板はある程度の導電率が欲しい

というのが最初に基板を全部p型にする主な理由です.

4.2 pMOSFET用に n well を作る (n well)

p substrate の中に作れるのは nMOS です.pMOS を作るためには,「全体が n型の中に p型の領域を作る」という構造が必要なので,n型の領域を作る必要があります.これが n well です.n well で指定した領域にだけ不純物を打ち込んで n型半導体にします.

まず基板表面に SiO2 膜を形成します.これは後で全部削るんですが,基板表面を保護する役割をします.その後レジストを塗り,n-wellのマスクを使って露光・現像し,n-well の形に穴を開けます.

そこに不純物を打ち込むと,レジスト開口部の下だけ不純物によって n型に変わります.これが n well です.

終わったらレジストを除去します.

4.3 素子分離 (STI)

MOSFETを作る前に,素子分離のための STI を作ります.まずは表面に窒化膜 (Si3N4) を形成します.この窒化膜はハードマスクと呼ばれ,STIの穴を掘るエッチングの際にマスクとしてはたらきます.基板の上に直接窒化膜を作ってしまうと基板の結晶格子が壊れるので SiO2 をバッファとして挟んでいます.その上にレジストを塗り,p/n diffusion のマスクを使って diffusion の上を保護します.

このレジストでハードマスクをエッチングし,その後基板表面の SiO2をエッチングで除去します.エッチングが終わったらレジストは除去します.

ハードマスクをマスクとして,基板に穴 (トレンチ) を掘ります.穴を掘ったら表面保護のために表面を酸化させてSiO2膜を作ります.とにかく基板の結晶格子にダメージがいかないように気をつかいます.

穴を掘ったらCVD で SiO2 を積みます.

最後に表面を研磨して窒化膜,酸化膜を除去したらSTIの完成です.

4.4 ゲートを作る (polysilicon)

現在の製造プロセスはゲートポリシリコンをレジストとしても使うことで位置合わせが自動的に行なわれる自己整合プロセス (Self-Aligned Process) ですので,ドレイン/ソースの拡散層 (p/n diffusion) より先にゲートポリシリコンを作ります.

まずゲート酸化膜を作ります.この酸化膜は厚さ数nm,トランジスタのチャネルを制御するもっとも大事な膜で,原子レベルで欠陥のない均一な膜にする必要があります.ほんとに原子1個の欠陥で特性変わります.

その上に CVD でポリシリコンを積み上げます.ここで堆積されるポリシリコンは純粋なケイ素ではなく,抵抗率を下げるために不純物が混ざっています.抵抗を作るための高抵抗ポリ (polyres) では不純物を密度を変えて抵抗を上げることもあります.

ここに polysilicon マスクを使ってゲートポリシリコンの形にレジストを残します.

あとはエッチングで削り,レジストを除去すればゲートポリシリコンの完成です.この時点では diffusion領域の表面は SiO2 で覆われたままです.ここで SiO2 まで剥いでしまうと,このあとの工程で表面が壊れてしまうので保護用に SiO2 は残しておきます.

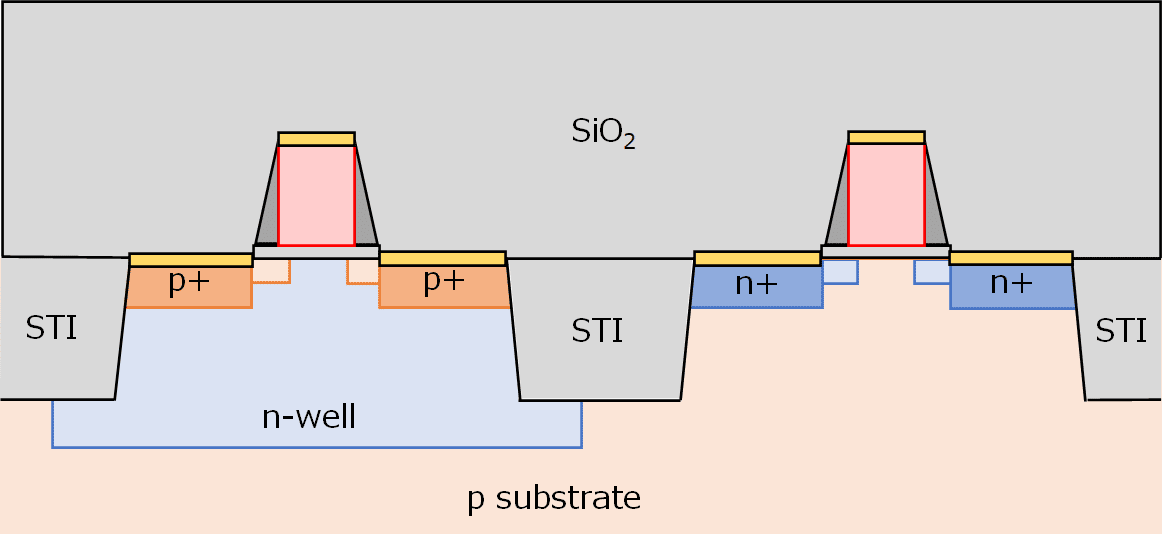

4.5 ソース/ドレイン領域を作る (p diffusion/n diffusion)

ソース/ドレイン領域 (拡散領域) はだいたい簡略化した図で描かれますが,実はけっこう複雑な構造をしています.チャネル周辺は不純物密度を複雑にコントロールする必要があったり,抵抗を下げるための合金化処理 (シリサイド化) をしたりするためです.

まず,不純物密度の薄い p/n 領域を作ります.これを LDD (Lightly-Doped Drain) と呼びます.チャネル直近に不純物密度の高い領域を作るといろいろ不都合なのでこういうことをします.ここで注目してもらいたいのは,ゲートポリシリコンが不純物を防ぐのでゲートポリの下には不純物がドーピングされていない,というところです.このドーピングされていない領域がトランジスタのチャネル領域になるのですが,先にゲートポリを作ることでチャネル領域が自動的にゲートポリの下にできます.これが自己整合プロセス (Self-Aligned Process) です.

次に窒化膜を積みます.

積んだらエッチングで削って,ゲートポリの脇だけ残します.サイドウォールと呼ばれ,この後の不純物注入とシリサイド化を自己整合プロセスにするための構造です.

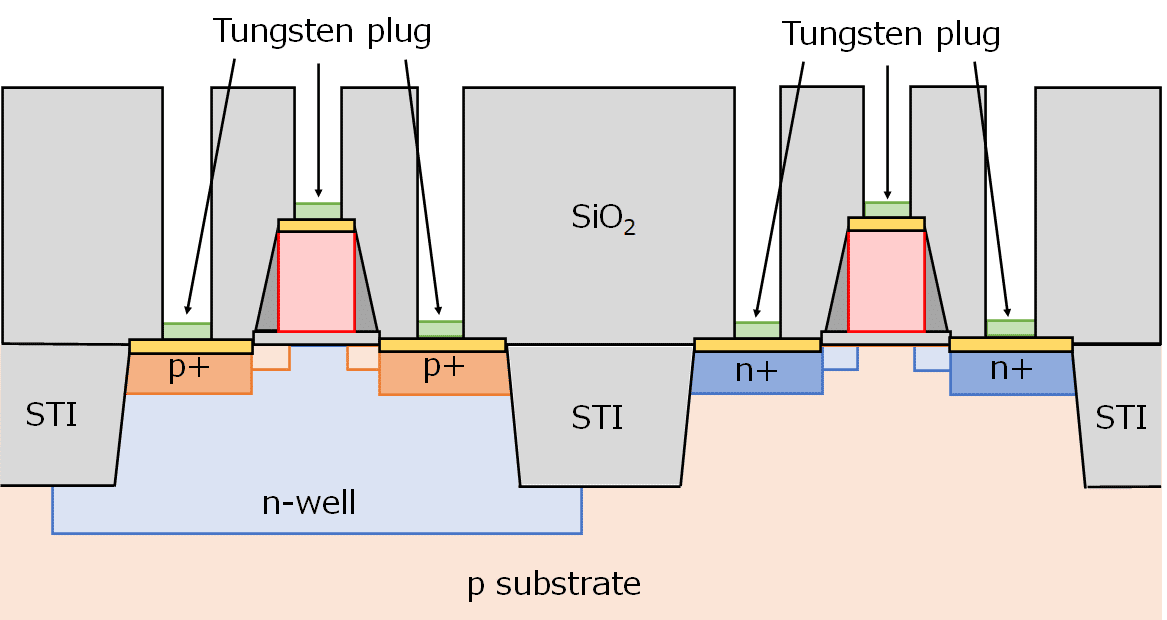

サイドウォールができたら,p/n diffusionマスクを使ってドレイン/ソース領域に不純物を高濃度に注入します.図では濃度が高いということで p+/n+ と書いています.ゲートポリとサイドウォールによって自己整合プロセスになり,サイドウォールの下に LDD が残ります.図には描いていませんが,p tap/n tap にも p+/n+ を注入します.

さらに,ドレイン/ソース/ゲートの抵抗を下げるためにシリサイド化 (合金化)します.これもサイドウォールのおかげで p+/n+/ゲートポリの上だけが合金化されます.この「自己整合するシリサイド化プロセス」をサリサイドプロセス (salicide: Self-Aligned Silicide) と呼びます.

抵抗を作る polyres レイヤーは,このシリサイド化を行なわないポリシリコンです.Siliwiz では polyres というレイヤーですが,シリサイド化させない領域を指定する silicide block を polysilicon に被せることで高抵抗ポリを作ることもあります.抵抗用ポリは,ポリシリコンの不純物の量とシリサイドの有無によって何種類かあったりします.Siliwiz では1種類だけですが.

4.6 酸化膜・コンタクトホール (metal1 via)

ここまででだいたいMOSFETは完成していますので,CVD で酸化膜 (SiO2) を積んで全体を覆います.

ただ酸化膜を積んだだけだと表面が凸凹なので,研磨して平坦化します.

コンタクト (metal1 via) を作るための穴 (コンタクトホール) を空けます.図では省略していますが,レジスト塗布,露光・現像,エッチングによって穴を開けます.

穴を開けたらタングステン膜を形成し,表面研磨でコンタクトホールの底の部分だけにタングステンを残します.このタングステンをタングステンプラグを呼びます.なぜここでタングステンが要るか,についてはおまけ A.2 を見てください.

これでMOSFETが完成です.ここまでの製造工程を FEOL (Front-End Of Line) と呼びます.この後は金属配線でつないでいく BEOL (BackEnd Of Line) です.

4.7 コンタクトを打つ (metal1 via)

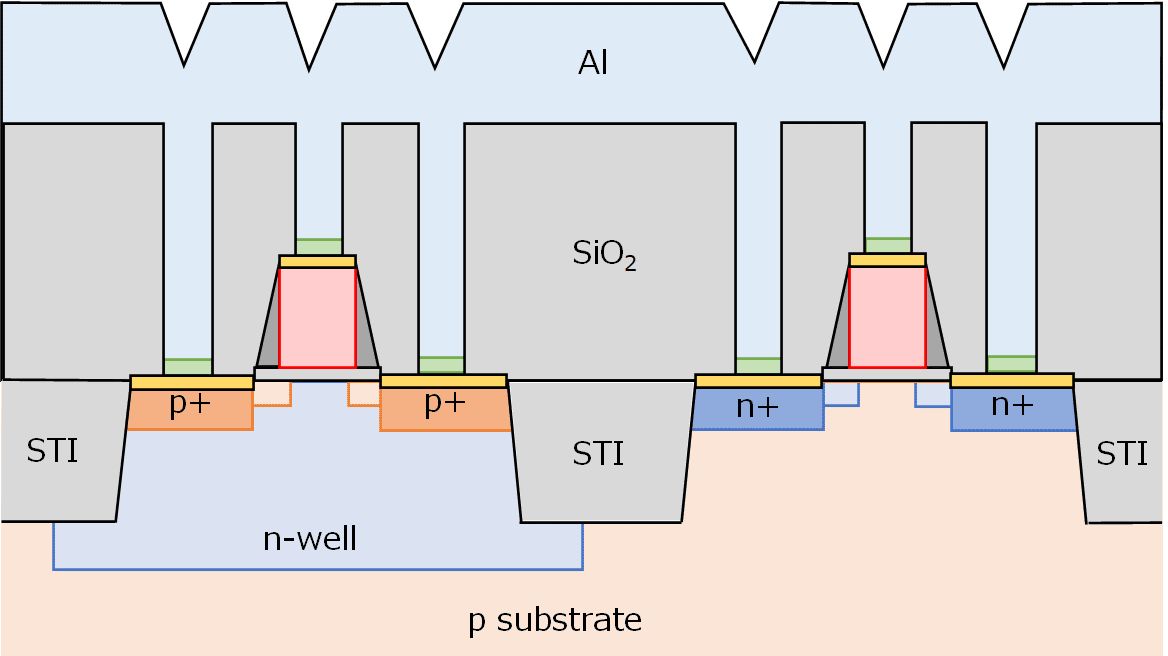

PVDによって金属 (ここではアルミとします) を堆積します.この後研磨するので,コンタクトホールを開ける前に酸化膜表面を窒化膜で覆っておくこともあります.

表面を研磨して余計な金属を除去してコンタクト (metal1 via) が完成です.

4.10.a 第1配線層 (metal1) : アルミの場合

配線材質がアルミの場合,一度全面に PVD でアルミを堆積し,後でエッチングします.

もちろんエッチングの前にはレジスト塗布,metal1マスクで露光・現像してからです.

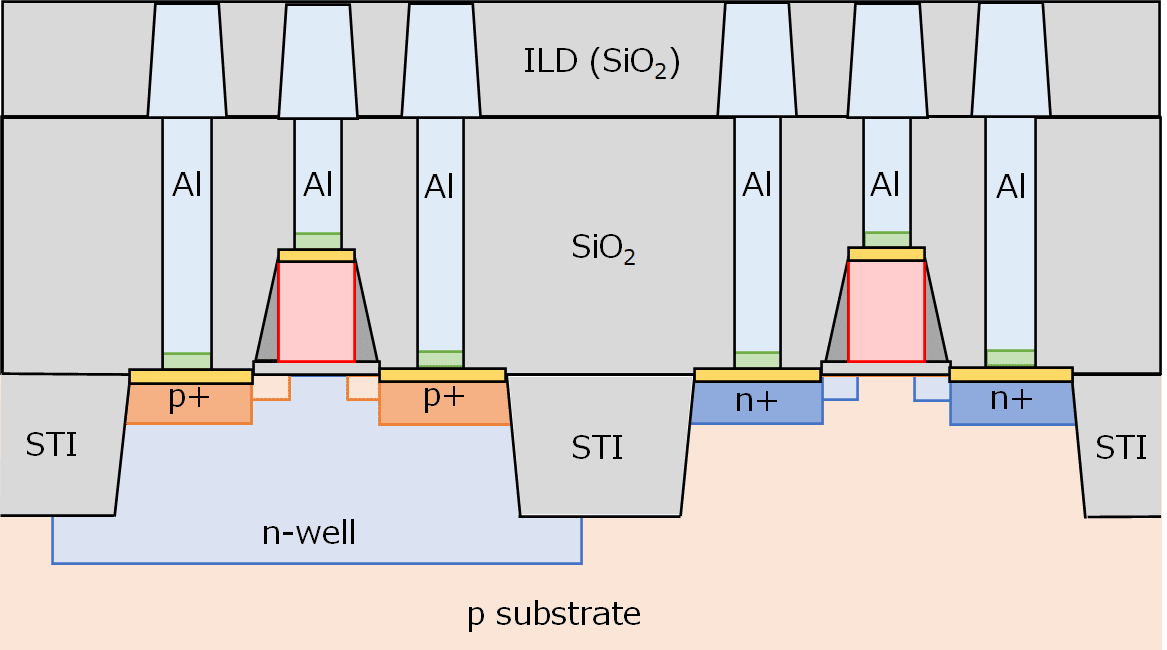

配線ができたら CVDで層間絶縁膜 (ILD: InterLayer Dielectric) となる SiO2 を堆積し,余計な SiO2 を研磨で除去して metal1 の完成です.

この後は同じように SiO2堆積 → metal2 via の穴を掘る → アルミPVD (metal2 via完成) → 研磨 → アルミエッチング (metal2) → SiO2堆積 → 研磨 (metal2完成) で metal2,metal2 via が作られます.

4.10.b 第1配線層 (metal1) : 銅の場合

材質が銅の場合はアルミと逆で,先に層間絶縁膜を作ってから metal1 マスクで配線の形に穴を掘り,そこに銅を埋め込みます (ダマシン工程: Damascene process).ダマシンというのは日本語で言うと象嵌.表面に溝を掘ってそこに異なる材質を埋め込み,表面を研磨するという製法で,ダマスカスで編み出されたためダマシンと呼びます.なぜ材質によって作り方が変わるのか? の理由の一端についてはおまけA.2にて.

ダマシンの場合はまず層間絶縁膜のSiO2を積み,それを metal1マスクを使ってエッチングします.バリアメタルを貼ったり,エッチングを止めるための窒化膜を作ったりもしますが,それは省略…

ここに PVD で銅を堆積し,表面を研磨・平坦化 (CMP) することで配線を形成します.ここでは metal1 のみを形成していますが,実際には配線の溝とビアの穴を掘っておき,2層一度に銅で埋めるデュアルダマシンでやります.

上の図ではコンタクトがアルミ,metal1 が銅になっていますが,このあたりの材質はプロセスによって違います.metal1 までアルミ,metal2 から銅というプロセスもあります.

A.おまけ

本文中に書くと長くなるおまけ情報いろいろ.

A.1 タングステンプラグ

p型半導体と n型半導体を接合すると整流効果をもつ,という話はしましたが,半導体と金属を接合した場合はどうなるか? というと,半導体-金属接合でも整流効果がでることがあります.これは使う材質の組み合わせで決まります.なぜ整流効果がでるのか,について半導体の教科書を読みましょう.

整流効果をもつ組み合わせをショットキー接合 (Schottky barrier junction),ダイオードにならない組み合わせをオーミック接合 (Ohmic contact) と呼びます.当然ながらコンタクトが整流効果をもつのは困るので,オーミック接合にしたい.この組み合わせは接合している金属の仕事関数で決まるので,オーミック接合になるタングステンをまず貼りつけて,そこにアルミをつなぐわけです.

A.2 銅の困った性質

銅 (抵抗率 1.7 μΩ・cm)はアルミ (抵抗率 2.7 μΩ・com) より抵抗率が低いため,配線の材質としては優れているように見えます.実際,身の回りにある導線はほとんどが銅でできています.しかし,集積回路の配線に銅を使うのは簡単ではなく,銅配線がいい派 (IBMとか) vs. 銅配線はダメ派 (Intel とか) でけっこうな議論がありました (結局配線は130nm か 90nmあたりから銅配線になった).

その困った性質というのが「銅原子はSiO2 の中に染み出す」というもの.銅は絶縁膜である SiO2 の中に染み出していき,ついには隣の配線とつながってしまったりするのです.これを防ぐために,SiO2 に「防水加工」をする必要があり,バリアメタルと呼ばれるタンタル (Ta) や窒化タンタル (TaN)で SiO2 の表面を覆う工程が必要になりました.そのため,銅配線は絶縁膜を作る → 穴を掘る → バリアメタル形成 → 銅を埋めるという順番にする必要があり,ダマシン工程になりました.(これだけがダマシン工程の理由ではないですが.)

A.3 ゲートはなぜポリシリコンなのか

ゲートはポリシリコンでできています.ただこれは最初からではなく,もともとは金属でした.だから Metal-Oxide-Semiconductor (MOS) なのです.なぜポリシリコンになったかというと,製造工程の都合で金属ゲートが使えなくなったからです.

もともと,集積回路は下から順番に作っていました.ドレインとソースを作った後に,チャネルにゲートを乗せていたわけです.しかしこの作り方はゲートの位置精度をものすごく高くする必要がありました.もしゲートがドレイン/ソースから外れた場合,チャネルがドレインとソースの間をつなぐことができず,トランジスタとして動きません.かと言って余裕をもってドレイン/ソースとゲートを大きくオーバーラップさせると余計な容量 (オーバーラップ容量) がついて動作が遅くなります.

そこで編み出されたのが,先にゲートを作ってからドレイン/ソースを作る 自己整合プロセス (Self-Aligned Process) と呼ばれる方法です.これは先に作ったゲートにレジストの役割を担わせることで,ドレインとソースの拡散層が自動的にゲートとぴったりの位置にできる,という方法です.Siliwiz でも,p-diffusion/n-diffusion の上に polysilicon を置くと,自動的に polysilicon の下の diffusion が消えます.

自己整合プロセスは非常に賢い方法なんですが,拡散層の形成は熱拡散で温度が800度ぐらいになります.熱拡散じゃなくてもイオン注入の後はアニーリングしますので,やっぱ高温になります.そうするとアルミ (融点660度) は耐えられない.というわけで熱に強いポリシリコンを使うようになりました.銅 (融点 1,085度) なら耐えられるって? 銅は銅で他に困った性質があるのでたぶん使われなかったんでしょう… (よく知らない.でも銅に困った性質があるのは本当.)

で,ずっとポリシリコンが使われていたわけなんですが,その後ゲートは再び金属に戻ります (全部金属ではなくポリシリコンが主体ですが).High-k/Metal-gate と呼ばれますが,ここに至る話はまたさらに長くなるのでここでは割愛.