レイアウト設計超入門: Siliwiz で遊ぶ

1.レイアウト設計

ICの設計は最終的にはレイアウト (マスクデータ) と呼ばれる図面を描くことです.製造工場にレイアウトを送り,その図面に従ってフォトマスク (レチクル) が作られ,フォトリソグラフィでICが製造されるわけです.(もしかしたらEB直描かも知れないけど.)

ではIC設計者はみんなレイアウト描いてるのか? というとそうでもないです.面倒臭いから.デジタル回路はほぼ自分でレイアウト描くことはなく,RTL (もしかしたらもっと高位) から合成・配置・配線がEDAツールによって自動的に行なわれます.

ではレイアウトは人間が描かなくてもいいか? というとそれも違います.アナログ回路は人手でレイアウトを描くことも多いですし,デジタル回路の"部品" (スタンダードセル) を作る人ももちろん手描きです.… とまぁそういうことは置いておいて,せっかくIC設計するんだから自分でトランジスタ描いてみたいですよね.ということで描きましょう.

でもいきなり実際のPDKでレイアウト設計をやると,数十~数百ページのデザインルールブック・数百~数千のエラーを指摘してくるDRC・がんばってもエラーが見つけられないLVSによって心が折れます.そこで,もっと優しい Siliwiz から始めましょう.

2.Siliwiz

2.1 Siliwiz とは

Siliwiz は実用ではなく教育に目的を置いたツールです.ツールというか教材です.ブラウザでレイアウトとシミュレーションがインタラクティブに動きます.すごい.

Github はこちら.

おなじみ Matt Venn による解説動画もあります.(Siliwiz は TinyTapeout・ZerotoASIC に関連しています.)

2.2 Siliwiz のいいところ

ブラウザですぐ動く・ブラウザの画面1枚でレイアウトもシミュレーションもできる.通常,IC設計では設計の場面に応じて使うツールが違います.あれをやるにはこのツール,次はこのツールだからこの形式のファイルを作って… とか,やり方を覚えるだけで心が折れます.Siliwiz はブラウザ1枚だけで分かりやすい.

とりあえず何らかの特性は出る.想定年齢は「14才以上」となっており,興味があるなら小学生でも見様見真似で使えます.通常,IC設計でレイアウトしたデバイスの特性を知ろうとするとレイアウトから回路図を抽出してテストベンチつけてシミュレーションする必要があります.面倒臭い上に,レイアウトを間違っていたら抽出 → シミュレーションを繰り返さないといけません.実際にはレイアウトと回路図が一致しているかどうかを確認する LVS (Layout Versus Schematic) をする検証ツールがあるわけですが,通すのがとんでもなく大変です.冗談抜きに心が折れます.Siliwiz は抽出の手間がないのでトライアンドエラーが簡単にできます.

また,デザインルールが緩いです.エラー出す方が難しいぐらいです.これが実際の設計だと,DRC (Design Rule Check) で簡単に数百~数千個エラーが見つかり,心が折れます.Siliwiz はほとんど細かいことを考えずにレイアウトを描いても大丈夫です.ものすごくトリッキーなものも描けます.

2.3 Siliwiz の制約

インターフェースをシンプルにするために,レイアウトできる面積は結構狭いです.だいたい論理ゲート数個ぐらいがせいぜいです.実はもっとたくさん描けますが,マウスでは無理です.Siliwiz で多数の論理ゲートを手描きする職人になるぐらいなら Klayout で描きましょう…

また,シミュレーションは過渡解析,入力は1つのみでステップ入力固定 (信号遷移時間は指定可能),という割り切り方.回路シミュレーションに慣れている人はDC解析とAC解析やらせろ,とか入力せめて正弦波入れさせろとか言うかも知れませんが,縛りプレイだと思って遊びましょう.実際,過渡解析だけでもいろいろ分析は可能ですから.

3.Siliwiz を使ってみる

使ったのは ver.4719e7c,記事作成は 2023年3月18日です.

3.1 とりあえず見てみる

とりあえず siliwiz にブラウザでアクセスします.

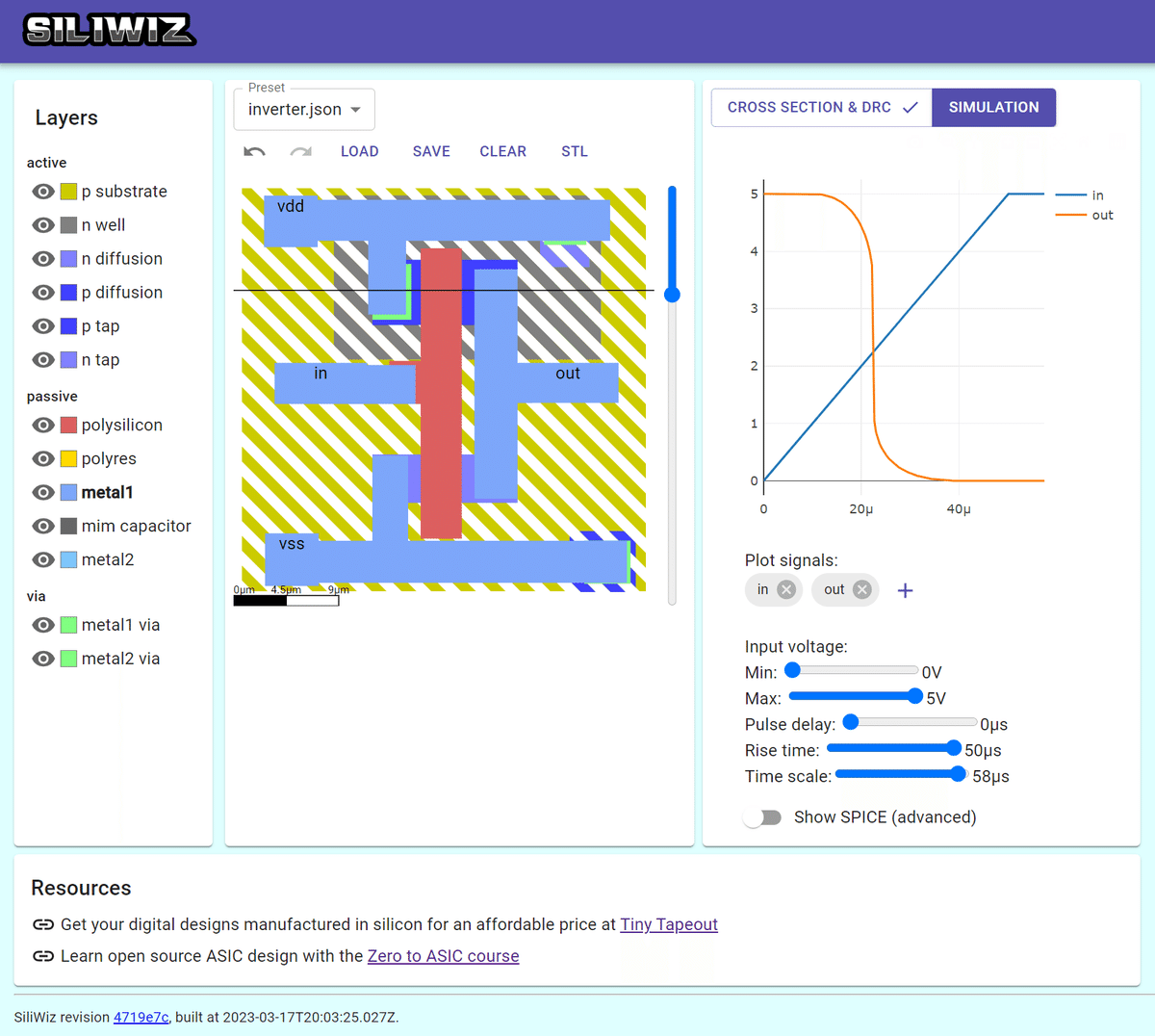

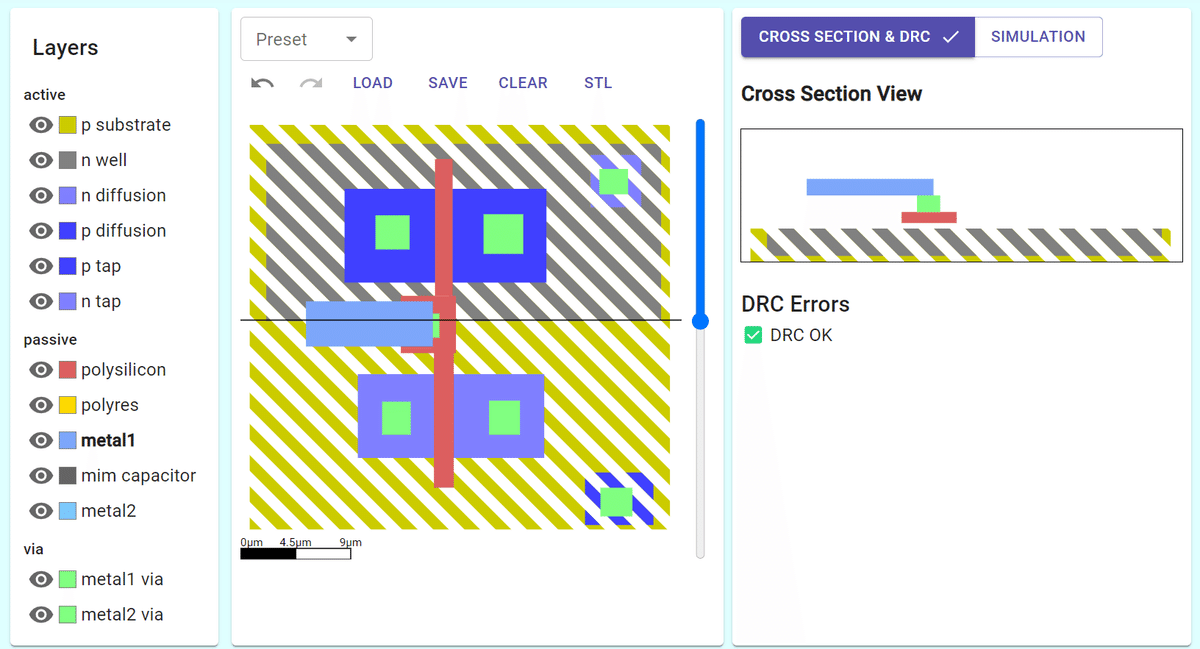

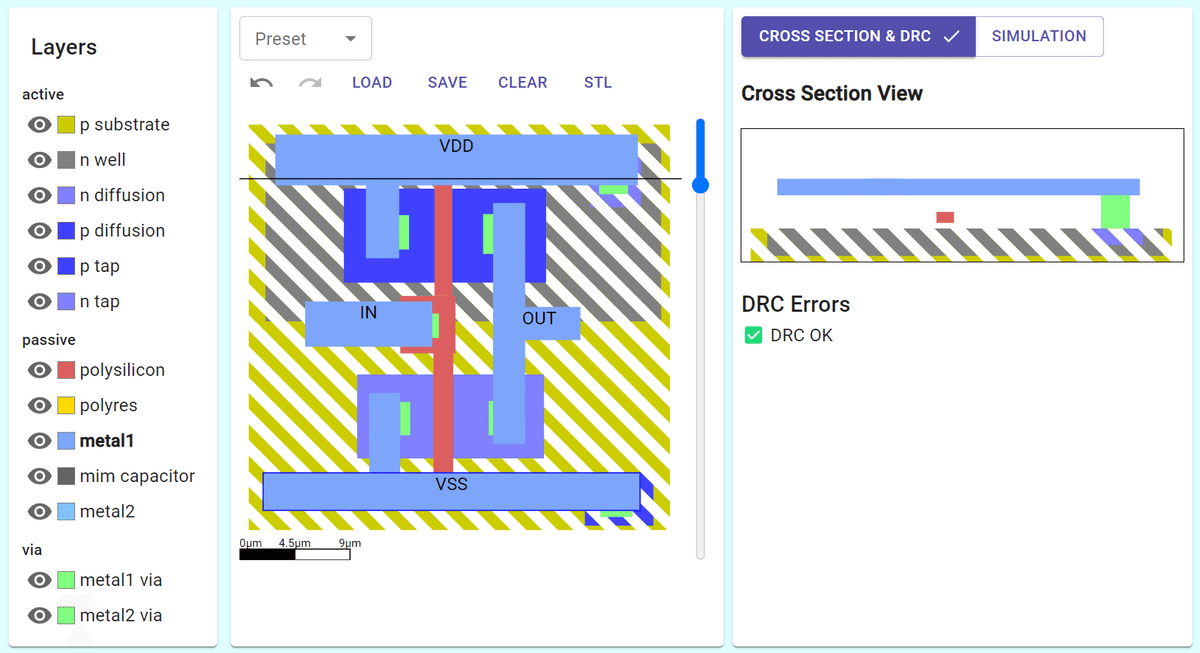

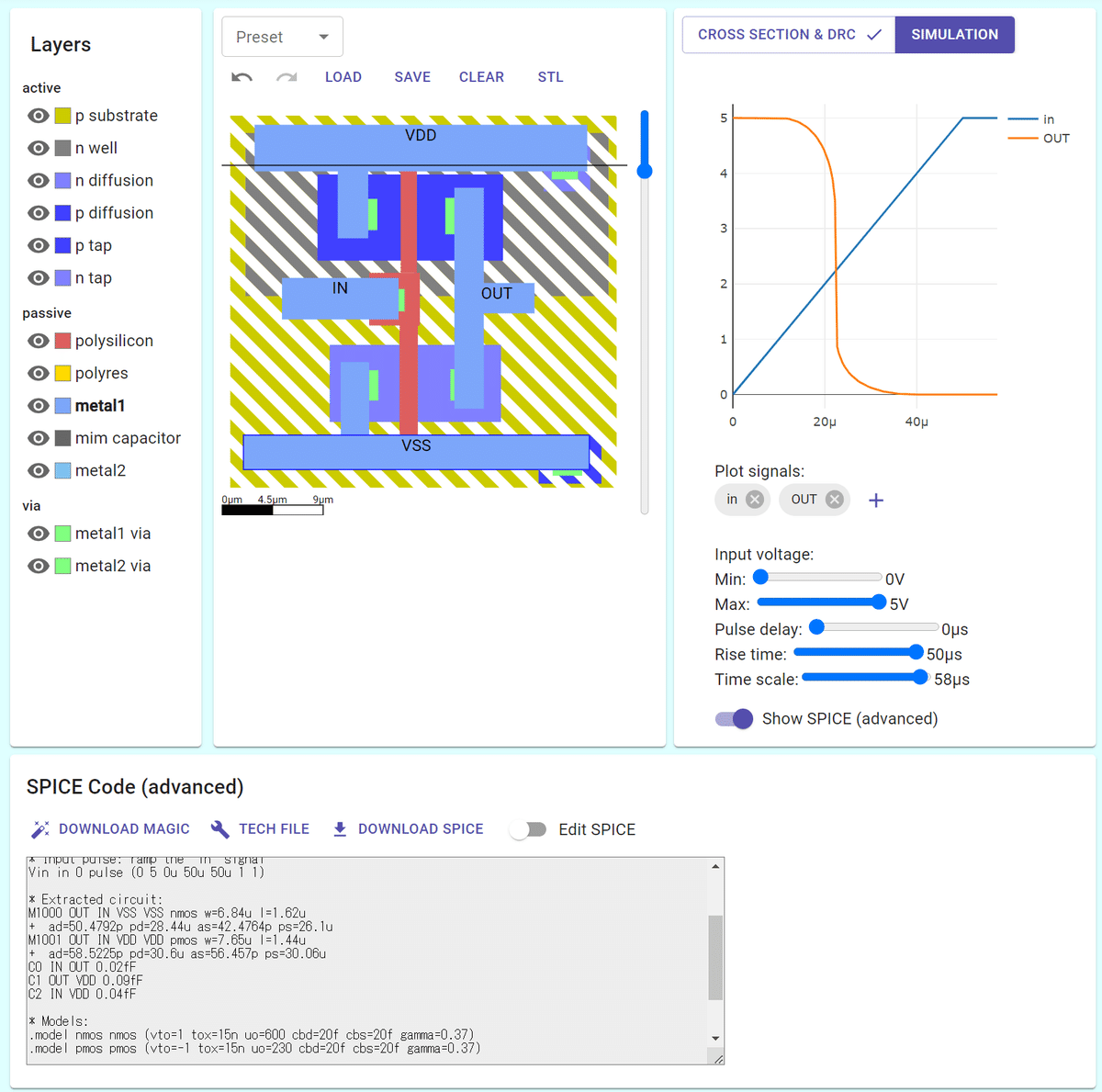

こんな画面が開くはず.分かる人には分かると思いますが,CMOSインバータですね.

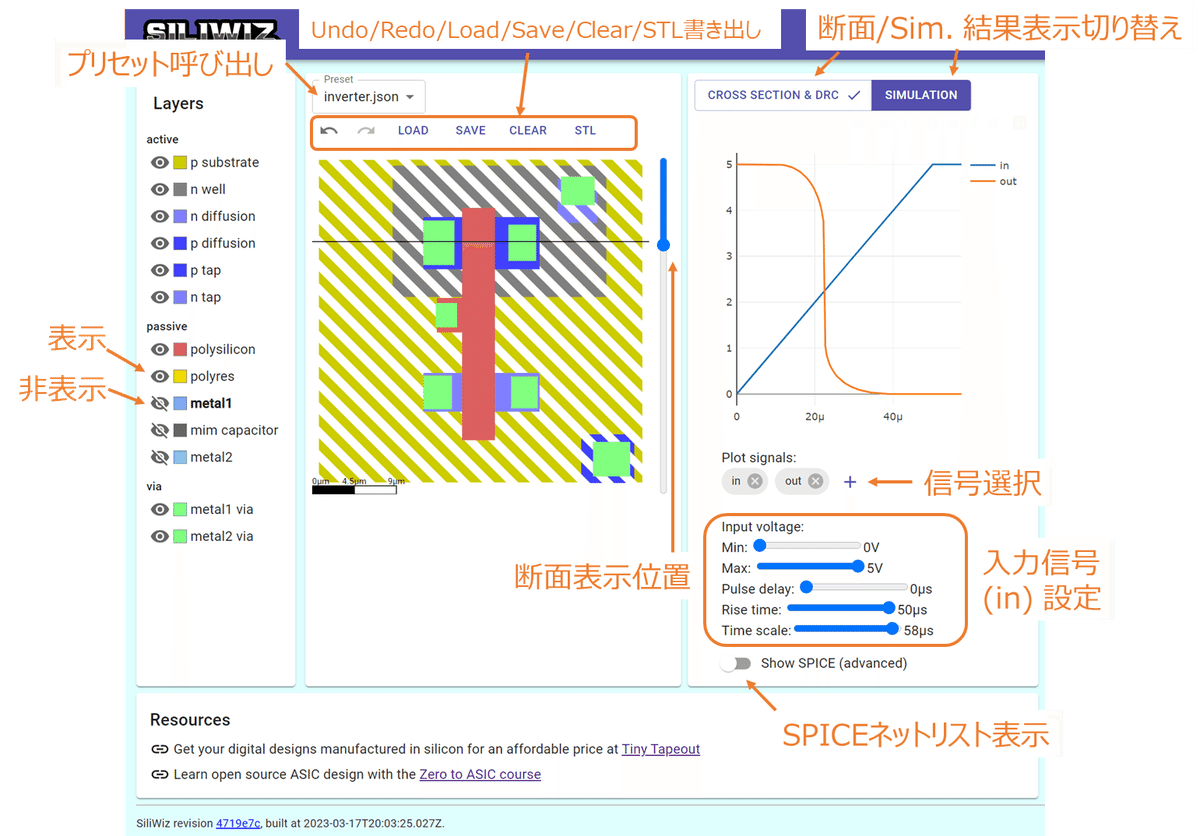

各部の説明は下図の通り.項目が少ないこともあって直感的に操作できます.すばらしいのは画面左側のレイアウトと右側のシミュレーション結果が一画面に収まっているところです.上の図と違うように見えますが,これは左側の "Layers" のところでメタルを非表示にしているからです.

また,右側は断面構造の表示に切り替えることができます.

断面構造表示がデフォルトで使えるのは非常にすばらしいです.一部のツールで断面構造を表示することはできましたが,これほど簡単に断面構造が見られるのは,初心者には非常に分かりやすい.普通のツールだと,何かおかしいときにレイヤーの上下関係を覚えて頭の中で断面構造を思い浮かべながらデバッグする必要がありますが,Siliwiz ではスライダーをぐりぐり動かして変なところを探せばいいのです.

図とグラフでは満足できない人のためにちゃんと SPICE のネットリストも出してくれます.

3.2 とりあえず描いてみる

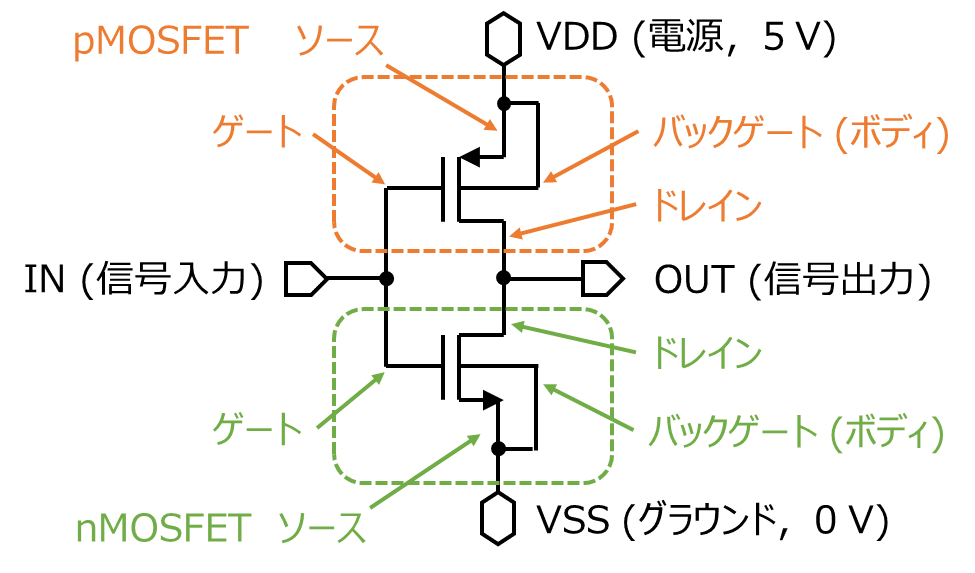

一からインバータを描いてみましょう.CMOSインバータは下のような回路図です.pMOSFET と nMOSFET が1つずつ.ゲートが入力でドレインが出力,ソースとバックゲートはそれぞれ電源とグラウンドにつながります.ひとまずこの回路図の細かいことは分からなくても大丈夫です.

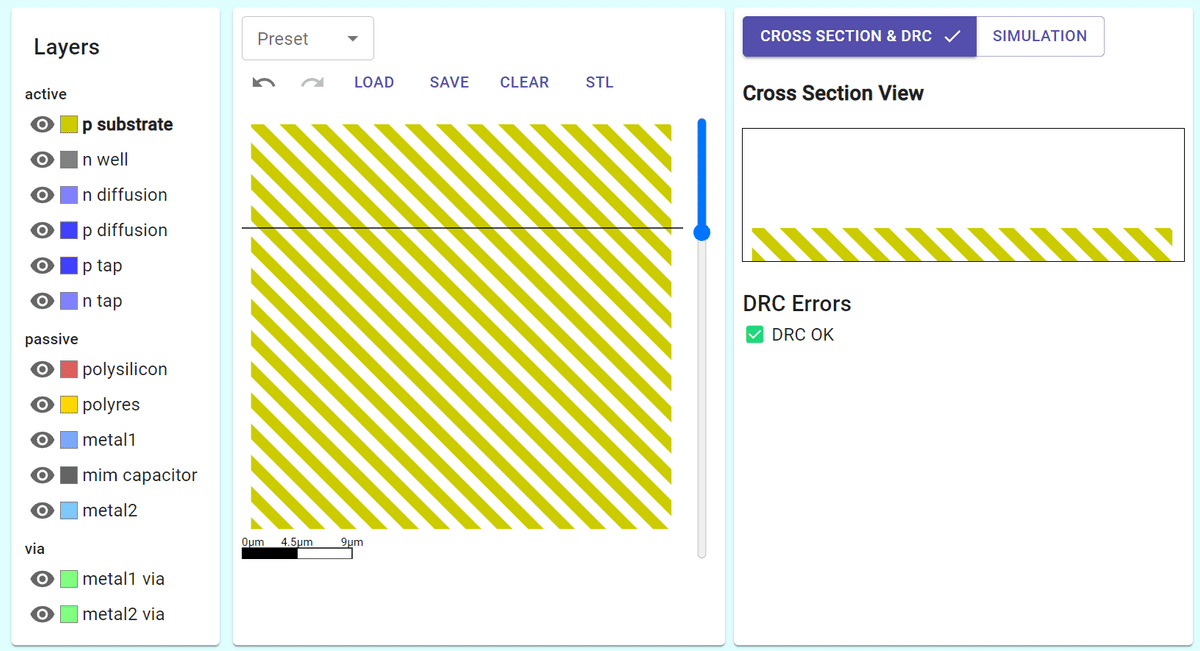

最初からレイアウトを描いていきましょう.一旦レイアウトを Clear します.

まずは Layers から "p substrate" を選択して,描画領域に大きく p substrate を描きます.レイアウトを描くときは右側を断面表示モードにしておきましょう.

p substrate というのは日本語で言うと「p型基板」.ICを作るための基板 (シリコンウェハ) はインゴットから切り出した状態では不純物のない純粋なシリコン (真性半導体) ですが,まず最初に不純物を打ち込んで p型半導体にしておきます.(なので,実際のプロセスではわざわざ p substrate は描かなくてもいいことが多いです.何も描いてないところは p substrate と扱われます.)

3.3 nMOS を描く

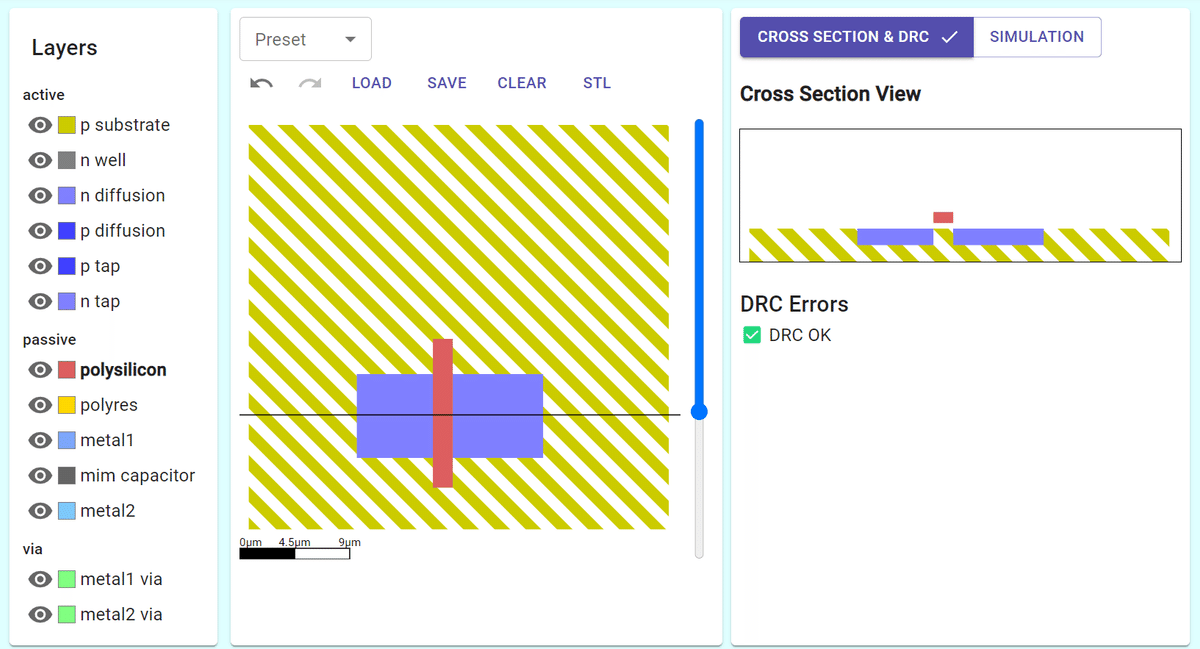

nMOS を描きましょう.画面の下半分ぐらいに,適当に "n diffusion" の四角を描きます.

断面表示のスライドを描いた n diffusion のところにもっていくと,p substrate の中に薄い n diffusion が配置されたことが分かります.n diffusion は日本語で言うと「n型拡散層」.p substrate とは違う不純物を打ち込んで,n型半導体にした領域です.ここがn型だから nMOS.n diffusion が回路図で言うとドレインとソースになります.

次にゲートポリシリコンを置きます.n diffusion のだいたい真ん中を横切るように,細長い polysilicon を描きます.

polysilicon は日本語で言うと「多結晶シリコン」.電気をよく通す材質で,金属の線だと思っていて問題ありません (実際,部分的に金属だし…).polysilicon はトランジスタのゲート電極に使う他,配線のように使うこともできます.ここで注目して欲しいのが断面構造で,polysilicon の下にあった n diffusion が消えています.これは,製造工程で先にゲートポリシリコンを作ることでゲート (polysilicon) の下に拡散層 (diffusion) ができるのを防ぐ,という作り方をするためです (Self-aligned process).詳しく説明すると長くなるので,ここでは「そういうものだ」と思いましょう.これでn diffusion が2つに分割されたので,一方がドレイン,もう一方がソースの端子になります.

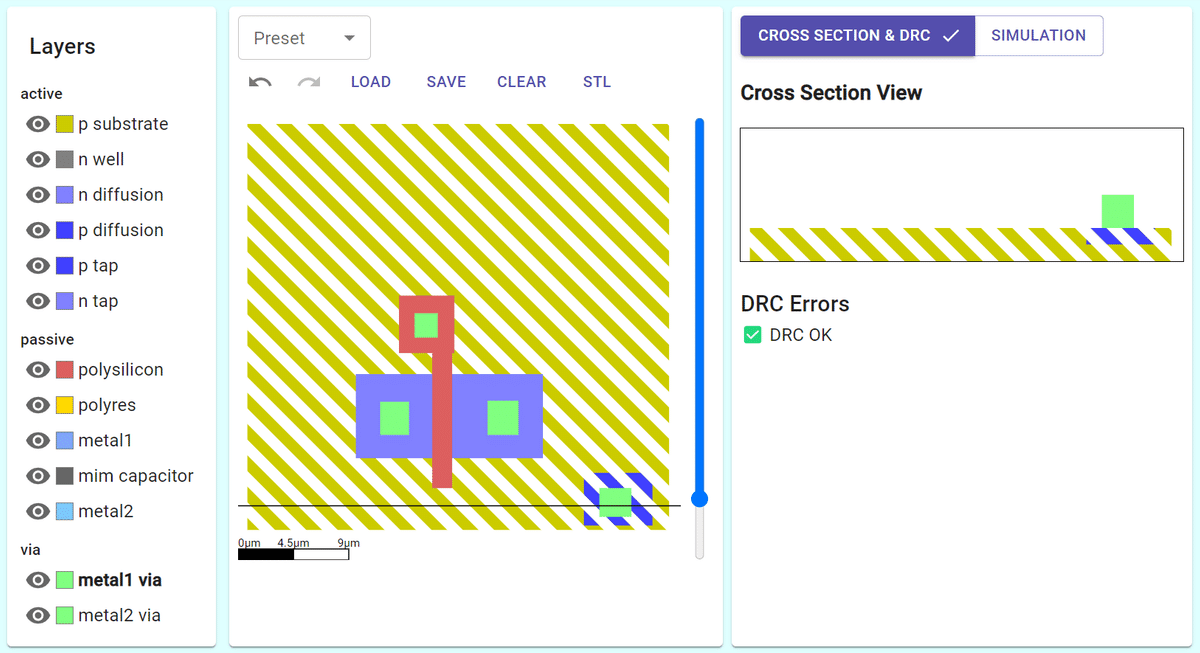

n diffusion が分割されてドレインとソースができたので,配線を出しておきましょう.断面の上下方向をつなぐ金属の線を via (ビア)と言います.n diffusion に1個ずつ小さい四角を描きます.

断面構造から,n diffusion から上に緑色の線が伸びていることが分かります.

注: 多くのPDKでは,基板につながる配線は contact (コンタクト) という特別な呼び方で呼び,M1 (金属配線1層目)と M2 (2層目) をつなぐビアを via1 と呼びます.via がどの層とどの層をつないでいるかは勘違いしやすいので注意しましょう.

ゲートポリシリコンにも配線をつないでおきます.これも via です.分かりやすいようにポリシリコンをちょっと広げて,そこに via を打ちます.

断面構造を見ると,polysilicon に via がつながっています.metal1 via は 「metal1 とその下にある何かをつなぐ線」なので,polysilicon の上に via を描くと,その via は基板ではなく polysilicon につながります.

忘れられがちですが,トランジスタには4つ目の端子「バックゲート (ボディ)」があります.これはどこに打てばいいの? というと,これは基板に打ちます.ということで p substrate に via を打つわけですが,p substrate に直接 via を打ち込んでもうまくつながりません (ショットキー接合).そこで,まず "p tap" を置いてから via を打ちます.

diffusion は n で tap は p です.間違えないようにしましょう.なぜ? というのはひとまず置いておいて,これで nMOSFET の4つの端子がすべて描けました.

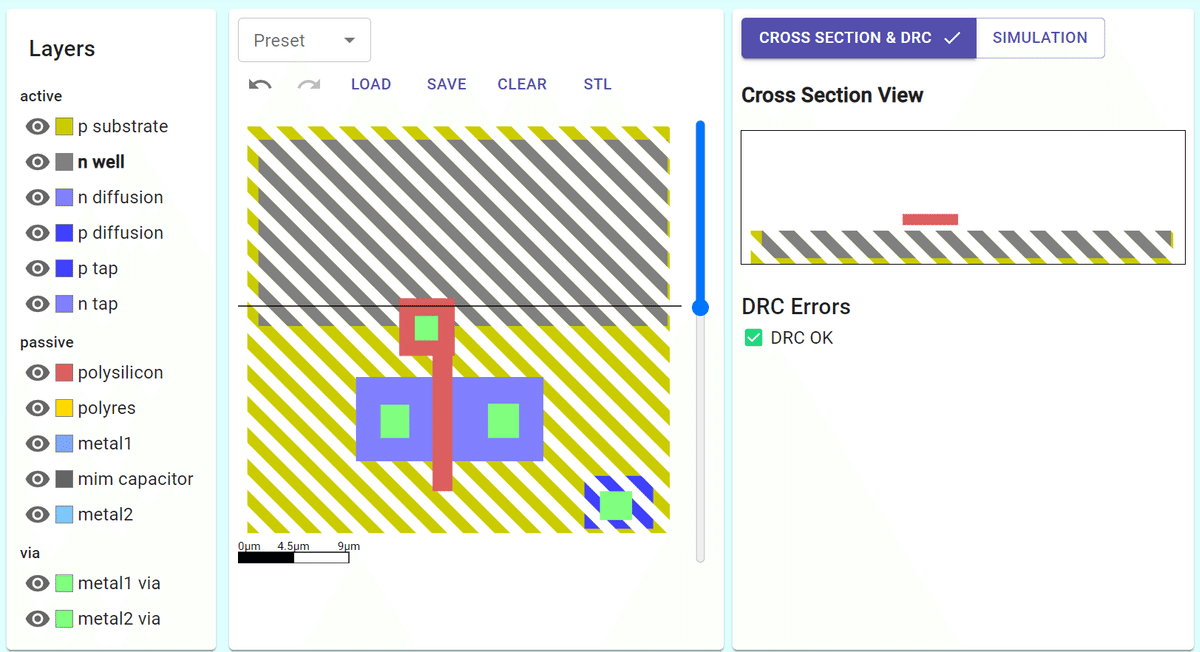

3.4 pMOSを描く

pMOS は nMOS の反対です.n diffusion を p diffusion にすればいい… のですが,p substrate の上に p diffusion を作ると基板と拡散層が導通してしまいトランジスタのなりません.なので,基板と拡散層の間にn型半導体を挟む必要があります.そのために描くのが "n well" です.上半分の空いているスペースに大きく n well を描きましょう."well" は「井戸」ですが,「穴」というぐらいのイメージでしょうか.

上図のように,n well は polysilicon や via と重なっても構いません.polysilicon や via は基板からは浮いていますので.あとは nMOS と同じ要領で p diffusion,polysilicon を置き,ドレインとソースにコンタクトを打ち,n well に n tap 経由でバックゲートの端子を打ちます.最初に出した回路図の通り,pMOS と nMOS のゲート端子はつなげますので polysilicon でつなげてしまいしょう.

p と n を間違えると DRCエラーが出ますので,断面図の下が「DRC OK」になっていることを確認しましょう.例えば p diffusion と n diffusion を間違えるとこんなエラーが出ます.

DRC はどのルールに違反しているかは教えてくれますが,場合によっては分かりにくいこともあります.上の例では「N-Well と N-Diffusion の距離が小さすぎる」というエラーですが,原因は n diffusionと p diffusion を間違えたことなのでn well と n diffusion の形をどう変えてもエラーはなくなりません.Siliwiz の場合,「使うレイヤーを間違えている」ということが多い (というかそれ以外のエラーがあんまり出ない) ので,落ち着いてレイヤーを確認しましょう.ちなみに実際の設計ではこのエラーが数十種類・数百箇所に出て絶望します.

3.5 配線をつなげて端子を作る

トランジスタはできたので,配線 (metal 1) を使ってつなげていきます.まず簡単なところでゲートから行きましょう.これは pMOS と nMOS のゲートがすでに polysilicon でつなげてあるので,ゲートの via に metal 1 をかぶせるだけです.

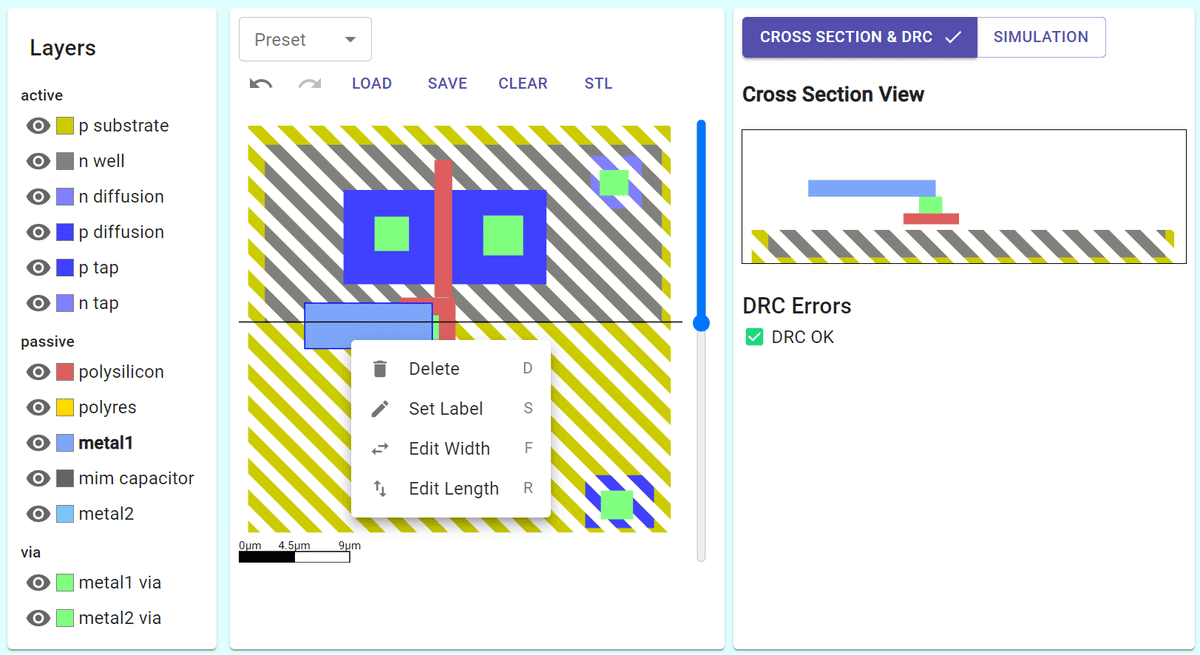

断面構造で metal 1 と via がつながっているのを確認しましょう.そして,ここは信号が入る端子なので,その指定を行ないます.描いた metal 1 をクリックすると,下のようなメニューが開きます.

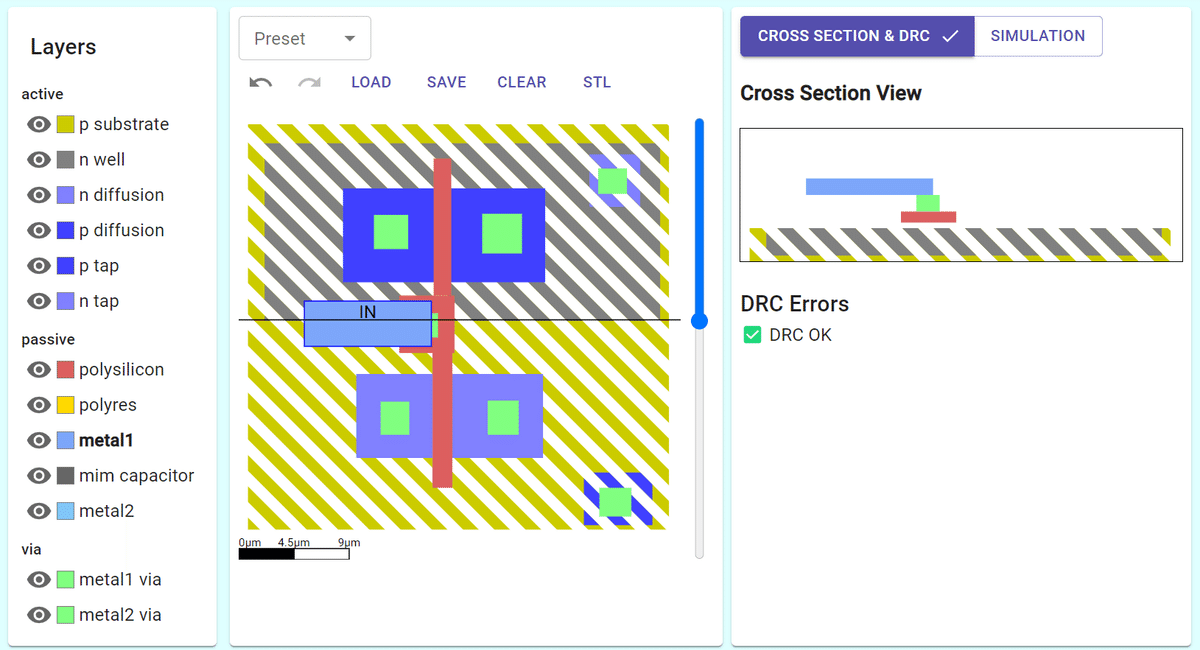

上から2番目の "Set Label" を選んで,名前を "IN" にします.これでこの配線が回路図での "IN" の端子に対応する,ということが分かります.ラベルは好きな名前をつけることができますが,信号を入力する端子は "IN" と決まっていますので,ここは "IN" とつけてください.ちなみに大文字と小文字は区別されません.

では出力端子も作りましょう.pMOS と nMOS のドレイン端子をつなげて,そこを出力端子にします.ん? ドレインとソースってどっちがどっち? と思った人は鋭いです.どっちでもいいです.レイアウトを描いて分かる通り,ドレインもソースも構造は同じですので.

metal 1 の形状は via とつながっていれば問題ありません.ラベルは "OUT" にしましたが,ここは好きな名前で問題ありません.まぁ入力が IN なのでここは OUT でしょう.論理ゲートに慣れている人は入力を A,出力を Y にしたくなるかも知れませんが.

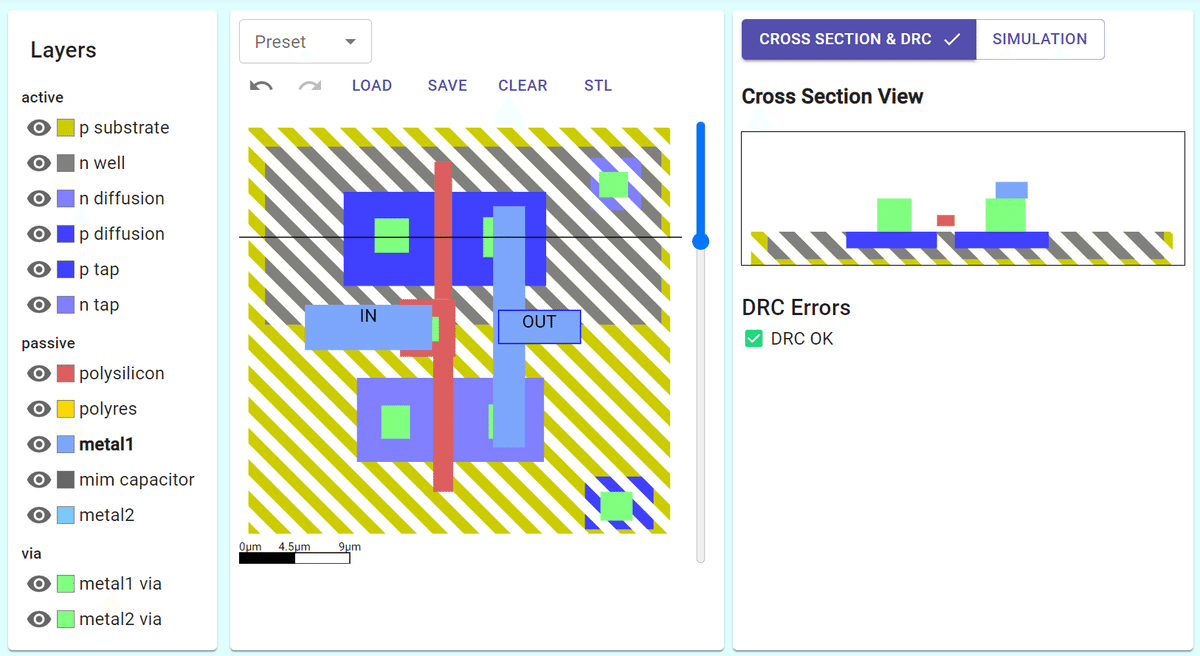

あとは電源とグラウンドです.pMOS のソースとバックゲートは電源,nMOSのソースとバックゲートはグラウンドにつながりますが,電源は "VDD",グラウンドは "VSS" というラベルをつけることで識別されます.ということで VDD と VSS を作ると下図のようになります.

metal 1 は via 以外とはつながりませんので,他のレイヤーの上を通っても大丈夫です.上図では polysilicon と重なっていますが,断面図を見ても分かるとおり階層が違うのでつながったりはしません.

これでCMOSインバータのレイアウトが完成です.

3.6 シミュレーション

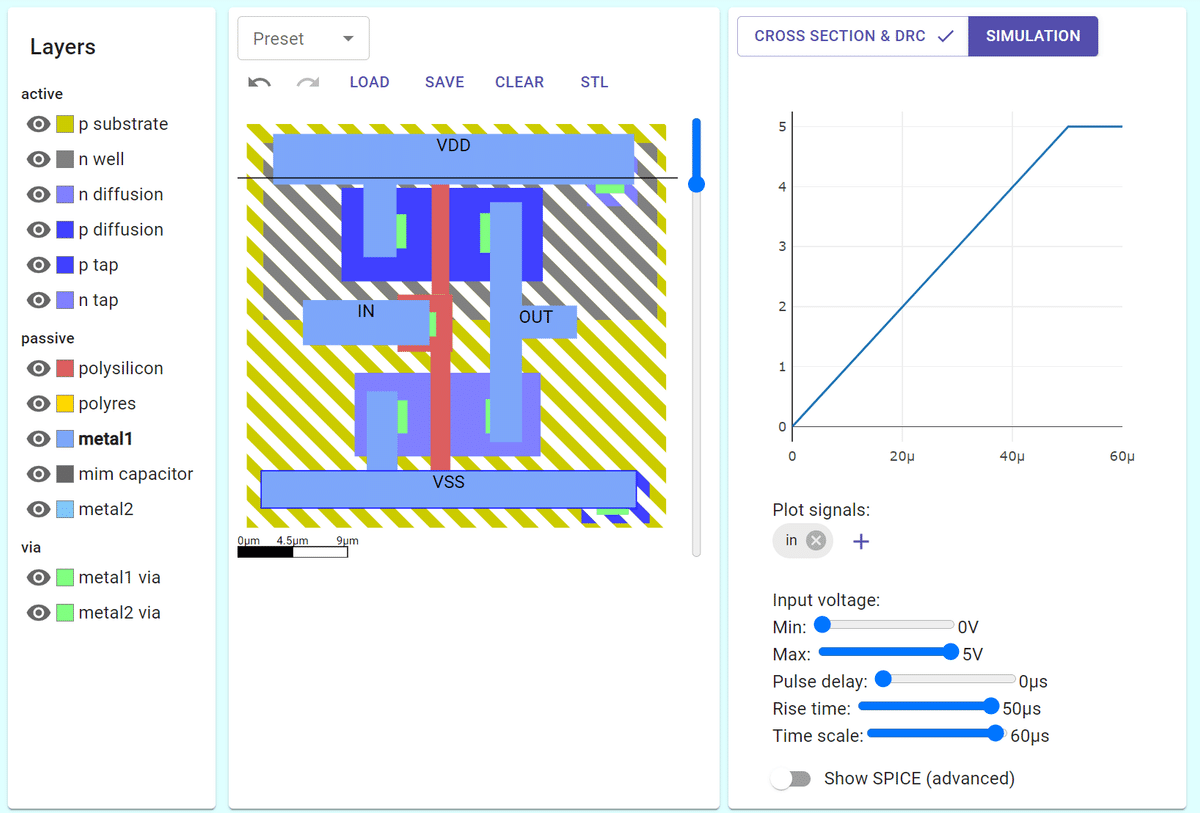

レイアウトができたので,ちゃんと動くか特性を見てみましょう.画面右側を SIMULATION に切り替えます.

IN端子は信号が入力される端子と決まっています.その設定は画面右下のスライダーで設定できます.

Min : 初期電圧.シミュレーション開始時の電圧です.

Max : 電圧が何 Vまで上がるか.他の設定によってはこの電圧まで上がらないこともあります.

Pulse delay : 電圧が変化し始める時刻.

Rise time : Min から Max まで何秒かけて変化するか.

Time scale : 何秒までプロットするか.

ちなみに Min を Max より高い電圧に設定することもできます.まぁこれはスライダーをいろいろいじってみた方が分かりやすいでしょう.

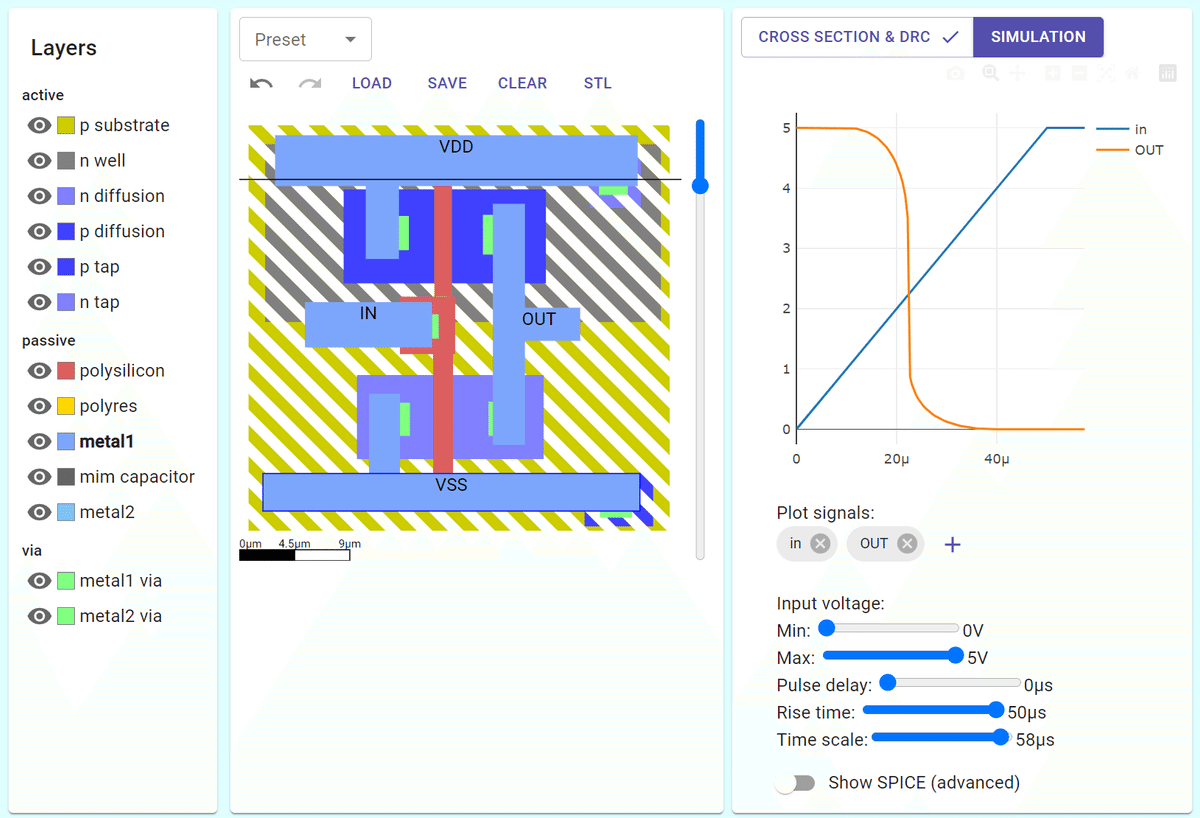

別の端子の電圧を見るときには "Plot signals: " のところで"+"ボタンを押してラベルを指定すればよいです.出力の OUT を見てみましょう.

IN の電圧が低いときは OUT は高い電圧 (電源電圧 = 5 V),IN がある電圧を超えるとOUT の電圧は急速に低い電圧 (グラウンド = 0 V) に下がる,ということが分かります.

プロットでは "i(端子名)" のように指定することで電流を見ることもできます.ただし縦軸のスケールは 0 から 5 固定ですので,適当に倍率を掛けて適切なスケールにしましょう.下図では "i(vss)*1000" と指定してグラウンドに流れる電流を 1000倍してプロットしています.つまり縦軸のスケールは mA ということですね.出力が切りかわるときだけ電流が流れているのが分かります.

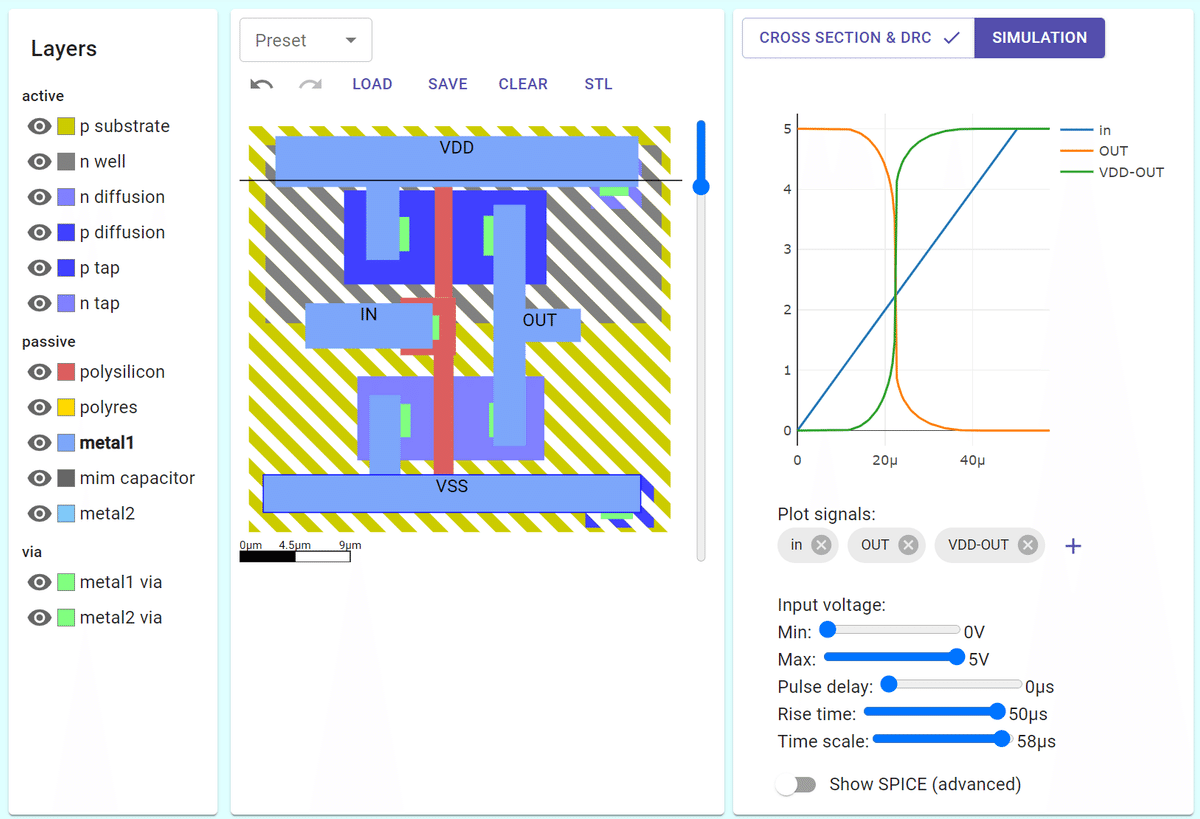

電圧の差を取ることもできます."VDD-OUT" をプロットするとこんな感じ.

あと,絶対値 (abs) なんかも使えます.なお,プロットできない信号 (存在しないラベルなど) があると,すべてのプロットが消えます.突然グラフが出なくなった,という場合は Plot signals から信号を消していきましょう.

3.7 SPICEネットリストの確認

SPICEネットリストを見せろ! という人のために,"Show SPICE" でネットリストを見ることができます.

回路部分だけ抜き出すと,こんな感じ.気になる人は見ましょう.

* Extracted circuit:

M1000 OUT IN VSS VSS nmos w=6.84u l=1.62u

+ ad=50.4792p pd=28.44u as=42.4764p ps=26.1u

M1001 OUT IN VDD VDD pmos w=7.65u l=1.44u

+ ad=58.5225p pd=30.6u as=56.457p ps=30.06u

C0 IN OUT 0.02fF

C1 OUT VDD 0.09fF

C2 IN VDD 0.04fF

4.(おまけ) 3Dで見てみる

Siliwiz は STL をエクスポートできるので,適当な3D CAD にインポートすれば立体構造を見ることができます.ただし,via がちゃんとつながっていなかったり,完全なものではありません.

5.レイヤーの意味

それぞれのレイヤーが何なのか,は書くと長くなるので別記事にしました.

この記事が気に入ったらサポートをしてみませんか?