A2PDP11 (5) パワーアップ構成レジスタ

初期化シーケンスを進めるために、パワーアップ構成レジスタ(Power-Up Configuration Resister)を設定します。

BOOT ADDRESS:Power-Up モード 3 の時の、起動アドレスの上位 7 ビット

<15:9> を指定します。起動アドレスの下位ビット 9 ビット <8:0> は 0 になります。

FPA HERE: 外付けの浮動小数点演算プロセッサが接続されているとき、

1 をセットします。

UNUSED: 未使用。

HALT OPTION: HALT 命令の動作を指定します。

1 = トラップ 4 を実行

0 = コンソール ODT に入る

POWER UP MODE:起動モードを指定します。

0 (00) = トラップ 24 を実行

1 (01)= コンソール ODT に入る

2 (10) = 17 773 000 から実行

3 (11) = ユーザ指定の BOOT ADDRESS から実行

POK (Power OK):電源が正常な時、1 をセットします。

top.sv を修正します。

DAL を上位 6 ビット dal_hi と、下位 16 ビット dal_lo に分け、下位ビットを入出力ポートに変更します。

BUFCTL に従い、入出力を切り替えます。

ALE の立ち下がりで、AIO を調べ、GP READ (4'b1110) または GP WRITE (4'b0101) なら、GP CODE を保存します。

GP CODE が、8'o000 または 8'o002 の時、パワーアップ構成レジスタに設定する値を DAL に出力します。

// DCJ11 TangNano interface

// TEST2 2024.07.28 Bus read, nanja.info

// TSET3 2024.08.03 Start-Up config, nanja.info

//

`default_nettype none

module top (

input wire [3:0] aio,

input wire [1:0] bs,

input wire [5:0] dal_hi, // DAL<21:16>

inout wire [15:0] dal_lo, // DAL<15:0>

input wire proc_n,

input wire bufctl_n,

input wire ale_n,

input wire strb_n,

input wire sctl_n,

input wire map_n,

input wire abort_n,

input wire clk,

input wire mclk,

output wire dir

);

logic sclk;

Gowin_rPLL u_rpll(

.clkout(sclk), //output clkout 72MHz

.clkin(clk) //input clkin 27MHz

);

// AIO CODE

parameter NIO = 4'b1111;

parameter GP_READ = 4'b1110;

parameter INTERRUPT_ACK = 4'b1101;

parameter INST_READ = 4'b1100;

parameter READ_NBUSLOCK = 4'b1011;

parameter READ_BUSLOCK = 4'b1010;

parameter DATA_READ = 4'b0111;

parameter DEMAND_READ = 4'b0110;

parameter GP_WRITE = 4'b0101;

parameter BYTE_WRITE = 4'b0011;

parameter WORD_WRITE = 4'b0001;

// GP CODE

parameter POWER_UP0 = 8'o000;

parameter POWER_UP2 = 8'o002;

assign dir = ~bufctl_n;

logic [15:0] dal_out;

assign dal_lo = bufctl_n ? 16'bz: dal_out;

always_ff@(negedge bufctl_n) begin

if ((gp_code == POWER_UP0) || (gp_code == POWER_UP2)) begin

dal_out <= 16'b1000001_0_0000_0_11_1;

// BOOT_ADDRESS, FPE, UNUSED, HALT, MODE, POK

end else begin

dal_out <= 0;

end

end

logic [7:0] gp_code;

always_ff@(negedge ale_n) begin

if ((aio == GP_READ) || (aio == GP_WRITE)) begin

gp_code <= dal_lo[7:0];

end else begin

gp_code <= 8'b11111111;

end

end

logic [3:0] t;

logic stretch;

always_ff@(posedge clk) begin

if (strb_n) begin

t <= 1;

end else begin

if (sctl_n == 0) begin

t <= 4;

end else begin

t <= t + 1'b1;

end

end

end

endmodule

`default_nettype wire初期化シーケンスのフローチャート前半を再掲します。

パワーアップ構成レジスタを、MODE = 3、BOOT ADDRESS = 101 とした時の動作を観察してみます。

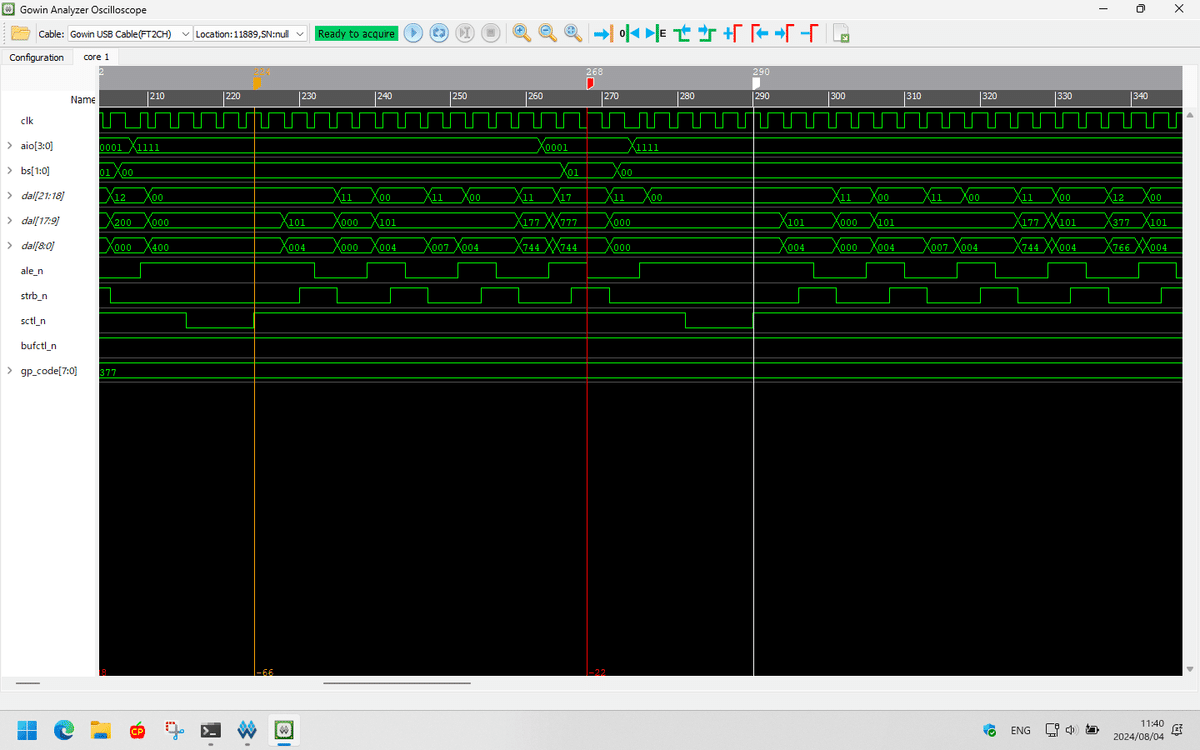

下図の、黄色マーカー部分が GP CODE 002 です。白マーカー部分で、DAL がパワーアップ構成レジスタ値を示しています。

最下位ビットの POK が 1 なので、赤マーカー部 キャッシュ制御レジスタ CCR の設定に進みます。DAL が CCR レジスタのアドレス 17777746、AIO がバスワード書き込み 0001、BS がシステムレジスタ 01 となっています。書き込みデータはオレンジマーカー部の DAL 000400 です。ビット 8 のフラッシュキャッシュビットを 1 に設定することを示します。

次に、メモリーシステムエラーレジスタ MSER のクリアに進みます。下図、赤マーカー部で、DAL が MSER のアドレス 17777744、AIO がバスワード書き込み 0001、BS がシステムレジスタ 01 を示しています。書き込みデータは白マーカー部の 000000 です。

次に、CPU エラーレジスタに 177766 を書き込みます。NIO なので、バスからはわかりません。

次に、CPU エラーレジスタの値を読み出します。下図の、赤マーカー部で、DAL が CPU エラーレジスタのアドレス 17777766、AIO がデータリード 1001、BS が 内部レジスタ 11 となっています。

次に、CPU エラーレジスタに 0 を書き込みます。NIO なので、バスからはわかりません。

初期化シーケンスの後半部分に移ります。

先ほど読み出した、CPU エラーレジスタの値が、書き込んだ 177766 と一致するか調べます。NIO なので、バスからはわかりません。一致すると GP CODE 220 が生成されます。

下図の、赤マーカー部が、GP CODE 220 の生成を示します。AIO が 汎用書き込み 0101、DAL<7:0> が 220 となっています。GP WRITE 220 は、マイクロ診断テスト 1 が成功したことを示します。

次に、アドレス 00000000 を読み出します。下図、白マーカー部で、AIO がデータ読み出し 1001、BS が 00 メモリ、DAL が 00000000 となっているのがわかります。この時、NXM (Non-existent memory) アボートが起きなければ、アドレス 17777700 の読み出しに進みます。

下図の、オレンジマーカー部で、AIO がデータ読み出し 1001、BS が外部 I/O 10、DAL が 1777700 となっているのがわかります。通常は、このアドレスに外部 I/O に割り当てることはありませんので、NXM アボートが発生します。今回は、アボート処理を実装していないので、GP CODE 224 (マイクロ診断テスト 2 成功) の生成はスキップされます。

次に、RCSR (レシーバ制御および状態レジスタ) の読み出しに進みます。下図の白マー株で、AIO がデータ読み出し 1001、BS が外部 I/O 10、DAL が RCSR のアドレス 17777560 となっているのがわかります。

次に、NXM アボートのテストに進みます。アボートが発生しなければ、GP CODE 230 (マイクロ診断テスト 3 成功) を生成します。下図の赤マーカー部で、AIO が汎用ワード書き込み 0101、DAL<7:0> が 230 になっているのがわかります。

次に、パワーアップオプション(MODE)により、処理が分岐します。今回は、MODE = 3、BOOT ADDRESS = 101 を指定したので、PC に 101000 がセットされます。 PS は 340 となります。下図、白マーカー部で、AIO が命令読み出し 1000、BS がメモリ 00、DAL が 101000 となっているのがわかります。読み出した命令コード 000000 は、HALT 命令を示します。オレンジマーカー部は、AIO 1100 で、命令の先読みを表します。DAL 次のアドレス 101002 を示しています。

参考文献

DCJ11 Microprocessor User's Guide, 8.3 POWER-UP AND INITIALIZATION, 1983

DEC Semiconductor Databook, Initialization, pp 1-277, 1986

DEC Semiconductor Databook V1, Initialization, pp. 1-283, 1987

この記事が気に入ったらサポートをしてみませんか?