Tang Nano 9K で Apple II を再現する(3)垂直タイミング

第四章 Video Timing 前半

回路図 C-3 の残りの垂直信号生成部を video_address.sv に加えます。

第二回で示したコードには、74LS161 の RC 信号に誤りがあったので修正してあります。

`default_nettype none

module a2_video_address (

input wire ldps_n,

output wire h0,

output wire h1,

output wire h2,

output wire h3,

output wire h4,

output wire h5,

output wire hpe_n,

output wire va,

output wire vb,

output wire vc,

output wire v0,

output wire v1,

output wire v2,

output wire v3,

output wire v4,

output wire v5

);

// D14:74LS161

logic [3:0] d14_q;

logic d14_pen;

logic d14_rc;

always_ff@(posedge ldps_n) begin

if (!d14_pen) begin

d14_q <= 4'b0;

end else begin

d14_q <= d14_q + 1'b1;

end

end

assign d14_rc = d14_q[3] & d14_q[2] & d14_q[1] & d14_q[0];

assign d14_pen = d13_q[2];

// D13:74LS161

logic [3:0] d13_q;

logic d13_pen;

logic d13_rc;

logic d13_et;

always_ff@(posedge ldps_n) begin

if (!d13_pen) begin

d13_q <= {d13_q[3], 3'b100};

end else if (d13_et) begin

d13_q <= d13_q + 1'b1;

end

end

assign d13_rc = d13_q[3] & d13_q[2] & d13_q[1] & d13_q[0] & d13_et;

assign d13_pen = d13_q[2];

assign d13_et = d14_rc;

// D12:74LS161

logic [3:0] d12_q;

logic d12_pen;

logic d12_rc;

logic d12_et;

always_ff@(posedge ldps_n) begin

if (!d12_pen) begin

d12_q <= {1'b1, d13_rc, 2'b01};

end else if (d12_et) begin

d12_q <= d12_q + 1'b1;

end

end

assign d12_rc = d12_q[3] & d12_q[2] & d12_q[1] & d12_q[0] & d12_et;

assign d12_pen = ~d11_rc;

assign d12_et = d13_rc;

// D11:74LS161

logic [3:0] d11_q;

logic d11_pen;

logic d11_rc;

logic d11_et;

always_ff@(posedge ldps_n) begin

if (!d11_pen) begin

d11_q <= {1'b0, d12_rc, d12_rc, 1'b1};

end else if (d11_et) begin

d11_q <= d11_q + 1'b1;

end

end

assign d11_rc = d11_q[3] & d11_q[2] & d11_q[1] & d11_q[0] & d11_et;

assign d11_pen = ~d11_rc;

assign d11_et = d12_rc;

assign h0 = d14_q[0];

assign h1 = d14_q[1];

assign h2 = d14_q[2];

assign h3 = d14_q[3];

assign h4 = d13_q[0];

assign h5 = d13_q[1];

assign hpe_n = d13_q[2];

assign va = d13_q[3];

assign vb = d12_q[0];

assign vc = d12_q[1];

assign v0 = d12_q[2];

assign v1 = d12_q[3];

assign v2 = d11_q[0];

assign v3 = d11_q[1];

assign v4 = d11_q[2];

assign v5 = d11_q[3];

endmodule

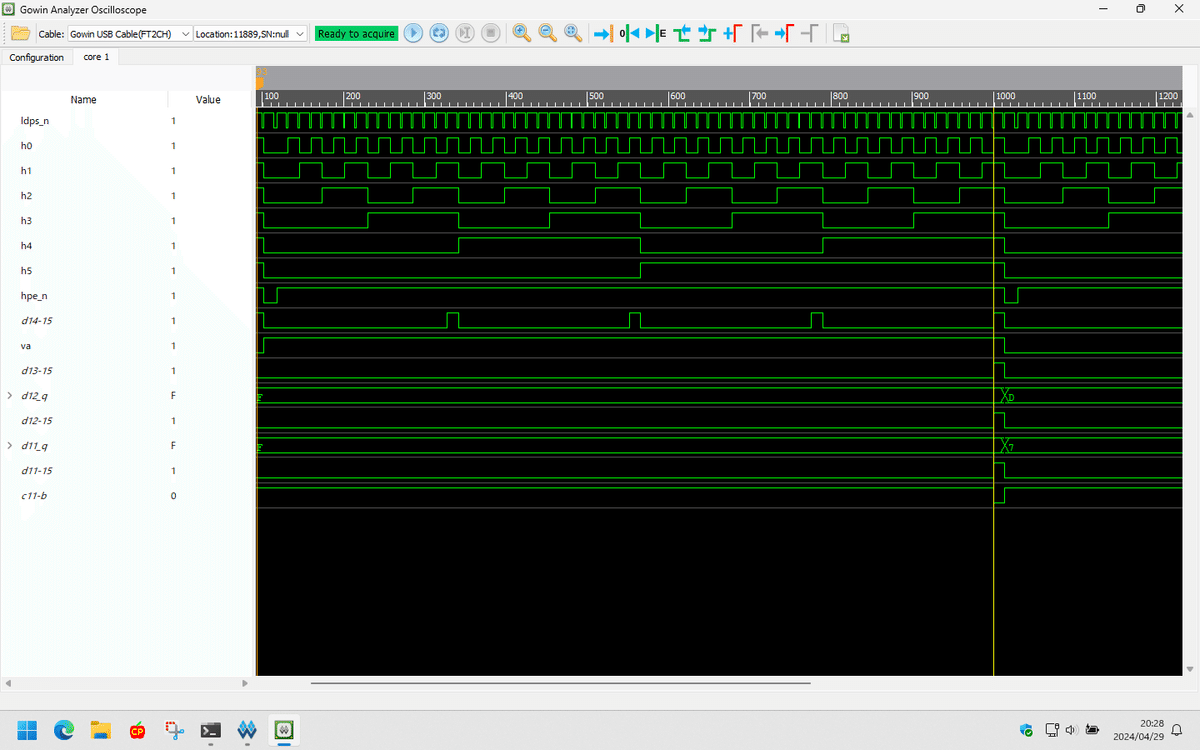

`default_nettype wire水平タイミングを確認しておきます。水平カウンタ h0-5 は、0 が二つ続き、その後 1 から 63 まで ldps_n に同期してカウントアップします。最初の 0 の期間は、1117 nsec で、それ以降は 987 nsec です。

垂直タイミング va は、1 ライン毎に反転します。

vb から v5 は 8 ビットのカウンタとして動作し、初期値の 125 から 255 まで 2 ライン毎にカウントアップします。

va から v5 の 9 ビットが、垂直ビデオアドレスビットとなります。

参考文献

この記事が気に入ったらサポートをしてみませんか?