みてわかる電子回路「差動増幅回路」

ここでは差動増幅回路の必要性とその中身の動作原理について解説します。

(ご利用にあたり免責事項をご一読ください)

そもそもなぜ差動増幅回路が必要なのか?

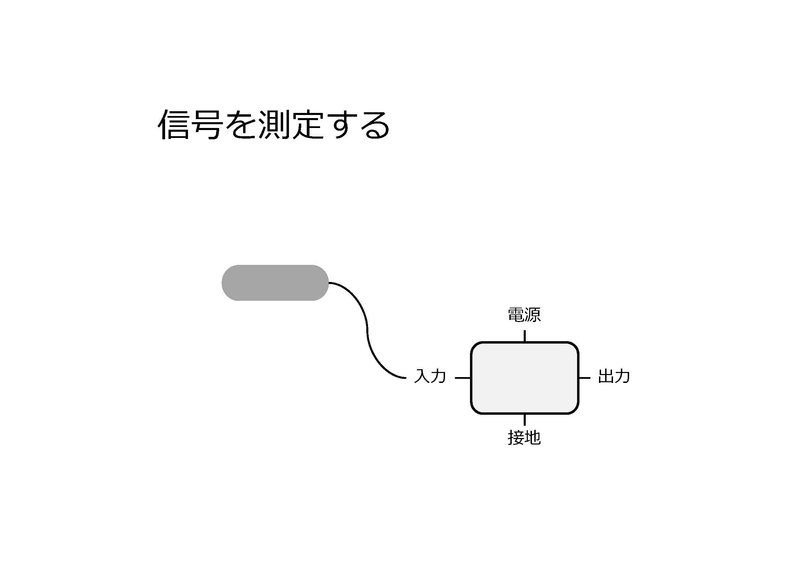

信号増幅回路の用途の一つは、自然界のなかの信号を読み取り、増幅してデータを取得することです。いままで学んできた電圧信号増幅回路を用いることで、このような測定が可能になります。

この増幅回路は、接地、電源、入力、出力、の計4つの端子を持つと見なすことができます。このような増幅回路は、接地を基準として、入力された信号電圧を読み取り、増幅して、出力するという機能を持っているといえます。

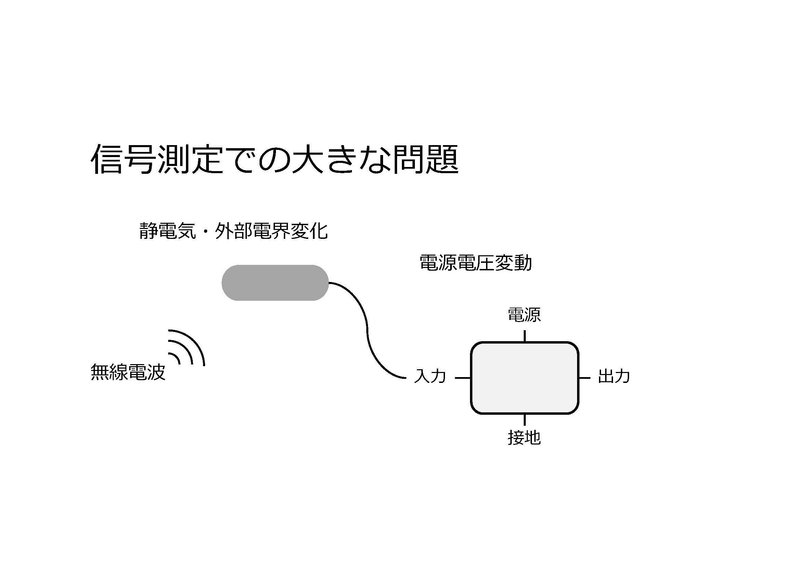

この信号測定での大きな困りごとの一つは、関心のある信号をかき消すほどのノイズです。たとえば、静電気や外部電界変化などによる電位変動、無線電波からの起電力、電源電圧の変動、など様々なノイズ要因があるなかで回路を動作させなければなりません。これらのノイズを含む信号をそのまま増幅しても、ノイズ信号も含めて増幅されてしまうため関心のある信号を読み取ることができない、という問題が生じてしまいます。

このような状況を何とか克服して測定を成功させるには、関心のないノイズ信号を除去し、関心のある信号のみを取り出す必要がありますが、どうすればよいのでしょうか?

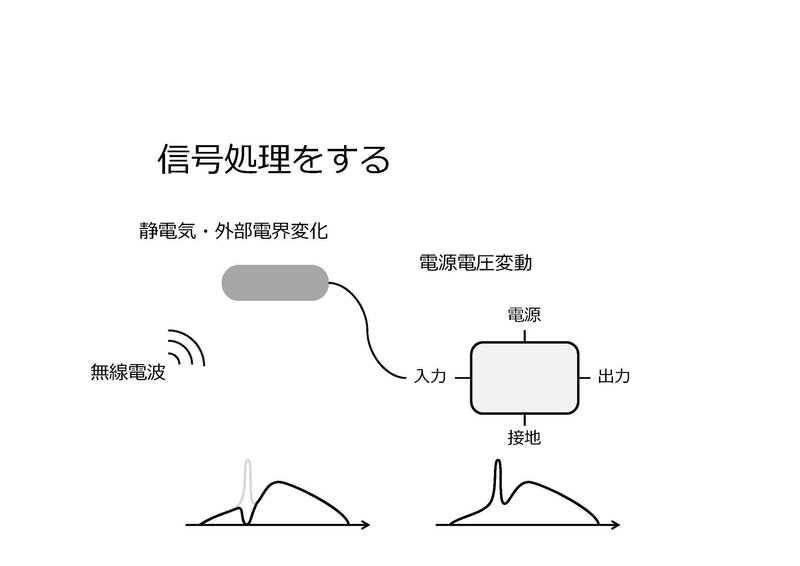

もしノイズ信号の周波数が最初から分かっているのであれば、測定後の信号処理によってノイズ除去できるでしょう。たとえば商用電源周波数の電磁波に由来するノイズは最初から周波数がわかっているので、その成分だけを除去すればよいですよね。

しかし多くの場合、ノイズの周波数は未知であるうえに、関心のある信号の周波数帯に重なっていることもあります。このため、フィルター回路や測定後の信号処理でノイズ成分のみを検出して除去することは万能とはいえません。

静電気や外部電界変化などによる測定対象全体の電位変動は、測定対象の1点を測定回路の基準となる電圧(最低電位の電源や接地など)と接続することで低減することができます。このような状況では、測定対象の電位が回路の接地によって固定されるため、測定対象全体にわたる電位変化は抑制され、測定回路からの信号に影響しません。

しかし、これでもまだ接地端点と測定端点の間に発生するノイズ信号は除去できずにいます。たとえば、無線電波からの起電力に起因するノイズや、測定回路の電源電圧そのものの変動によるノイズ信号は除去できていません。

ここで、ノイズの種類によっては、二つの測定端点を用意し、その間の差信号のみを測定することで低減できる場合があります。また二つの測定端点の信号を測定する回路で電源を共通にすれば、電源電圧の変動に由来するノイズ信号を低減することも可能になります。

このように、測定対象での一つの測定点のみからの信号を測定するのではなく、二つの測定端点間での差信号を測定することで、ノイズ成分の多くを除去することができます。

差動増幅回路とは?

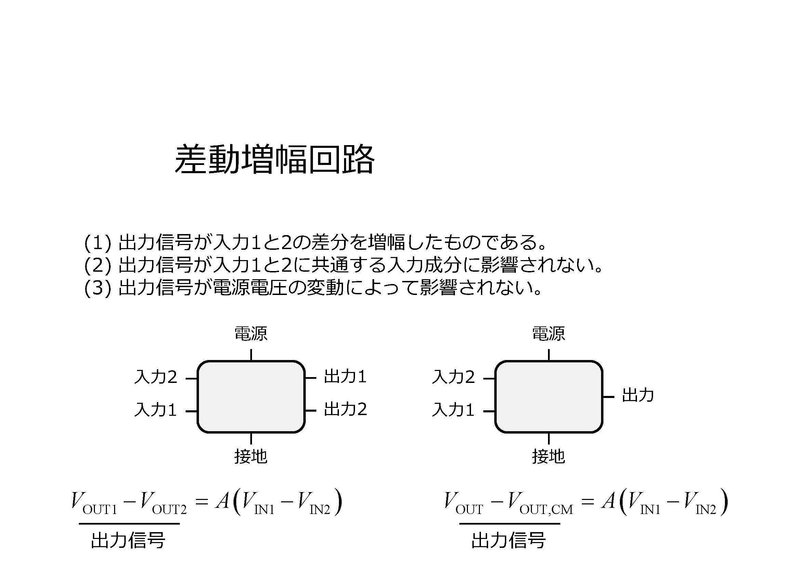

以上のような背景から、信号の差分を増幅する回路が有用そうだということがわかります。

このような回路は「差動増幅回路」と呼ばれ、次の要件を満たしてほしい回路です:

(1) 出力信号が入力1と入力2の差分を増幅したものである。

(2) 出力信号が入力1と入力2に共通する入力成分に影響されない。

(3) 出力信号が電源電圧の変動によって影響されない。

ここで、出力端子を2つもち、出力信号が二つの出力端子間の差信号となる回路を「2入力2出力の差動増幅回路」あるいは「全差動増幅回路」とよぶことにしましょう。この場合の増幅率をAとすると、下記スライド中の左下式のように書けます。

一方、出力端子を1つだけ持ち、出力信号が基準出力電圧 $${ V_{\rm{OUT, CM}} }$$ [V] との電位差として出力される回路を「2入力1出力の差動増幅回路」とよぶことにします。この場合の増幅率を$${ A }$$とすると、下記スライド中の右下式のように書けます。

MOSFETによる差動増幅回路の動作

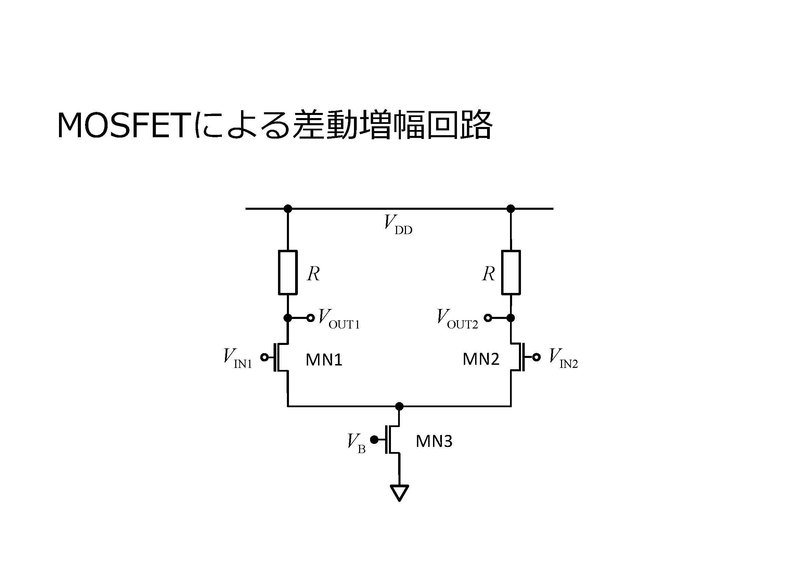

下記スライド中の回路は、最も基本的な差動増幅回路をN型MOSFET(略してNMOS)によって実現したものです。この回路は次のようなものです:

(1) NMOSと抵抗を直列接続したもの二つが、並列接続されている。

(2) 二つのNMOS (MN1, MN2)は共に同じ特性を持ち、その動作が飽和状態に維持されていると仮定する。

(3) 二つの抵抗は共に同じ値を持つ。

(4) それらが一つのNMOS (MN3)に接続されており、ゲートに一定のバイアス電圧$${ V_{\rm{B}} }$$ [V] が印加されており、飽和状態が維持されている。

(5) NMOSのゲートが二つの入力端子となっている。

(6) 二つの出力端子をもち、それらはいずれもNMOSのドレインに接続されている。

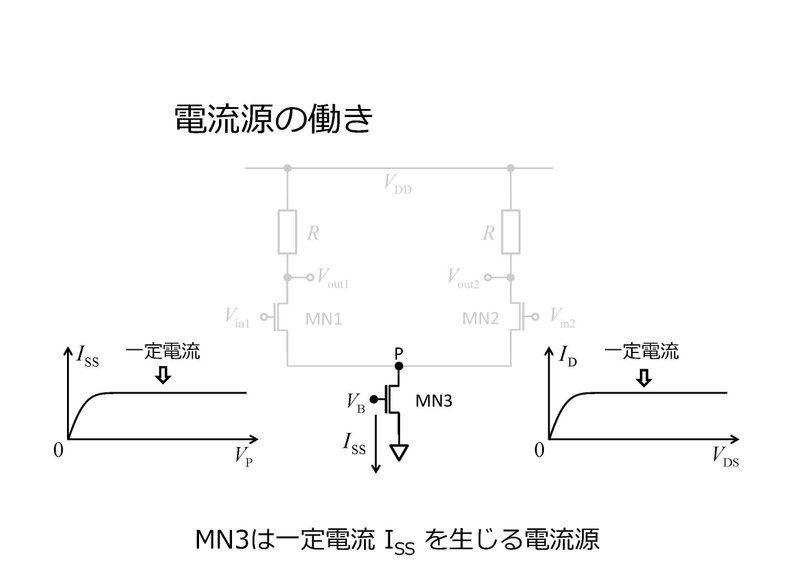

この回路の一番下にあるNMOS(MN3)は、ドレイン電圧によらずほぼ一定の電流を流す「電流源」の役割を担っています。NMOSのゲートには一定電圧 $${ V_{\rm{B}} }$$ [V] が印加されていますが、このときNMOSのドレイン電圧 $${ V_{\rm{DS}} }$$ [V] に対するドレイン電流 $${ I_{\rm{D}} }$$ [A] の関係は、下記スライド中の右下図のようになっています。ドレイン電圧 $${ V_{\rm{DS}} }$$ は回路図中の端点Pの電圧 $${ V_{\rm{P}} }$$ [V] に等しく、ドレイン電流 $${ I_{\rm{SS}} }$$ [A]はこの回路全体に流れます。この電流は、トランジスタの $${ I_{\rm{D}} - V_{\rm{DS}} }$$ 特性から、この回路が飽和状態であり続ける限りほぼ一定に保たれているはずですよね。このようにして、確かにMN3は電圧によらず決められた電流を生じる「電流源」として機能しています。

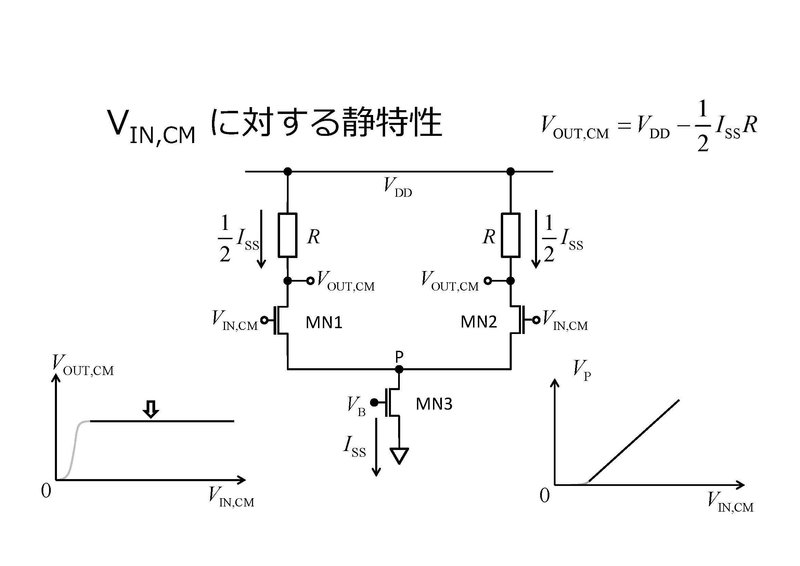

ここで、時間的に変化しない直流電圧 $${ V_{\rm{IN,CM}} }$$ [V] が、二つの入力端子に共通して生じた場合を考えましょう。

それぞれのNMOSに生じる電流量はいずれも $${ I_{\rm{SS}}/2 }$$ [A] であり、 $${ V_{\rm{IN,CM}} }$$ の値によらず一定値です。また、二つの出力端子の電圧 $${ V_{\rm{OUT,CM}} }$$ [V] はいずれも下記スライド中右上の式のように表され、やはり $${ V_{\rm{IN,CM}} }$$ の値によらず一定値となります。

なお、端子 P の電圧 $${ V_{\rm{P}} }$$ は、MN1およびMN2が流す電流量が $${ I_{\rm{SS}}/2 }$$ となるように $${ V_{\rm{IN,CM}} }$$ に追随して変化します。

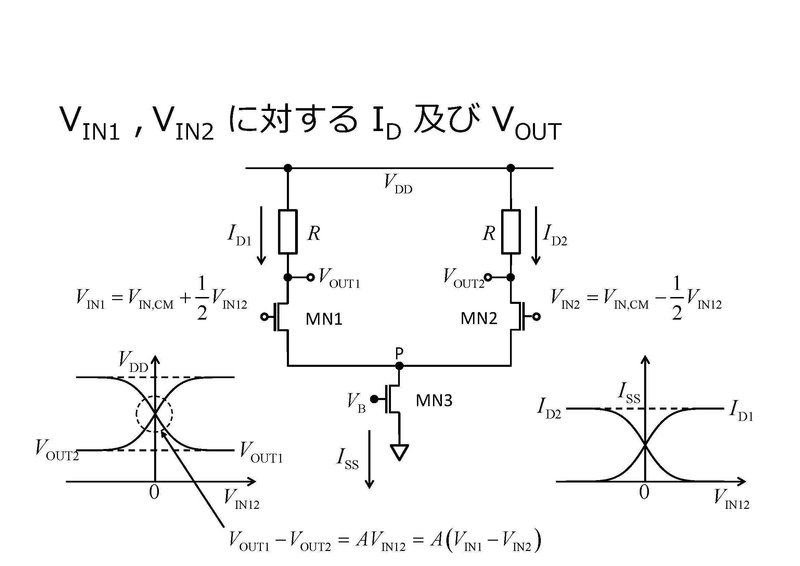

それでは、二つの入力端子に直流電圧 $${ V_{\rm{IN1}} }$$ と $${ V_{\rm{IN2}} }$$ が印加されたときを考えましょう。

この回路では、 $${ V_{\rm{IN,CM}} }$$ の変化に対して $${ I_{\rm{D1}} }$$, $${ I_{\rm{D2}} }$$ が一切変化せず、したがって $${ V_{\rm{OUT1}} }$$, $${ V_{\rm{OUT2}} }$$ も変化しません。

つまり、この回路では冒頭に説明した差動増幅回路の性質(2)「出力信号が入力1と入力2に共通する入力成分に影響されない」を満たしています。

このため、回路動作を考える上で $${ V_{\rm{IN1}} }$$ と $${ V_{\rm{IN2}} }$$ のなかで共通した電圧成分は無視してもよく、$${ V_{\rm{IN12}} = V_{\rm{IN1}} - V_{\rm{IN2}} }$$ のみを考えればよいことになります。すなわち、回路解析において

$${ V_{\rm{IN1}} = V_{\rm{IN,CM}} + V_{\rm{IN12}}/2 }$$

$${ V_{\rm{IN2}} = V_{\rm{IN,CM}} - V_{\rm{IN12}}/2 }$$

であるとしても一般性を失いません。

このように考えると、$${ V_{\rm{IN12}} }$$ と $${ I_{\rm{D1}} }$$, $${ I_{\rm{D2}} }$$ の関係は下記スライド中の右下図のようになります。

(a) $${ V_{\rm{IN12}}>0 }$$ のとき: MN1に流れる電流 $${ I_{\rm{D1}} }$$ が増加し、MN2に流れる電流 $${ I_{\rm{D2}} }$$ が減少する。やがて $${ I_{\rm{D1}} = I_{\rm{SS}} }$$, $${ I_{\rm{D2}} = 0 }$$ となると、その後は電流は変化しない。

(b) $${ V_{\rm{IN12}}<0 }$$ のとき: MN2に流れる電流 $${ I_{\rm{D2}} }$$ が増加し、MN1に流れる電流 $${ I_{\rm{D1}} }$$ が減少する。やがて $${ I_{\rm{D1}} = 0 }$$, $${ I_{\rm{D2}} = I_{\rm{SS}} }$$ となると、その後は電流は変化しない。

このような $${ I_{\rm{D1}} }$$, $${ I_{\rm{D2}} }$$ の変化が与えられれば、 $${ V_{\rm{OUT1}} }$$, $${ V_{\rm{OUT2}} }$$ の変化は抵抗による $${ V_{\rm{DD}} }$$ からの電圧降下を考えることで容易に得られ、スライド中の左下図のようになります。

この図を見ると、$${ V_{\rm{IN12}} }$$ がある程度小さいところでは、近似的に $${ V_{\rm{OUT2}} - V_{\rm{OUT1}} }$$ が $${ V_{\rm{IN12}} }$$ に比例して変化していると見なすことができますね。つまり二つの出力電圧の差は、入力電圧 $${ V_{\rm{IN12}} }$$ に比例することになります。

以上から、この回路は差動増幅回路の性質(1)「出力信号が入力1と入力2の差分を増幅したものである」を満たしています。

さらに、この回路での出力信号は $${ V_{\rm{OUT1}} }$$ と $${ V_{\rm{OUT2}} }$$ の差であるため、$${ V_{\rm{DD}} }$$ に依存しません。つまり、この回路は差動増幅回路の性質(3)「出力信号が電源電圧の変動によって影響されない」も大まかには満たしています。増幅率 $${ A }$$ が電源電圧によって変動する可能性は残されていますが、小信号等価回路による解析により、このような影響は基本的には現れてこないことがわかります。

以上から、このトランジスタ回路は確かに差動増幅回路の3つの要件を満たしていますね。