みてわかる電子回路「NチャネルMOSFETの静特性」

ここではNチャネルMOSFET(NMOS)の静特性について簡単に見ていきましょう。

(ご利用にあたり免責事項をご一読ください)

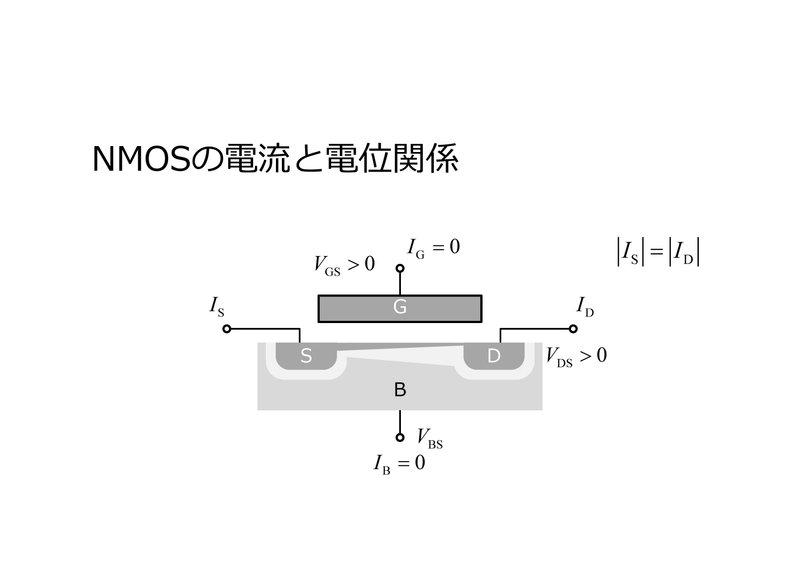

NMOSの電流と電位関係

まずNMOSでの電流と電圧の関係について大まかに考えておきましょう。NMOSの各領域を独立した端子と考えると、ソース(S)、ドレイン(D)、ゲート(G)、基板(B) の4個の端子を持つ素子として見なすことができるのでした。それぞれの端子に流れ込む電流を $${I_{\rm{S}}}$$ [A], $${I_{\rm{D}}}$$ [A], $${I_{\rm{G}}}$$ [A], $${I_{\rm{B}}}$$ [A] とし、ソースを基準としたドレイン、ゲート、基板の電圧をそれぞれ $${V_{\rm{DS}}}$$ [V], $${V_{\rm{GS}}}$$ [V], $${V_{\rm{BS}}}$$ [V] としましょう。

集積回路の場合、基板端子は回路の中で最も低い電圧にしておきます。たとえば回路が接地(0V)から電源電圧 $${V_{\rm{DD}}}$$(>0)の間で駆動するのであれば、基板は必ず接地されます。こうすると、ソースやドレインに $${0 < V < V_{\rm{DD}}}$$ のどのような電圧が印加されたとしても、ソース基板間およびドレイン基板間のPN接合は常に逆バイアスされるので、不要な電流が発生せずNMOSが正常に動作します。

なお、集積回路ではなく単一のNMOSが単一のチップに搭載されている場合は、基板はソースと接続されていることが多いです。

このようにするとソースやドレインは基板との間で常に逆バイアスされているため、基板に生じる電流 $${I_{\rm{B}}}$$ [A] はゼロとなります。また、ゲートは他の端子と絶縁膜を介して接続されているため、電圧印加による電界が伝わることはあっても、電流が生じることはありません。このため、ゲートに生じる電流 $${I_{\rm{G}}}$$ [A] も常にゼロであるとみなせます。このように、$${ I_{\rm{B}} = I_{\rm{G}} = 0}$$ であるため、ソースに生じた電流 $${I_{\rm{S}}}$$ は全てドレインに生じる電流 $${I_{\rm{D}}}$$ となります(電流の向きが符号で現れるので下図では絶対値記号を付けて大きさの関係のみ表しています)。ソースに対してドレインに正電圧を印加し、かつソースに対してゲートにチャネルが形成されるほど十分大きな正電圧が印加すれば、ソースドレイン間に電流が生じてNMOSがONとなります。

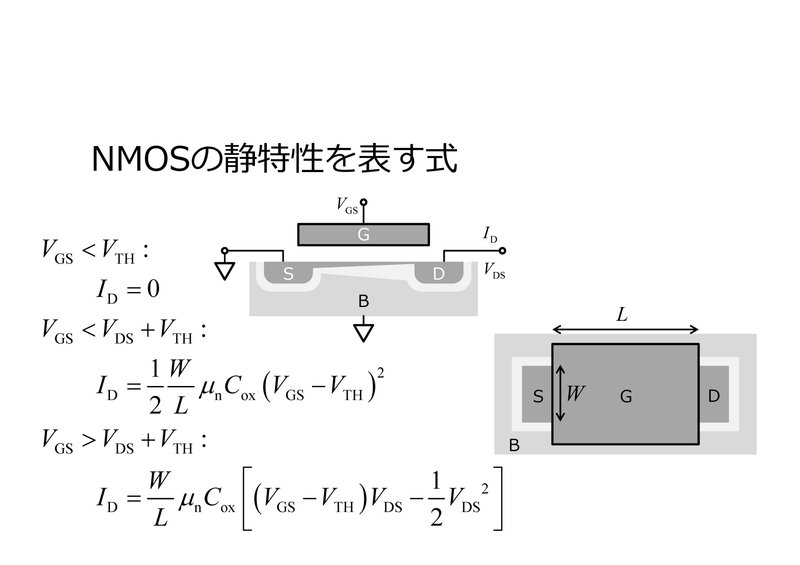

NMOSの静特性を表す数式

NMOSの静特性に関する詳細な説明は省略しますが、結果からいうと下図中の数式によって表されます。ただし $${L}$$ [m] はチャネル長、$${W}$$ [m] はチャネル幅、$${\mu_{\rm{n}}}$$ [m$${^2}$$/Vs] は電子の移動度、そして $${C_{\rm{ox}}}$$ [F/m$${^2}$$] はゲート絶縁膜がもつ単位面積当たりの電気容量を表します。

これらのパラメータ値はNMOSが製造された時点で既に決定しており、その素子の特性を表す指標です。NMOSを回路の中で使用する人はこれらを変更することはできません。

このNMOSを使用する人は、ソース・ドレイン・ゲートに印加する電圧を変更することでNMOSに流れる電流を制御します。ここで絶縁膜基板界面に十分な密度の電子が集結し、ソースドレイン間がチャネルで接続されるためには、ゲートにある一定以上の正電圧を印加する必要がありますよね。このような電圧を「しきい値電圧」とよび、$${V_{\rm{TH}}}$$ [V] と書きます。もし $${ V_{\rm{GS}} < V_{\rm{TH}} }$$ であれば $${I_{\rm{D}}}$$ は殆ど流れず、$${ V_{\rm{TH}} < V_{\rm{GS}} }$$ となって初めてNMOSが動作しON状態となります。

なお、実際のNMOSではチャネル長変調効果やサブスレッショルド電流など2次的な効果が表れますが、これらについては将来どこかで言及する必要が出たときに簡単に紹介することとしましょう。

NMOS静特性(ID-VDS特性)

ではこの静特性の式を基にして、基板およびソースを接地し、ある $${ V_{\rm{GS}}}$$ [V] ($${> V_{\rm{TH}}}$$ )を印加した状態を考えましょう。ここで $${V_{\rm{DS}}}$$ [V] を 0V から徐々に正に増加させると、絶縁膜基板界面にチャネルが形成されてソースドレイン間に電流 $${I_{\rm{D}}}$$ [A] が生じます。このとき $${I_{\rm{D}}}$$ の $${V_{\rm{DS}}}$$ 依存性は下図のようになります。

この図で示された $${I_{\rm{D}}}$$ と $${V_{\rm{DS}}}$$ の関係において、電流がほぼ一定になりだすときの $${V_{\rm{DS}}}$$ は「ピンチオフ電圧」と呼ばれ、$${V_{\rm{P}}}$$ [V] などと書かれます。ピンチオフ電圧は $${ V_{\rm{P}} = V_{\rm{GS}} - V_{\rm{TH}} }$$ と与えられます。

NMOSが $${ V_{\rm{DS}} < V_{\rm{P}} = V_{\rm{GS}} - V_{\rm{TH}} }$$ で動作しているところは「線形領域」とよばれ、$${I_{\rm{D}}}$$ が $${V_{\rm{DS}}}$$ の増加にしたがって増加します。ソースドレイン間のチャネルの両端に印加される電圧が $${V_{\rm{DS}}}$$ に他ならず、これが増加することで電流量が増加するためです。

いっぽう $${ V_{\rm{P}} = V_{\rm{GS}} - V_{\rm{TH}} < V_{\rm{DS}} }$$ で動作しているところは「飽和領域」とよばれ、 $${I_{\rm{D}}}$$ が $${V_{\rm{DS}}}$$ によらずほぼ一定となります。

このようになる理由の詳細は省略しますが、大まかにいうと下記のような理由によります:

(a) 絶縁膜基板界面でゲートの正電圧 $${V_{\rm{GS}}}$$ が電子を集結させる能力は、絶縁膜界面付近での基板とゲートとの間の電位差によって決定される。

(b) $${V_{\rm{DS}}}$$ に正電圧を印加することで、ドレイン近傍にある絶縁膜界面付近での基板領域の電位が既に正で高くなっている。

(c) このため、ドレイン近傍では $${V_{\rm{GS}}}$$ により電子を集結させる効果が弱められており、電子の密度が小さくなっている。

(d) 結果的に、 $${V_{\rm{DS}}}$$ が正に大きいときにはドレイン近傍でチャネルが消失する。

(e) チャネルが消失しても電流は生じるが、その先さらに増加したドレイン電圧は電流の増加に寄与せず、電流は一定になる。

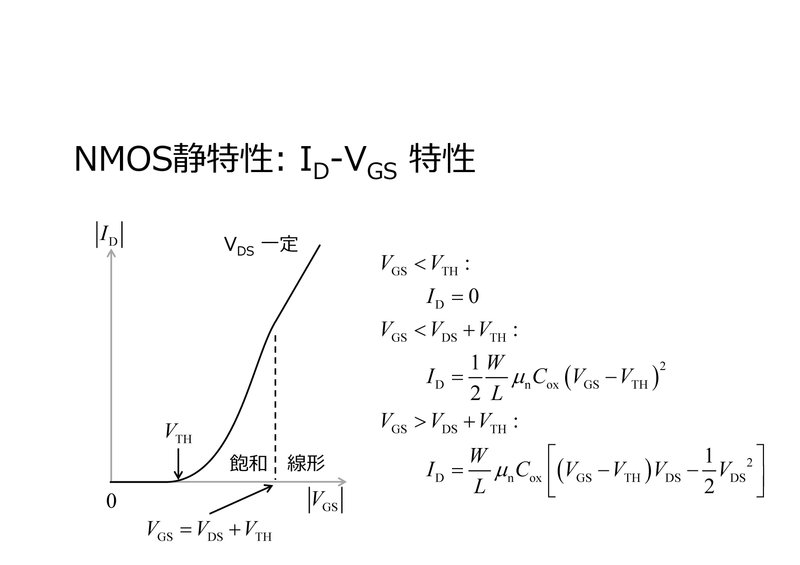

NMOS静特性(ID-VGS特性)

では最後に、基板およびソースを接地し、ある $${V_{\rm{DS}}}$$ [V] を印加した状態を考えましょう。ここで $${V_{\rm{GS}}}$$ [V] を 0V から徐々に正に増加させると、絶縁膜基板界面にチャネルが形成されてソースドレイン間電流 $${I_{\rm{D}}}$$ が生じます。このとき $${I_{\rm{D}}}$$ の $${V_{\rm{GS}}}$$ 依存性は下図のようになります。