3. 12AX7を用いた増幅回路

本節では、12AX7を用いて増幅回路を設計し、動作をシミュレーションします。

12AX7を用いた増幅回路の設計

まず、12AX7のEp-Ip特性図に負荷直線を引いたものを、次の図に示します。

電源を12Vとし、プレート電流の軸上240μAとの間に負荷直線を引いてみます。横軸上の12Vは電源電圧から決まります。縦軸上の240μAは、なるべくEp-Ip曲線と負荷直線が等間隔に交わるように決めてみました。

このときの負荷抵抗値はRp=12V÷240μA=50kΩとなります。ここで、Ep-Ip曲線の間隔がだいたい等間隔になるような範囲を取ると、プレート電圧が4Vから9Vの範囲となり、6.5Vあたりが中心になります。ここをバイアス点とします。

Ep-Ip曲線はグリッド電圧を0Vから0.1Vずつ-1.2Vまで小さくして引いたものが左から並んでいるので、バイアス点におけるEp-Ip曲線のグリッドバイアスは-0.5Vとなり、このときのプレート電流は110μAです。よって、カソード抵抗で-0.5Vのバイアスをグリッドに掛けるには、0.5V (500mV)を110μAで割って、4.5kΩとなります。

また、負荷直線上でグリッドバイアス-0.5Vの点を中心として、-0.3Vから-0.7Vまで0.4Vppの範囲を入力信号の振幅とします。このとき負荷直線上の信号はバイアスは-0.3Vから-0.7Vまで0.4Vppだけ動き、横軸のプレート電圧で見ると4Vから9Vまで5Vppだけ動きます。これより理想的な増幅率は5Vpp÷0.4Vpp=12倍となります。

さらに、入力の信号を0V中心にするためのハイパスフィルターは0.1μFと470kΩ、出力の信号を0V中心にするためのハイパスフィルターは0.1μFと470Ωにしました。これは、50kΩとこの470Ωの抵抗の並列の合成抵抗が交流信号に対する負荷になりますので、この合成抵抗が50kΩからあまり下がらないように、十分大きな抵抗値を出力に置いてあります。

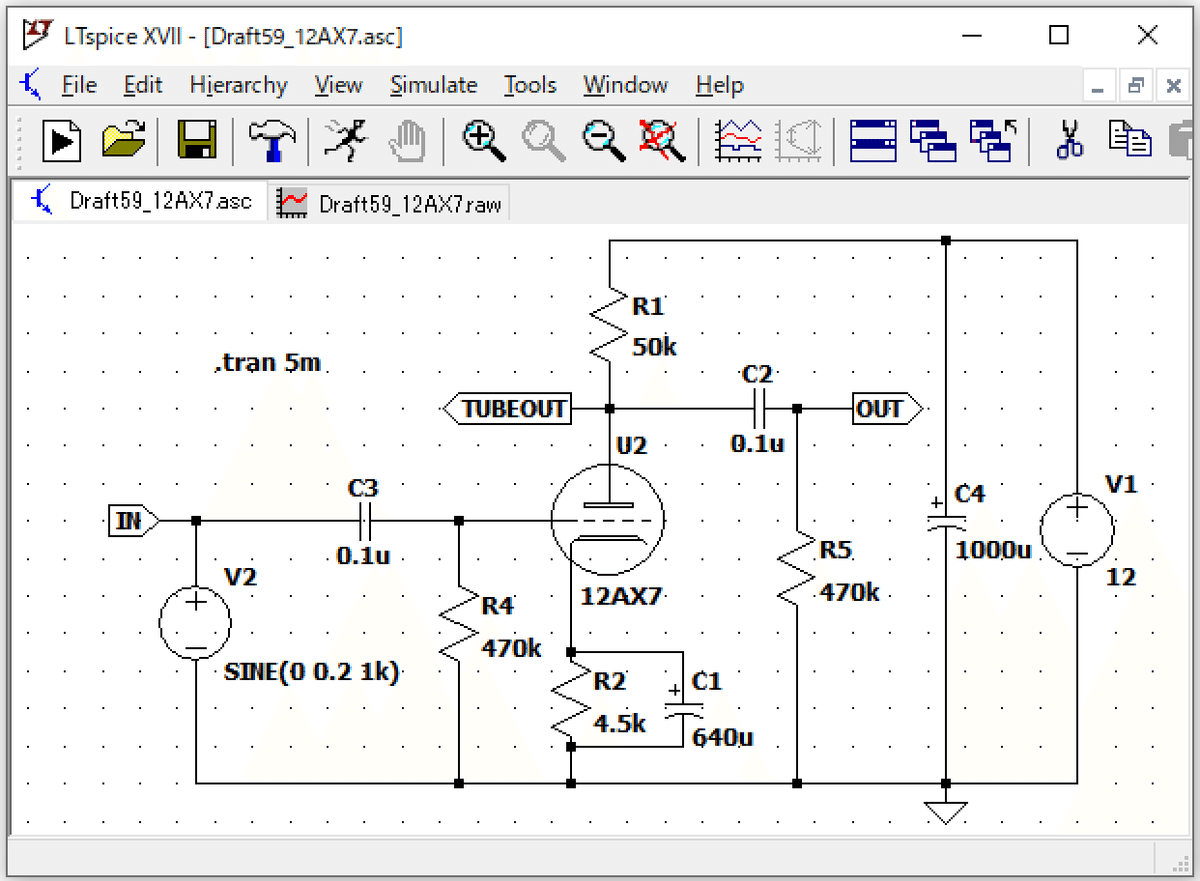

以上で次の回路図が完成しました。

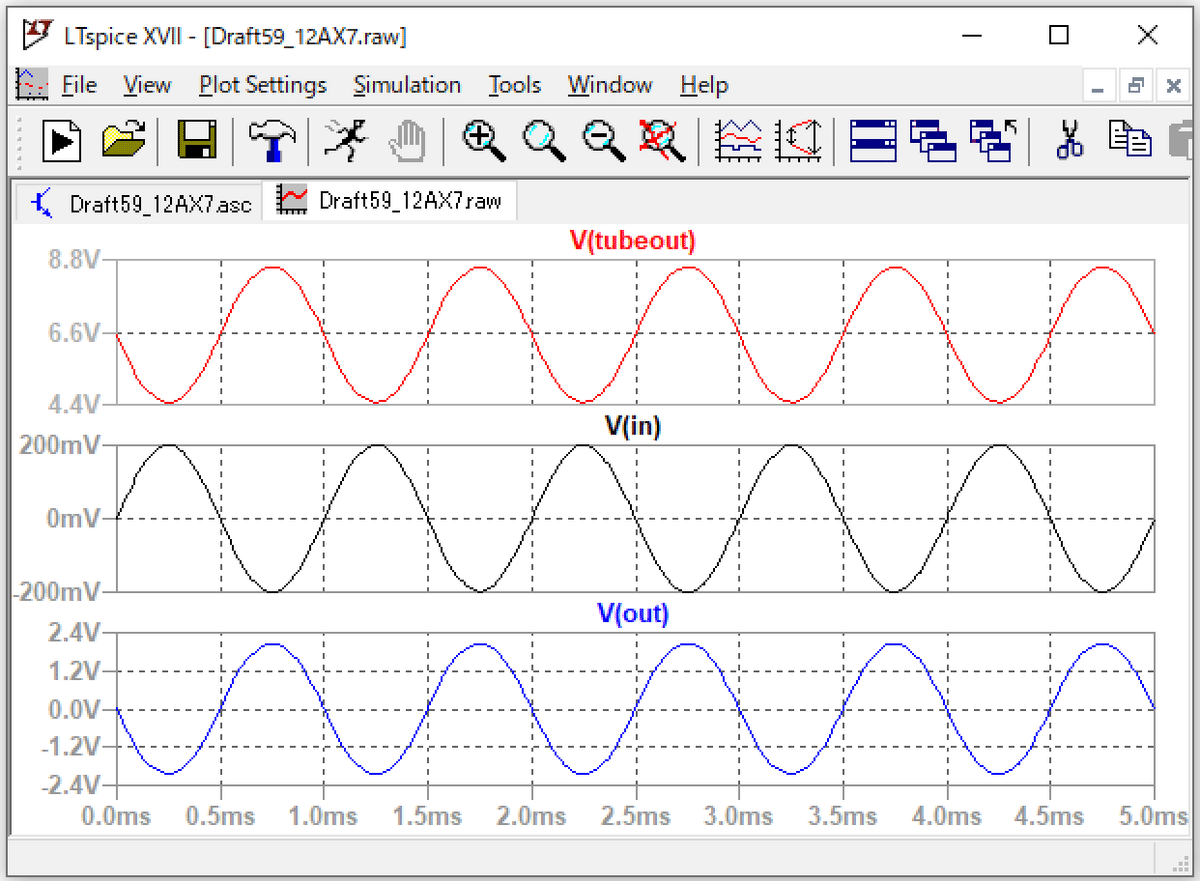

この回路に最大値0.2Vmax (0.4Vpp)の正弦波を入力したときの入出力波形を

次の図に示します。

このグラフでは、合わせて真空管のプレート電圧もプロットしてみました。3つのグラフは上から順にプレートの電圧、入力電圧、出力電圧です。だいたい計算通りの出力になっていることが分かります。また、プレートの電圧V(tubeout)を中心電圧が0VとなるようにシフトしたものがV(out)となっていることも見てとれます。

12AX7を用いた増幅回路の出力インピーダンスの改良

さて、この回路を改良してみます。上図の回路は、出力に付いている抵抗の値が大きいです。これは、出力インピーダンスが大きいことを意味します。次の回路やスピーカーへの接続を考えると、回路の出力インピーダンスはなるべく小さい方が使いやすいです。ここでは接合型FET (junction FET, JFET)を用いて出力インピーダンスを小さくします。

改良した回路を次の図に示します。

この回路の出力インピーダンスは、JFETのソース抵抗と出力についている2つの10kΩの並列の合成抵抗となるので、前の回路に比べるとかなり小さくなっていることが分かります。

この回路に最大値0.1Vmax (0.2Vpp)の正弦波を入力したときの入出力波形を

次の図に示します。

2つのグラフは上から順に入力信号の電圧、出力信号の電圧です。前の図と同じように入力信号が増幅されて出力されていることが見てとれます。

この記事が気に入ったらサポートをしてみませんか?