FIFO Generator

Xilinx のFPGA開発ツールである Vivado では多くのIPが提供されています。

FPGAに備わった機能のうち、メモリーや高速シリアル等の特別な機能を使用するためのIPです。

逆に言えば、IPを理解し使い熟せないと、高級なFPGAの機能の大部分が使い物になりません。

そんなわけで何回かに分けて、個人的によく使うIPの説明をしていきたいと思います。

※ この記事はVivado 2019.2、及びFIFO Generator ver13.2を用いて説明を行います。

まずは、First In First Outメモリ、通称FIFOです。

データを入力された順に蓄えて、入力されたのと同じ順番で出力するメモリのことをFIFOと呼びます。

ビデオデータや通信データのように、大量のデータを出力する装置ではよく使われるメモリ構成です。

FIFOのIPを使うためには、まずVivadoでプロジェクトを開いた状態で、Flow Navigatorの「IP Catalog」を選択します。

そうすると、 PROJECT MANAGERウィンドウの中に IP Catalog が開きます。

このウィンドウで使いたいIPを選択すればOKです。

今回はFIFOを使いたいので、Search窓にfifoと打ち込んでIPを絞り込んでから「FIFO Generator」を選びます。

因みに、この方法で作ったIPはVerilogかVHDLのソースコードとして作られます。

Block Designの中に組み込みたい場合には、Block Designを開いた状態で行えるAdd IPというコマンドを使って下さい(右クリックで呼び出すメニューの中にあります)。

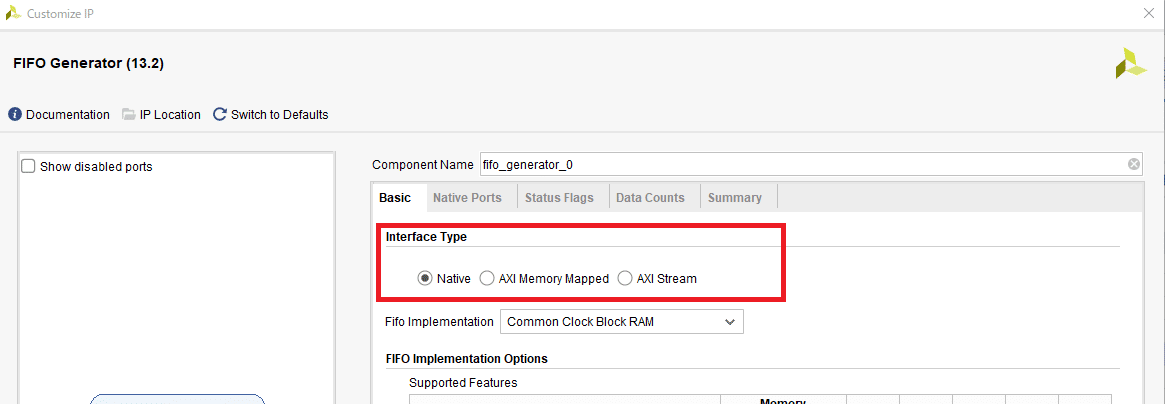

「FIFO Generator」を選択すると、設定ウィンドウが開かれます。これはIPを作った後からでも変更出来ます。

ここでFIFOの構造、必要な機能を決めて行きます。

始めにInterface Typeの説明です。

ここではNative、AXI Memory Mapped、AXI Streamの3種類があります。

ありますが、私個人としてはNativeしか使ったことがありません。

AXI Memory Mapped、AXI Streamを選択した場合には、FIFOのインターフェースがAXIインターフェースになったりAXI Streamになったりと、それはそれで使い道がありそうに見えるのですが、AXIもAXI Streamも、専用のIPが別にあったりします。

なので、このFIFO Generatorを使う場合にはNavite一択でいいです。

次の設定項目は FIFO Implementation です。

7種類の設定から、使いたいFIFOの構造を選択します。選択する構造の説明はすぐ下の FIFO Implementation Options の表に書かれている通りです。が、少し分かり難いので説明します。

FIFO Implementationの下矢印を押すと7つの選択肢が出ます。

この選択肢は、それぞれ下の表に対応しています。下の表には名称がありませんが、並び順は同じです。

一番上の Common Clock Block RAM の場合には、表の一番上の欄に対応しており、 これを選択中は太字で表示されています。

(1)~(5)となっているのは選択したFIFOが使用出来る機能で、Common Clock Block RAM では(3)を除く4つにチェックが入っています。それと同時に、表の下の文字列も、(3)の部分を除いて表示されています。(3)だけは薄文字で、この機能が使えないことを示します。

機能の内容が表の下の文字列に書かれていますが、ここもちょっと補足説明しておきましょう。

(1) Non-symmetric aspect ratios (different read and write data widths)

入出力のデータ幅が違う構造が可能です。

例えば、入力データ幅が16bitだった場合に、出力は16bit以外にも、8bitや32bitでも作れるということです。入力データ幅に対して出力が半分のデータ幅しかない場合には、2回の出力で入力データ1回分のデータを処理することになります。

この入出力のビット数の設定は、入力は自由に決めれますが、出力はそれに合わせた選択式になりますので、8bitの入力に対して、出力が6bitなどの半端な値は設定できません。

(2) First-Word Fall-Through

FIFOに入力された始めの1word目が出力にどのタイミングで反映されるかを変更出来る機能です。

基本的には、FIFOに入力されたデータはRead信号を入力することで出力信号に反映されます。この機能を持った構成を使うと、FIFOに入力された時点で出力信号に反映され、Read信号を入力すると2word目のデータが出力されるようになります。

出力信号とRead信号の数が一つずれると思って下さい。

(3) Uses Built-in FIFO primitives

この機能はFIFO専用のブロックを持っているFPGAだけ使用可能です。

通常のFIFOはFPGA内に存在するBlock RAMを使用しますが、この機能はBlock RAMではなくBuilt-in FIFOという機能ブロックを使用します。

消費するリソースは Block RAM と同じですが、幾つかの機能を削ることで Block RAM に付随していたロジックを使用せずに、専用機能を使って FIFOを構成します。当然のことながらデバイスが Built-in FIFO に対応している必要があります。

Block RAMを使うか、Build-in FIFOを使うかで、他の機能に制限が出る場合があります。

例として上げているスクリーンショットはXC7Z020デバイスを使用デバイスにプロジェクトを作ってあります。この場合だと、Build-in FIFOでは(1)のNon-symmetric aspect ratiosが使用出来ません。使える機能、効率的に実装出来るFIFO容量は、デバイスの種類によって異なります。

(4) ECC support

ECCをサポートしているかどうかです。

ECC とは Error-correcting code の略で、エラー検知コードのことです。これはパソコンのメモリにも採用されている技術で、データにエラー検知コードを追加して伝送することで、万が一、データが破損した場合に、破損していることを検知出来るという仕組みです。

高い信頼性が必要な装置を作る場合には有効ですが、FIFOの後に検知する回路や、訂正なり破棄なりする回路が必要になりますので、ロジックが肥大化してしまう弊害があります。

(5)Dynamic Error Injection

テスト用の機能です。故意にデータエラーを発生させます。

ECCとセットになる機能で、ECCでエラーが発生したという状況で後段の回路が正しく動作するか検証するために使用します。

テスト用の機能ですからデバック時には使用しても、製品時にはエラーが発生しないように回路を無効にしなければいけません。エラー発生自体はIPへの入力信号で制御出来ますので、IPを作り直さなくても無効にすることが可能です。

Memory Type

(3)のBuilt-in FIFOの説明でも少しだけ触れましたが、FPGA内のどこの機能ブロックを使用するかを指定します。

一番使用頻度が高いのはBlock RAMです。多くのFPGAに搭載されています。

次にDistributed RAM。これは直訳すると分散RAMとなりますが、Block RAM のような大きなブロックではなく LUT 内のRAMを使用します。

通常はLUTはロジックをアサインして使用します。ですが、Block RAMの数が足りなくなったり、FIFOの容量が小さすぎてBlock RAMにアサインするのは勿体ない時に使用します。当然、その分はロジックで使えるLUTが減りますので、FPGAの容量を考えながら使用することになります。

Shift Register は読んでそのまま、シフトレジスタです。

これも Distributed RAM と同じくLUTに実装されます。

ロジックでシフトレジスタを書くのが面倒だったり、シフトする段数を変更しながら試したい場合に使用します。

最後のBuilt-in FIFOは(3)で説明した通り、FIFO専用のブロックを使用します。

やっとBasicのタブの説明が終わりました。

この後は、他のタブに移動して詳細の設定を行いますが、FIFO Implementation で選んだ構成によって、タブの数も中身も異なります。

基本的には、FIFO Implementation Options にある機能を含めて、機能のOn/Offの設定を行うものです。

全てを説明すると記事が非常に長くなってしまいますので、残りのタブについては後日、別の記事に改めたいと思います。

ちなみに、Xilinxの正規の資料は、FIFO Generator の Documentation から Product Guide を選択すると見れます。Xilinxのホームページに飛んでpdfで表示されます。

表示されるのは英語資料ですが、日本語版もXilinxのホームページのどこかにあります。FIFO Generator なら PG057 という資料が表示されますので、PG057 で検索すると見つかると思います。

ただし日本語資料はバージョンが古かったりしますので、ご注意下さい。

--------------------------------------------------------------------------

続きの記事です。

この記事が気に入ったらサポートをしてみませんか?