応用情報処理勉強中(2023春)Day5

2023/4/16受験の皆様 一緒に頑張りましょう!

本記事時間かけたくなく雑記な点ご了承ください。

筆者について

・2022年11月に基本情報に合格(点数ギリギリです)

・勢いで応用情報に申し込んだはいいものの、1か月手をつけていない

・アウトプットが大切と聞いたため取り急ぎ(サボってたらご指摘ください;)

詳細

内容:過去問道場 令和4年春期、令和3年秋期、令和3年春期 テクノロジ

60問

所要時間:3h

※解説図はなるべく載せません。

不明点

問題1

1件のデータを処理する際に,読取りには40ミリ秒,CPU処理には30ミリ秒,書込みには50ミリ秒掛かるプログラムがある。このプログラムで,n件目の書込みと並行してn+1件目のCPU処理とn+2件目の読取りを実行すると,1分当たりの最大データ処理件数は幾つか。ここで,OSのオーバヘッドは考慮しないものとする。

A.500 B.666 C.750 D.1,200

回答

D.1200

解説

3件目以降書き込みがボトルネックになるため、

1分間は60秒×1,000ミリ秒=60,000ミリ秒

60,000ミリ秒÷50ミリ秒=1,200件

問題2

プロセッサの高速化技法の一つとして,同時に実行可能な複数の動作を,コンパイルの段階でまとめて一つの複合命令とし,高速化を図る方式はどれか。

A.CISC B.MIMD C.RISC D.VLIW

回答

D.VLIW

解説

VLIW…Very Long Instruction Word

複数の動作を一つにまとめて同時に実行させる処理

CISC…Complex Instruction Set Computer

複雑で多機能な命令背ttおでコンピュータを構成する方法

MIMD…Multiple Instruction Multiple Data

複数の命令とそれに対応するデータを、それぞれが独立している複数のプロセッサに振り分けて並列処理する方式

RISC…Reduced Instruction Set Computer

CPUに与える命令を短く固定長化し、専用の論理回路で高速に実行できるようにした命令セットでコンピュータを構成する設計方法

問題3

リストには,配列で実現する場合とポインタで実現する場合とがある。リストを配列で実現した場合の特徴として,適切なものはどれか。ここで,配列を用いたリストは配列に要素を連続して格納することによってリストを構成し,ポインタを用いたリストは要素と次の要素へのポインタを用いることによってリストを構成するものとする。

ア.リストにある実際の要素数にかかわらず,リストに入れられる要素の最大個数に対応した領域を確保し,実際には使用されない領域が発生する可能性がある。

イ.リストの中間要素を参照するには,リストの先頭から順番に要素をたどっていくことから,要素数に比例した時間が必要となる。

ウ.リストの要素を格納する領域の他に,次の要素を指し示すための領域が別途必要となる。

エ.リストへの挿入位置が分かる場合には,リストにある実際の要素数にかかわらず,要素の挿入を一定時間で行うことができる。

回答

ア.リストにある実際の要素数にかかわらず,リストに入れられる要素の最大個数に対応した領域を確保し,実際には使用されない領域が発生する可能性がある。

解説

配列… □□□□□□□□

リスト…10データ1/35 → 35データ 2/24 → 24データ3/72

問題4

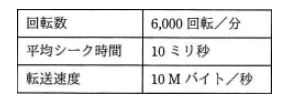

表に示す仕様の磁気ディスク装置において,1,000バイトのデータの読取りに要する平均時間は何ミリ秒か。ここで,コントローラの処理時間は平均シーク時間に含まれるものとする。

ア.15.1 イ.16.0 ウ.20.1 エ.21.0

回答

ア.15.1

解説

磁気ディスクのデータ読み取りに要する時間

データ読取りに要する時間=平均シーク時間+平均回転待ち時間+データ転送時間

・平均回転待ち時間

1分÷6,000回転÷2

=60,000ミリ秒÷6,000回転÷2

=5ミリ秒

・転送速度 10Mバイト/秒において1,000バイトのデータ転送速度は、

1,000バイト÷10Mバイト=0.1ミリ秒

10+5+0.1=15.1ミリ秒

問題5

密結合マルチプロセッサの性能が,1台当たりのプロセッサ性能とプロセッサ数の積に等しくならない要因として,最も適切なものはどれか。

ア.主記憶へのアクセスの競合

イ.通信回線を介したプロセッサ間通信

ウ.プロセッサのディスパッチ処理

エ.割込み処理

回答

ア.主記憶へのアクセスの競合

解説

密結合マルチプロセッサシステム…

複数のCPUが1つの主記憶を共有

単一のOSで制御されるマルチプロセッサシステム

一つのメモリにアクセスすると、競合する

問題6

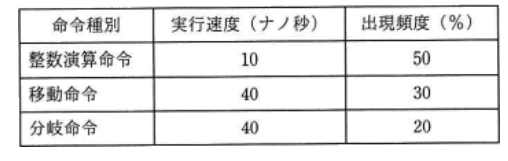

表に示す命令ミックスによるコンピュータの処理性能は,何MIPSか。

ア.11 イ.25 ウ.40 エ.90

回答

ウ.40

解説

10×0.5+40×0.3+40×0.2

=5+12+8=25ナノ秒

1秒÷25ナノ秒=40,000,000回

40,000,000回÷1,000,000回=40MIPS

問題7

メモリインタリーブの説明として,適切なものはどれか。

ア.主記憶と外部記憶を一元的にアドレス付けし,主記憶の物理容量を超えるメモリ空間を提供する。

イ.主記憶と磁気ディスク装置との間にバッファメモリを置いて,双方のアクセス速度の差を補う。

ウ.主記憶と入出力装置との間でCPUとは独立にデータ転送を行う。

エ.主記憶を複数のバンクに分けて,CPUからのアクセス要求を並列的に処理できるようにする。

回答

エ.主記憶を複数のバンクに分けて,CPUからのアクセス要求を並列的に処理できるようにする。

解説

メモリインタリープ…メモリアクセス高速化のための手法

物理的に一つの主記憶を同時アクセス可能な複数の論理的な領域(バンク)に分けて、並列アクセスすることで見かけ上のアクセス時間を短縮することができる

問題8

キャッシュメモリのフルアソシエイティブ方式に関する記述として,適切なものはどれか

ア.キャッシュメモリの各ブロックに主記憶のセットが固定されている。

イ.キャッシュメモリの各ブロックに主記憶のブロックが固定されている。

ウ.主記憶の特定の1ブロックに専用のキャッシュメモリが割り当てられる。

エ.任意のキャッシュメモリのブロックを主記憶のどの部分にも割り当てられる。

回答

エ.任意のキャッシュメモリのブロックを主記憶のどの部分にも割り当てられる。

解説

主記憶上の格納位置とキャッシュメモリ上の格納位置の対応させるかを決める方式

ダイレクトマップ…ハッシュ演算などにより、主記憶のブロック番号からキャッシュメモリのブロック番号が一意に定まる方法

主記憶ブロック:キャッシュメモリブロック=1:1

フルアソシエイティブ…主記憶ブロックをキャッシュメモリ上のどのブロックにも格納することができる方式(空いてる場所に格納する)

セットアソシエイティブ…キャッシュメモリのブロックを連続した一定数ごとにまとめたセットを用意し、主記憶のブロック番号から対応するセットが一意に定まり、そのセット内のブロックならどこでも格納できる方式(分割フルアソシエイティブ的な)

所感

普通に出来悪いです。解説見るので時間かかってます。

この記事が気に入ったらサポートをしてみませんか?