OpenMPW Walkthrough: 2 セットアップとサンプルの動作確認

Caravel をセットアップして,同梱されているサンプルを動かすところまでを試します.

1.Caravel の取得

Caravel は githubから取得できます.git clone してもいいですが,自分アカウントにリポジトリを作成しましょう.どうせあとで github にリポジトリは作ることになりますので,最初から作る方がよいです.

Quick Start に従って,リポジトリを生成します.caravel_user_project をテンプレートとしたリポジトリの生成画面がでてきます.(要 githubアカウント)

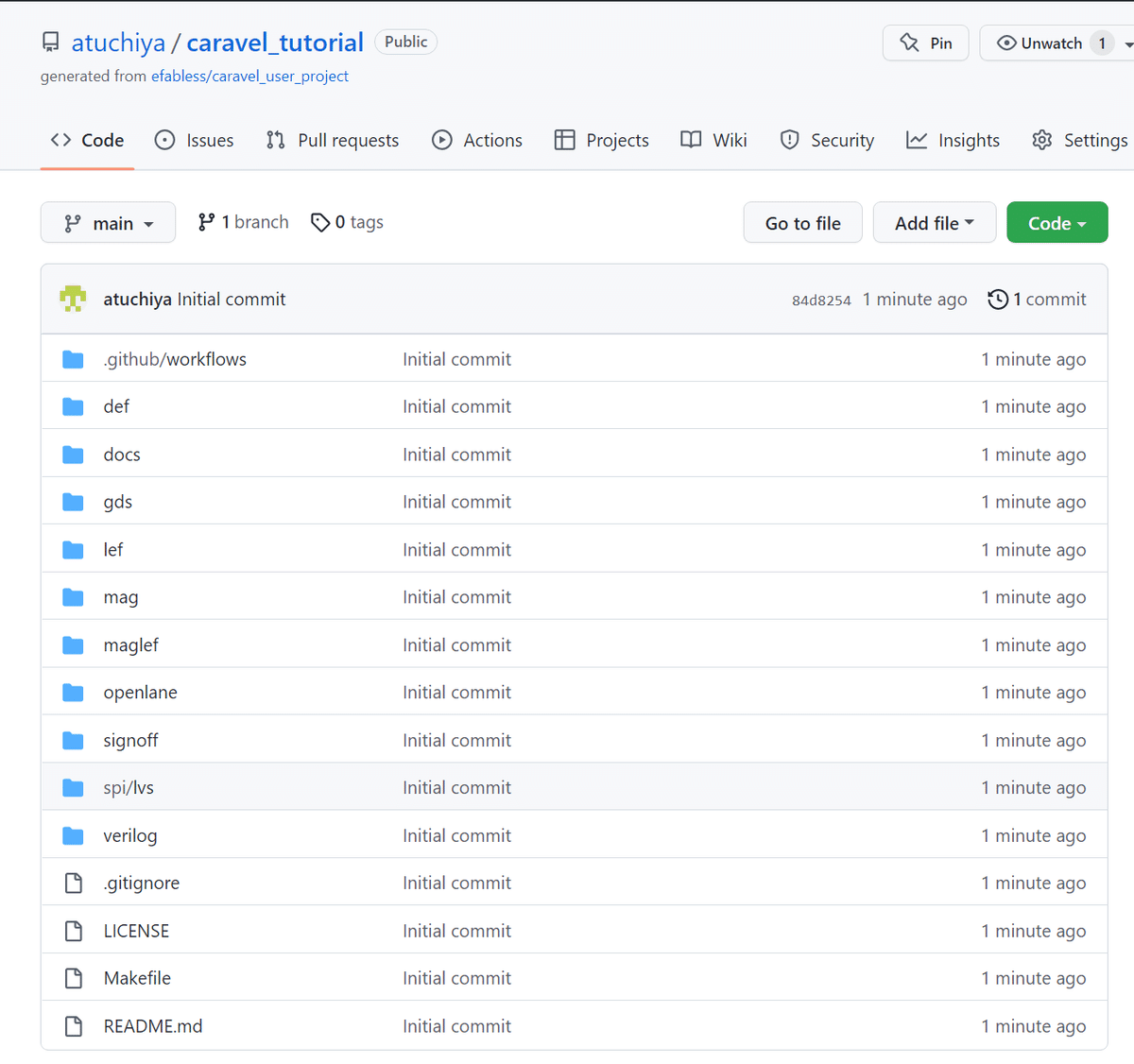

Owner のところの atuchiya は筆者のアカウントですので,ここはあなたの githubアカウントになります.リポジトリの名前は好きなものをつけましょう.ここでは caravel_tutorial にします.生成すると,以下のように自分のアカウントの下にリポジトリができます.

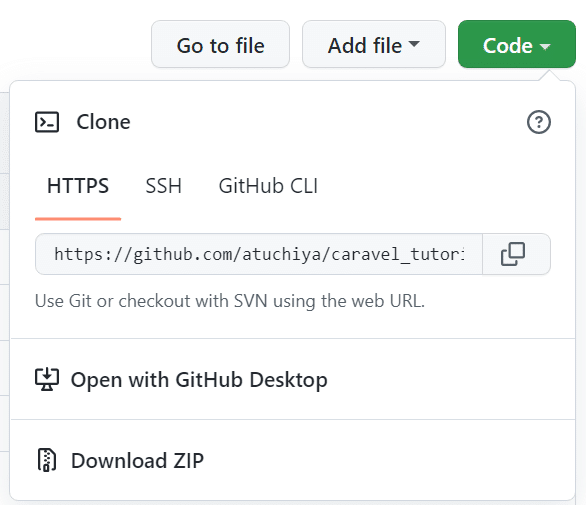

これをローカルに clone します.緑色の Code ボタンを押すと URL が表示されますので,これを clone します.

コマンドは git clone <URL> です.実行すると下のように clone され,ローカルにリポジトリの内容のコピーができます.

caravel_tutorial の中身はこんな感じ.あたりまえですが,リポジトリと同じです.

2.Caravel のセットアップ

Caravel のセットアップをします.このセットアップの手順はよく更新されており,実行するコマンドが過去のものと違っていたりします.(セットアップのコマンドは make setup ですが,かつては make install だったような.)

ということで,Quick Start をちゃんと読みましょう.

まず準備として,openlane と pdk を置く場所を作成し,環境変数でディレクトリを指定します.

mkdir dependencies

export OPENLANE_ROOT=$(pwd)/dependencies/openlane_src

export PDK_ROOT=$(pwd)/dependencies/pdks

export PDK=sky130B

追加の設定として,ロケールと言語を C.UTF-8 にしないとエラーになることがあります.ですので,LC_ALL と LANG も設定しておきましょう.

export LC_ALL=C.UTF-8

export LANG=C.UTF-8

このあたりの環境変数は毎回設定する必要があって面倒なので,シェルの起動スクリプトとかに書いておいてもいいと思います.

また,デフォルトでは Caravel は簡易版の Caravel_lite がインストールされます.フルバージョンをインストールするには,CARAVEL_LITE を 0 にしておきます.Liteバージョンとフルバージョンの違いは… どこに書いてあるんだろう.少なくともサンプルを動かすのは Lite でもできます.

# Lite ではなくフルバージョンをインストールする場合

export CARAVEL_LITE=0

設定したら,リポジトリのトップディレクトリ (ここでは caravel_tutorial の直下) で make setup を実行します.ネットワークやPCのスペックによりますが,だいたい5分ぐらいで終わります.下のように,"Successfully installed" "PDK … enabled" "Leaving directory …" となっていたら成功です.何らかのエラーがでた場合はがんばって対処しましょう.

3.同梱サンプルによる設計フローの確認

caravel_user_project にはサンプル (user_proj_example) が同梱されているので,それを使ってテープアウト直前までの設計フローを試してみます.

3.1 ユーザー設計部分の合成

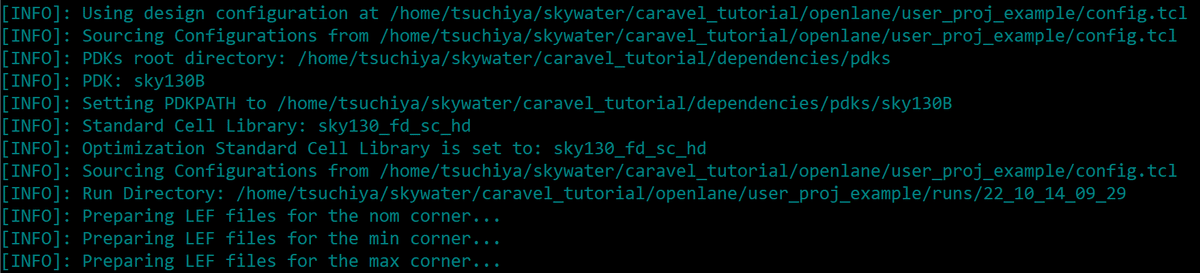

ユーザによる設計 (user_proj_example) から GDS を生成します.ひとまず user_proj_example の中身は気にしないことにして,トップディレクトリ (caravel_tutotial の下) で make user_proj_example を実行します.下図のような感じで始まります.

ステップ数は40個あるので,相応に時間がかかります.のんびり待ちましょう.集積回路の設計フローを知っている人はそれぞれのステップでどういうことをやっているか分かると思います.これだけの処理・検証がコマンド一発で終わるなんて素晴しいですね.

[STEP 1]

[INFO]: Running Synthesis...

[STEP 2]

[INFO]: Running Single-Corner Static Timing Analysis...

[STEP 3]

[INFO]: Running Initial Floorplanning...

[INFO]: Extracting core dimensions...

[INFO]: Set CORE_WIDTH to 888.72, CORE_HEIGHT to 576.64.

[STEP 4]

[INFO]: Running IO Placement...

[STEP 5]

[INFO]: Running Tap/Decap Insertion...

[INFO]: Power planning with power {vccd1} and ground {vssd1}...

[STEP 6]

[INFO]: Generating PDN...

[STEP 7]

[INFO]: Running Global Placement...

[STEP 8]

[INFO]: Running Placement Resizer Design Optimizations...

[STEP 9]

[INFO]: Writing Verilog...

[STEP 10]

[INFO]: Running Detailed Placement...

[STEP 11]

[INFO]: Running Clock Tree Synthesis...

[STEP 12]

[INFO]: Writing Verilog...

[STEP 13]

[INFO]: Running Placement Resizer Timing Optimizations...

[STEP 14]

[INFO]: Writing Verilog...

[INFO]: Routing...

[STEP 15]

[INFO]: Running Global Routing Resizer Timing Optimizations...

[STEP 16]

[INFO]: Writing Verilog...

[STEP 17]

[INFO]: Running Diode Insertion...

[STEP 18]

[INFO]: Running Detailed Placement...

[STEP 19]

[INFO]: Writing Verilog...

[STEP 20]

[INFO]: Running Fill Insertion...

[STEP 21]

[INFO]: Running Global Routing...

[STEP 22]

[INFO]: Writing Verilog...

[STEP 23]

[INFO]: Running Detailed Routing...

[INFO]: No DRC violations after detailed routing.

[STEP 24]

[INFO]: Writing Verilog...

[INFO]: Running parasitics-based static timing analysis...

[STEP 25]

[INFO]: Running SPEF Extraction at the min process corner...

[STEP 26]

[INFO]: Running Multi-Corner Static Timing Analysis at the min process corner...

[STEP 27]

[INFO]: Running SPEF Extraction at the max process corner...

[STEP 28]

[INFO]: Running Multi-Corner Static Timing Analysis at the max process corner...

[STEP 29]

[INFO]: Running SPEF Extraction at the nom process corner...

[STEP 30]

[INFO]: Running Single-Corner Static Timing Analysis at the nom process corner...

[STEP 31]

[INFO]: Running Multi-Corner Static Timing Analysis at the nom process corner...

[STEP 32]

[INFO]: Running Magic to generate various views...

[INFO]: Streaming out GDS-II with Magic...

[INFO]: Generating MAGLEF views...

[STEP 33]

[INFO]: Streaming out GDS-II with Klayout...

[STEP 34]

[INFO]: Running XOR on the layouts using Klayout...

[STEP 35]

[INFO]: Running Magic Spice Export from LEF...

[STEP 36]

[INFO]: Writing Powered Verilog...

[STEP 37]

[INFO]: Writing Verilog...

[STEP 38]

[INFO]: Running LEF LVS...

[STEP 39]

[INFO]: Running Magic DRC...

[INFO]: Converting Magic DRC Violations to Magic Readable Format...

[INFO]: Converting Magic DRC Violations to Klayout XML Database...

[INFO]: No DRC violations after GDS streaming out.

[STEP 40]

[INFO]: Running OpenROAD Antenna Rule Checker...

無事に終わると,下図のように "[SUCCESS]: Flow complete." が出れば完成です.WARNING はいくつか出ますが,問題ありません.これはサンプルなので ERROR は出ないはずです.エラーがでた場合は,どこでエラーがでたかを確認して対処することになります.

3.2 user_project_wrapper の合成

efabless に提出するデータは,user_project_wrapper でなければなりません.user_proj_example を組み込んだ user_project_wrapper を合成します.と言ってもコマンドは make user_project_wrapper を実行するだけですが.

こちらは32ステップ.基本的にこちらの方が user_proj_example よりも大きいので,やはり時間はそれなりにかかります.

[STEP 1]

[INFO]: Running Synthesis...

[STEP 2]

[INFO]: Running Single-Corner Static Timing Analysis...

[INFO]: Creating a netlist with power/ground pins.

[STEP 3]

[INFO]: Running Initial Floorplanning...

[INFO]: Extracting core dimensions...

[INFO]: Set CORE_WIDTH to 2908.58, CORE_HEIGHT to 3497.92.

[STEP 4]

[INFO]: Running IO Placement...

[INFO]: Applying DEF template. See log: /home/tsuchiya/skywater/caravel_tutorial/openlane/user_project_wrapper/runs/22_10_14_09_37/logs/floorplan/4-apply_def_template.log

[STEP 5]

[INFO]: Performing Manual Macro Placement...

[WARNING]: Skipping Tap/Decap Insertion.

[INFO]: Power planning with power {vccd1 vccd2 vdda1 vdda2} and ground {vssd1 vssd2 vssa1 vssa2}...

[STEP 6]

[INFO]: Generating PDN...

[STEP 7]

[INFO]: Performing Random Global Placement...

[INFO]: Skipping Placement Resizer Design Optimizations.

[STEP 8]

[INFO]: Running Detailed Placement...

[INFO]: Skipping Placement Resizer Timing Optimizations.

[INFO]: Routing...

[STEP 9]

[INFO]: Running Global Routing Resizer Timing Optimizations...

[STEP 10]

[INFO]: Writing Verilog...

[STEP 11]

[INFO]: Running Detailed Placement...

[STEP 12]

[STEP 13]

[INFO]: Running Global Routing...

[STEP 14]

[INFO]: Writing Verilog...

[STEP 15]

[INFO]: Running Detailed Routing...

[INFO]: No DRC violations after detailed routing.

[STEP 16]

[INFO]: Writing Verilog...

[INFO]: Running parasitics-based static timing analysis...

[STEP 17]

[INFO]: Running SPEF Extraction at the min process corner...

[STEP 18]

[INFO]: Running Multi-Corner Static Timing Analysis at the min process corner...

[STEP 19]

[INFO]: Running SPEF Extraction at the max process corner...

[STEP 20]

[INFO]: Running Multi-Corner Static Timing Analysis at the max process corner...

[STEP 21]

[INFO]: Running SPEF Extraction at the nom process corner...

[STEP 22]

[INFO]: Running Single-Corner Static Timing Analysis at the nom process corner...

[STEP 23]

[INFO]: Running Multi-Corner Static Timing Analysis at the nom process corner...

[STEP 24]

[INFO]: Running Magic to generate various views...

[INFO]: Streaming out GDS-II with Magic...

[INFO]: Generating MAGLEF views...

[STEP 25]

[INFO]: Streaming out GDS-II with Klayout...

[STEP 26]

[INFO]: Running XOR on the layouts using Klayout...

[STEP 27]

[INFO]: Running Magic Spice Export from LEF...

[STEP 28]

[INFO]: Writing Powered Verilog...

[STEP 29]

[INFO]: Writing Verilog...

[STEP 30]

[INFO]: Running LEF LVS...

[STEP 31]

[INFO]: Running Magic DRC...

[INFO]: Converting Magic DRC Violations to Magic Readable Format...

[INFO]: Converting Magic DRC Violations to Klayout XML Database...

[INFO]: No DRC violations after GDS streaming out.

[STEP 32]

[INFO]: Running OpenROAD Antenna Rule Checker...

こちらも "[SUCCESS]: Flow complete." が出れば完了.これで efabless に提出するデータが完成しました.

4.precheck

make user_project_wrapper でも各種検証は行なっているんですが,提出前の最終チェックが precheck です.user_project_wrapper は設定によっては OpenMPW に載せられないサイズにできたりするので,これは OpenMPW のシャトルのレギュレーションを満たしているかどうかのチェック,というような位置付けだと思います.テープアウト時にはこの precheck は efabless のサーバ上で実行され,パスする必要があります.

4.1 precheck のローカルへのインストール

毎回 precheck を efabless のサーバ上で実行するのも面倒ですし,efabless側のサーバも大変です.ということでローカルに precheck をインストールして precheck を実行し,パスしたら efabless にアップロードします.

その precheck をローカルで実行するために,ローカルに precheck をインストールします.コマンドは make precheck で,1分もかからずに終わります.

4.2 README の編集

トップディレクトリにある README.md を編集します.一見どうでもいいように見えますが,README がちゃんと編集されているかは precheck でチェックされます.OpenMPW のプロジェクトはすべて公開されるので,きちんとしたドキュメントを書く必要があります.デフォルトの内容が残っていると多少編集しても fail するので,一旦全部消して書き直しましょう.

ちなみに README をそのままで run-precheck すると,下のように precheck が fail します.

{{STEP UPDATE}} Executing Check 3 of 13: Default

The provided 'README.md' is identical to the default 'README.md'

{{README DEFAULT CHECK FAILED}} Project 'README.md' was not modified and is identical to the default 'README.md'

4.3 precheck の実行

precheck をインストールし,README もちゃんと編集したら make run-precheck でprecheck を実行します.チェックは13ステップで,5分ぐらいはかかります.

Executing Check 1 of 13: License

Executing Check 2 of 13: Makefile

Executing Check 3 of 13: Default

Executing Check 4 of 13: Documentation

Executing Check 5 of 13: Consistency

Executing Check 6 of 13: XOR

Executing Check 7 of 13: Magic DRC

Executing Check 8 of 13: Klayout FEOL

Executing Check 9 of 13: Klayout BEOL

Executing Check 10 of 13: Klayout Offgrid

Executing Check 11 of 13: Klayout Metal Minimum Clear Area Density

Executing Check 12 of 13: Klayout Pin Label Purposes Overlapping Drawing

Executing Check 13 of 13: Klayout ZeroArea

晴れて全てパスすると,{{SUCCESS}} All Checks Passed !!! で終了します.通ったら efabless のサイトにアップロードし,そこで precheck を実行,それも通ったらテープアウトです.あとは抽選で当たることを祈りましょう.

5.できあがった GDS を見てみる

ここまでコマンドを打ち込むだけでテープアウト可能な GDS が生成されましたが,どんなものができたのか中身を見てみましょう.

klayout で見ますが,layer property ファイルである pdks/sky130B/libs.tech/klayout/sky130B.lyp を読み込む必要があります.-l オプションで指定します (somewhere のところは適当に読みかえてください).めんどうなので alias とかにするといいです.

klayout -l /somewhere/dependencies/pdks/sky130B/libs.tech/klayout/sky130B.lyp生成された GDS は openlane/[project_name]/runs/[Date]/results/final/gds/ の下にあります.まずは user_proj_example の方を見てみます.

decap,fill,tap を非表示にして拡大すると,下のようにスタセルを使った回路ができているのが分かります.

次に,user_project_wrapper の方を見てみます.

中央付近のオレンジ色の矩形が user_proj_example です.信号線,電源メッシュによって IO とつながっていることが分かります.これが Caravel harness に組み込まれて製造されます.

この記事が気に入ったらサポートをしてみませんか?