Xschem の使い方 その4:回路の階層化

1.回路の階層化

ここまでは1つのスケマティックに回路や電源・信号源,モデル,シミュレーション条件などをすべて保存していました.ただ実際の設計では評価対象の回路は回路だけで1つにまとめ,評価条件である電源・信号源,モデル,シミュレーション条件など (これをテストベンチと呼んだりします) とは分けます.

このとき,ある回路を1つのまとまりとして扱うための仕組みがシンボル (SPICE ではサブサーキット) です.これによって回路の再利用ができますので,設計の効率化ができたり回路図が見やすくなったりします.また,後々レイアウトの検証ででてくるLVSの工程でテストベンチに入っていないネットリストが必要になってきますので,小さな回路であっても回路とテストベンチは分けておくのがよいです.

2.シンボルの作成

2.1 中身の作成

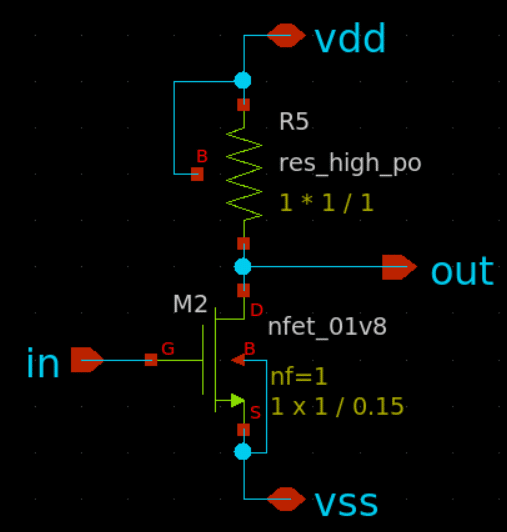

シンボル化する回路として,ソース接地増幅回路を作成します.モデルや電源などは配置せず,回路素子と配線,ピンをつなぎます.できたら保存します.

2.2 シンボルの作成

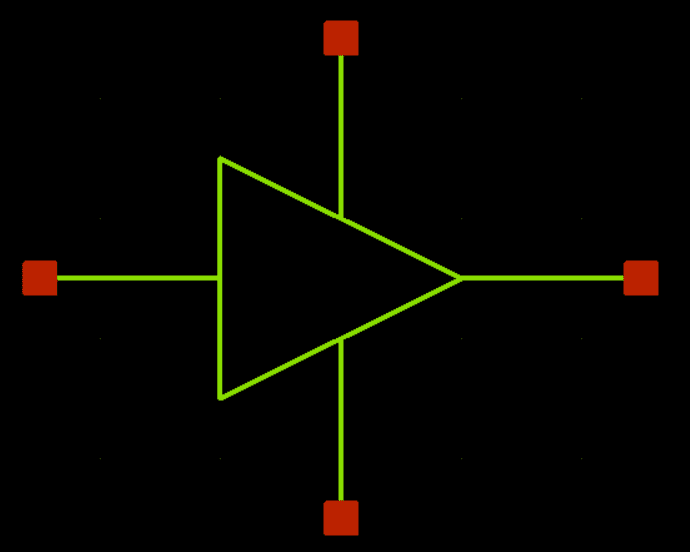

File → New Symbol からシンボルを作成します.シンボルはインスタンスとして置いたときの記号なので,ただの図形です.

まずピンを置きます.Symbol → Place symbol pin です.

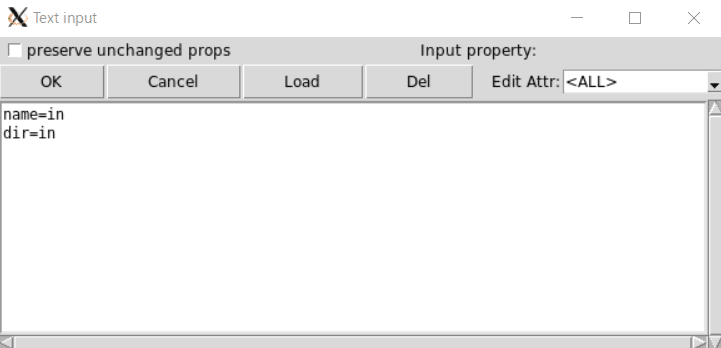

ピンは赤い四角です.適当に配置し,プロパティを開いて名前と種別 (in/out/inout) を設定します.

回路図で配置したピン in,out,vdd,vss を配置し,Insert line で適当に三角形と引き出し線を描きます.

インスタンスとして置いたときに表示される文字を設定します.Insert text で @name というテキストを配置します.これでシンボルとして置いたときに名前が表示されます.

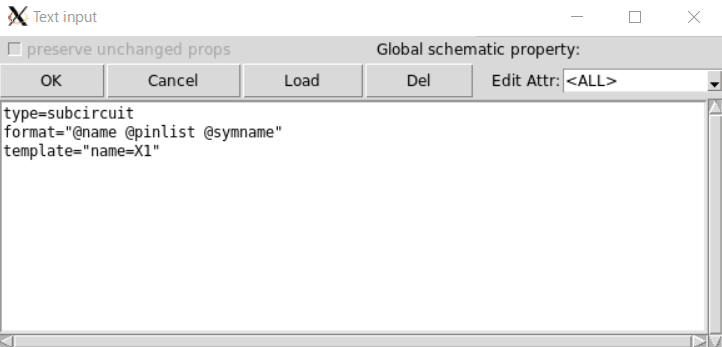

最後にシンボルの設定です.何も選択していない状態でQを押してプロパティを開くと,シンボル全体のプロパティが開きます.ここに,下図のように type,format,template を設定します.

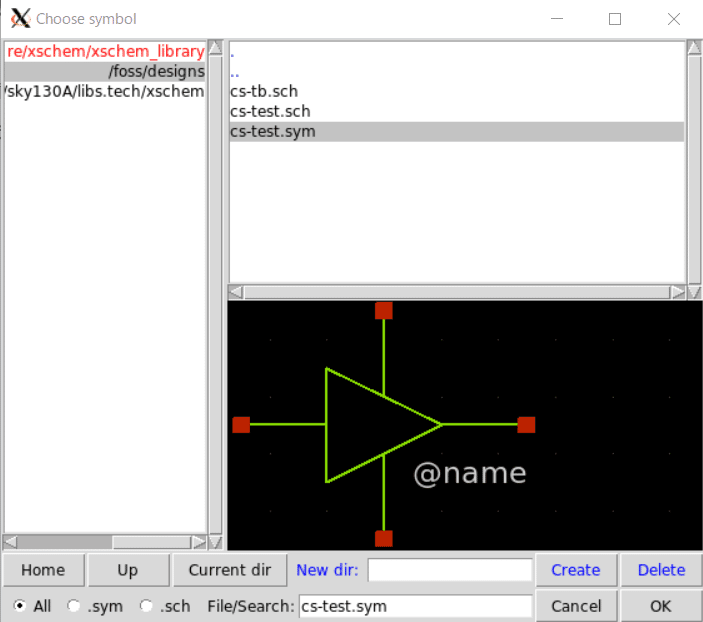

これでシンボルも完成です.シンボルは回路図と共通の名前で保存します.回路図が cs-test.sch ならシンボルは cs-test.sym です.cs-test.sym は自動的に cs-test.sch を回路の中身として読み込もうとしますので,ファイル名を変えてしまうとネットリストの生成時にエラーが出ます.

3.シンボルを使う

作成したシンボルはインスタンスとして使うことができます.新しいスケマティックを開いて,インスタンス挿入画面で先程作成したシンボルを選びます.

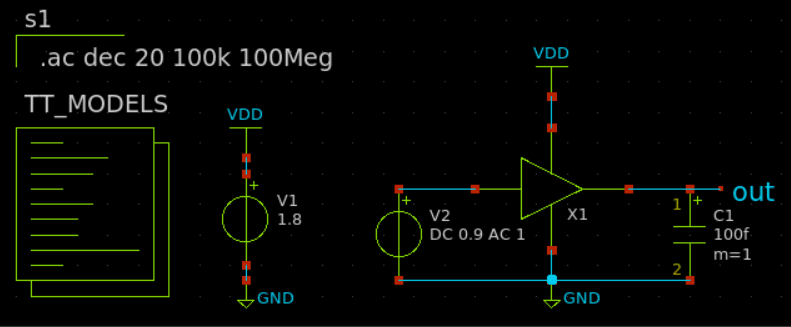

あとは普通に回路を設計します.例えば下図のように電源と信号を接続します.

この回路図のネットリストを書き出すと以下のようになっています.

** sch_path: /foss/designs/cs-tb.sch

**.subckt cs-tb

X1 net1 out VDD GND cs-test

V1 VDD GND 1.8

C1 out GND 100f m=1

V2 net1 GND DC 0.9 AC 1

**** begin user architecture code

** opencircuitdesign pdks install

.lib /foss/pdk/sky130A/libs.tech/ngspice/sky130.lib.spice tt

.ac dec 20 100k 100Meg

**** end user architecture code

**.ends

* expanding symbol: cs-test.sym # of pins=4

** sym_path: /foss/designs/cs-test.sym

** sch_path: /foss/designs/cs-test.sch

.subckt cs-test in out vdd vss

*.ipin in

*.opin out

*.iopin vdd

*.iopin vss

XM2 out in vss vss sky130_fd_pr__nfet_01v8 L=0.15 W=1 nf=1 ad='int((nf+1)/2) * W/nf * 0.29' as='int((nf+2)/2) * W/nf * 0.29'

+ pd='2*int((nf+1)/2) * (W/nf + 0.29)' ps='2*int((nf+2)/2) * (W/nf + 0.29)' nrd='0.29 / W' nrs='0.29 / W'

+ sa=0 sb=0 sd=0 mult=1 m=1

XR5 out vdd vdd sky130_fd_pr__res_high_po W=1 L=1 mult=1 m=1

.ends

.GLOBAL VDD

.GLOBAL GND

.end

.subckt cs-test の中身が,cs-test.sch で作成した回路になっていることを確認してください.もちろん普通にシミュレーションできます.

この記事が気に入ったらサポートをしてみませんか?