レイアウト設計超入門: 番外編 Siliwizでお絵描き

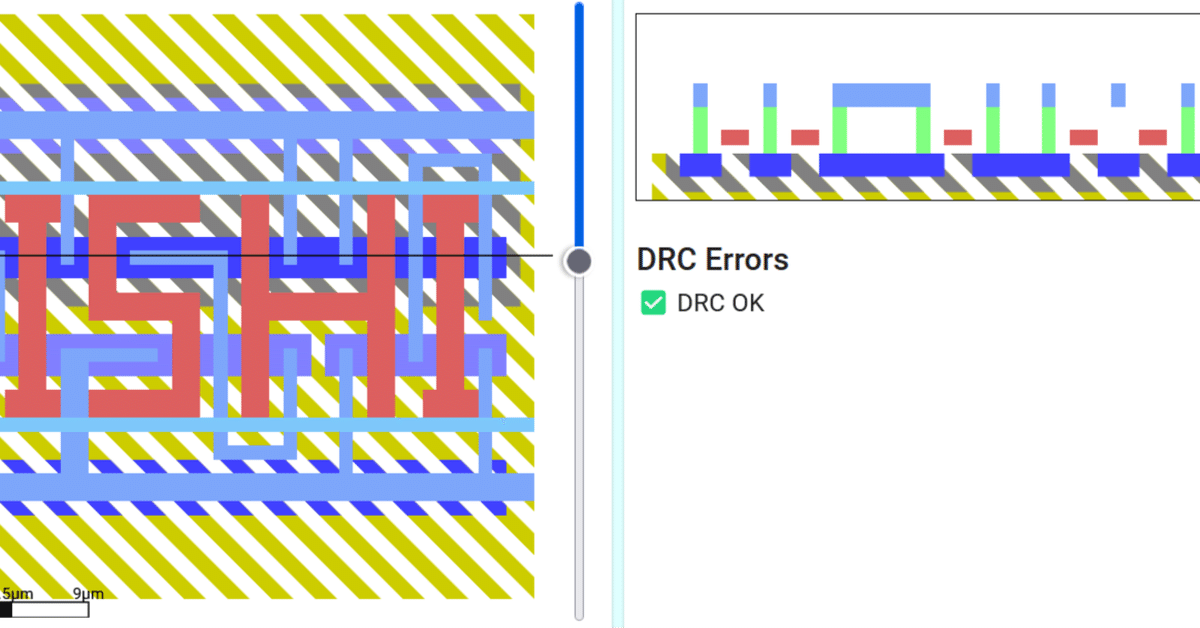

Siliwiz でお絵描きします.

1.ロゴを作ろう

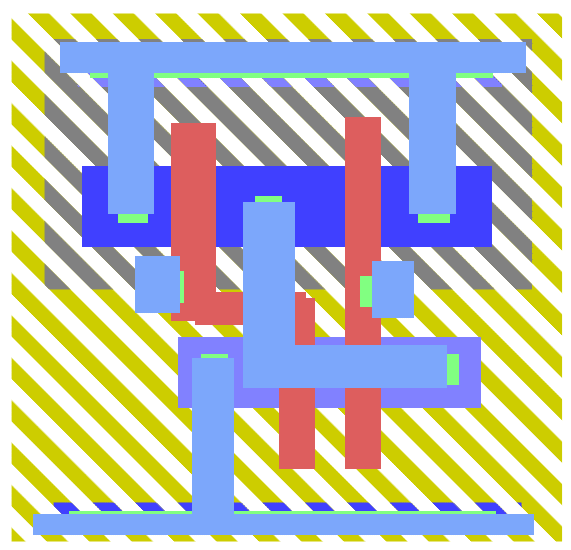

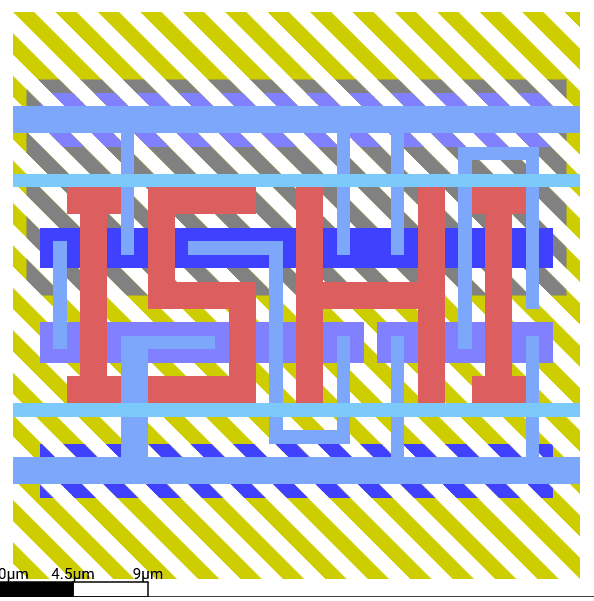

オープンなLSI設計の情報交換をするコミュニティを作ろう,という話があって会の名前どうしよう,という話になりました.チップのこと「石」って言うし石にまつわる何かいいんじゃない,とか言ってたらそのまま「ISHI会」という名前に.Discord で活動してるんですがなんかアイコン作ろうという話になって,適当に Siliwiz で描いたのが採用されたよ,というお話.

2.ISHIを描く

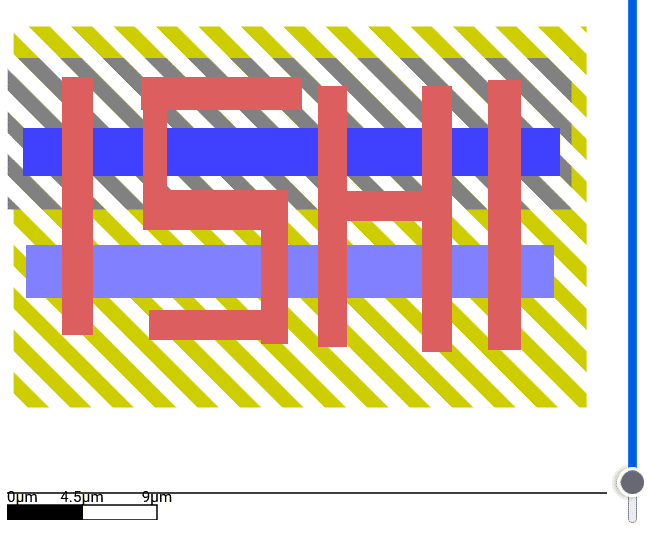

まぁ文字はゲート (polysilicon) ですよね.赤で目立つし.ということで適当に描いてみます.

CMOSっぽくしたいので上半分は PMOS,下半分は NMOS にしよう.p-sub 敷いて,n-well 掘って,p/n-diff 入れて…

せっかくだから何か意味のあるレイアウトにしたいですね.

2.1 NANDゲートを見い出す

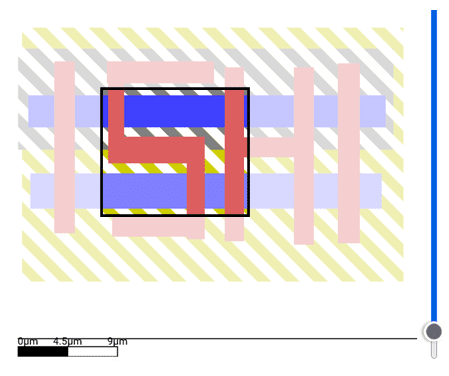

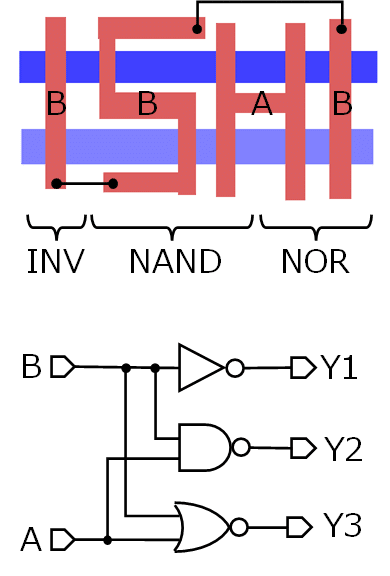

で,じっと眺めていると,ふと気付く.このゲートの形,NANDだな,と.

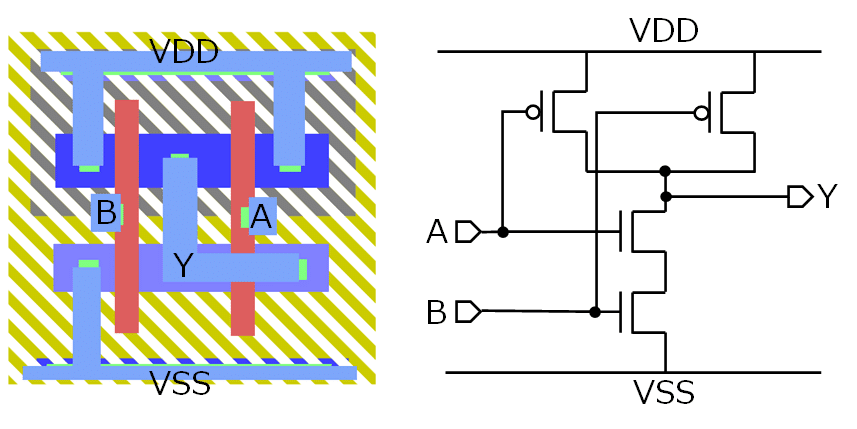

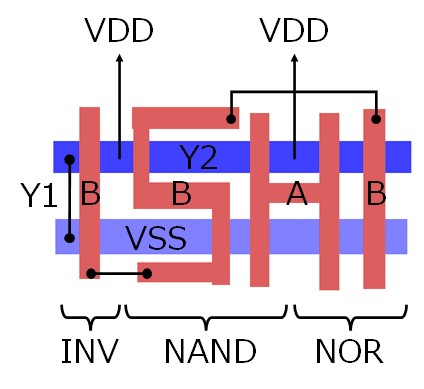

たぶん最近の人は思わないでしょう.最近はこういうゲートの置き方しない (できない) ですから.ちょっと解説すると,素直に NAND ゲートのレイアウトを描くとこんな感じです.2本のゲートがそれぞれ入力A,Bで,NMOSは直列,PMOSは並列に出力Yにつながっています.

さてこのレイアウトは最高の性能を出せるでしょうか? 論理ゲートにおいて工夫すべきは寄生成分 (寄生抵抗,寄生容量) を減らすこと.寄生容量はどこにたくさんつくかというと,diffusion です.p-diff は n-well との間に,n-diff は p-sub との間に空乏層がありますので,これがそのまま寄生容量になります.つまり,diffusion の面積は最小にしたい.ということで,こういうレイアウトにします.

PMOSのゲートに挟まれた真ん中の領域はY端子につなぐためにコンタクトを打つ必要がありますが,NMOSの真ん中の領域は2つの NMOSのドレインとソースが直結されているだけで,コンタクトを打つ必要がありません.ということで,上の図のようにゲートポリを折り曲げて NMOSの真ん中の領域は絞ります.このポリの形がNAND っぽいというわけです.

と,昔(0.35umとか?)のレイアウトを知っている人は思うわけですが,その後製造ばらつきが大きくなり,DFM (Design For Manufacturability) が重視されるようになるとゲートポリの形状は厳しく制限されるようになり,この図のように途中で曲げたり,ゲートポリの間隔が場所によって異なる,というレイアウトが忌避されるようになりました.ということで,最近 (と言っても 100nmぐらいから先) のレイアウトではゲートポリはまっすぐです.

2.2 NANDとくれば

ということで NAND にしよう.他の論理ゲートもあるといいよね.おあつらえむきにNANDの左にゲートが1本,右にゲートが2本並んでいるので左で INV,右で NOR とかよさそう.

いい感じに論理ゲートのトップスリーでぴったりゲートポリを使い切れそう.

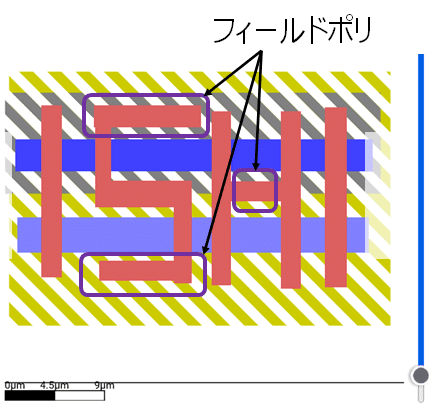

2.3 ポリ配線

あとはゲートポリになっていない部分にも何か意味を持たせたい.下図の横向きになっているポリです.同じ polysilicon レイヤーですが,トランジスタのゲートを構成するポリをゲートポリ,ゲートにならないポリをフィールドポリ,と呼んだりします.これも最近のプロセスではやらない (できない) ですが,かつてはフィールドポリを配線の代わりに積極的に使うことで面積を小さくしていました.

ということでこの部分はフィールドポリとして配線に使っている,ということにしましょう."H" の横棒部分は簡単で,NAND の入力端子と NOR の入力端子をつないでいるということで OK です."S" の下の棒は INV のゲートに,上の棒は NOR の一番右のゲートにつなげばちゃんと回路として成立するのでは.つまりこういうことです.

2.4 つなぎ方を考える

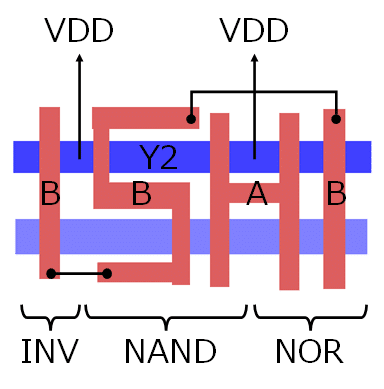

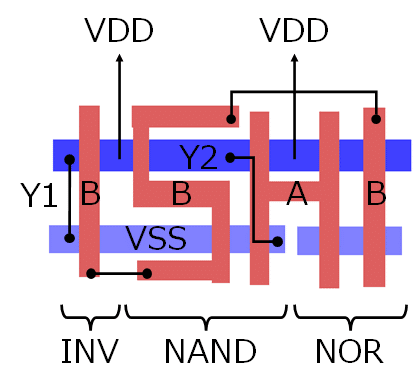

それではつなぎ方を考えていきましょう.これは実は選択肢はなかったりします.まず.NANDのPMOSは両側が VDD,真ん中が出力 Y2 です.

そうするとINVは左側が出力Y1,NMOSの右側が VSSで決まり.

"H" の下側の n-diff を NAND出力 Y2 にしたいところですが,このまま Y2 にすると NOR とつながってしまうので,n-diff を分割します.

NOR は NMOS の両側が VSS,真ん中が出力 Y3 ですから,これですべての端子が確定します.

2.5 うまくつなぐ

ではつないでいきましょう.まずゲートはこういう形にします.INV の入力B と NAND の入力 B はフィールドポリでつなぎました.なんだかポリの形がいびつな気がしますが,これは metal1,metal2 をかぶせて見えなくします.

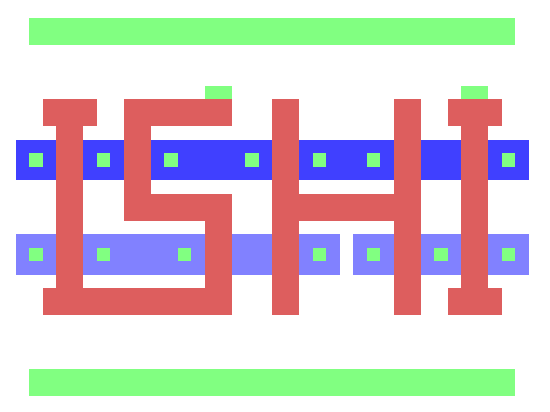

コンタクトはこんな感じ.上下の長いものは p tap,n tap用です."S" の右上と,右側の "I" の上にもコンタクトが打ってあります.

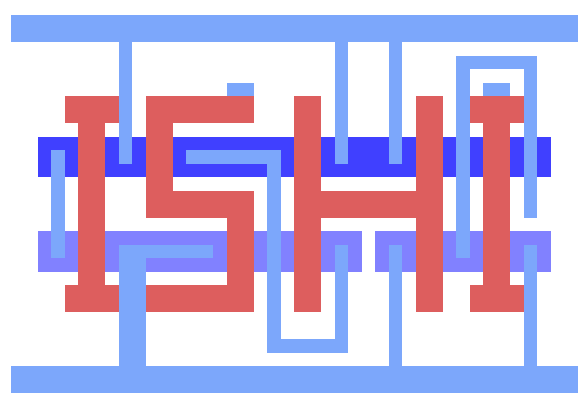

metal1 を置きます.コンタクトの緑色は色数が増えて見た目がうるさくなるので,metal1 を完全に被せて見えなくします.左の "I" と "S" をつないでいた polysilicon は metal1 をかぶせることで切れているように見せています.NAND の出力 Y2 と NOR の出力 Y3 はちょっと遠回りしてつないでいますが,これはデザイン優先です.実際にはゲートポリの上を通って短い距離でつなぎます.

この時点ではまだ "S" と右側の "I" がつながっていません."S" と右側の"I" の間には VDD につなぐための metal1 がすでに走っていますので,metal2 を使ってつなぎます.まず metal2 via を打って

metal2 でつなぎます.デザイン的にバランスを取るために,文字の下にも metal2 を置きました.下側の metal2 はどこにもつながっていません.

これで完成.非表示にしていますが,もちろん p-sub,n-well,p/n tap も配置しています.表示すると見にくいのでロゴでは非表示にしました.

JSONファイルはこちら.ちなみにマウスでは正確に描けないので座標計算して JSON をスクリプトで書き出して作りました.

この記事が気に入ったらサポートをしてみませんか?